現場可編程邏輯閘陣列(FPGA)通常被用於由嵌入式運算到高速串列數位通訊的各類應用。對於可重建硬體和密集型高速邏輯功能來說,FPGA是實現高效能、彈性設計的理想選擇。作為這些高密度架構的一部分,FPGA包含用於頻率合成的內部整數和分數鎖相迴路(PLL)。然而,這種架構也帶來一個簡單的問題:為了最佳化效能和簡化設計,在基於FPGA的設計中如何恰當選擇使用內部PLL、離散式振盪器和時脈IC?

控制平面時脈(Plane Timing)

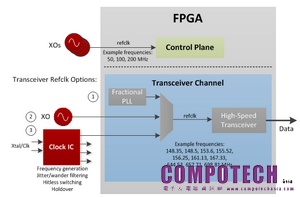

FPGA內部PLL為包括高速邏輯、數位訊號處理和嵌入式記憶體的各種功能模組提供低扭曲時脈來源。內部PLL也被用於產生全區域和局部時脈,以及其他高扇出、低扭曲控制訊號。這些內部PLL需要由外部輸入參考時脈驅動。如圖1所示,簡單的固定頻率振盪器通常被用於提供這些參考時脈。當為FPGA控制平面時脈選擇振盪器時,開發人員應當考慮三個關鍵指標:

FPGA內部PLL為包括高速邏輯、數位訊號處理和嵌入式記憶體的各種功能模組提供低扭曲時脈來源。內部PLL也被用於產生全區域和局部時脈,以及其他高扇出、低扭曲控制訊號。這些內部PLL需要由外部輸入參考時脈驅動。如圖1所示,簡單的固定頻率振盪器通常被用於提供這些參考時脈。當為FPGA控制平面時脈選擇振盪器時,開發人員應當考慮三個關鍵指標:

• 長期可靠性:FPGA通常被用於需要長生命週期的應用,並且重要的是要確保所有電路板層級(board-level)元件都支援長期運行等級。其中振盪器是一個關鍵的考慮因素,因為許多電子應用中基於石英體的元件是形成高返修率的主要原因。晶體很容易遭受由於工作時間和溫度變化而引起的啟動和頻率漂移問題。為了確保長期可靠性,開發人員應當選擇擁有長期運行品質保證的振盪器。合適的振盪器應當至少保證擁有10年的運行壽命,並且詳細標明升溫(例如40°C或更高)條件下的老化效能。

• 電路板層級雜訊抑制:FPGA通常運行在周圍遍佈開關電源的雜訊環境中。此外,FPGA也受到VDD和地平面的雜訊影響。最小化這類雜訊需要付出相對高昂的代價,且不能完全消除。當選擇振盪器時,一個重要的考慮因素就是電源雜訊濾波。具有內部電源電壓調節能力的振盪器提供雜訊抑制能力,透過確保在受到系統層級雜訊時不會超出元件的額定抖動規範,以擁有更多彈性運行能力。

• 可用性:振盪器在生產過程中相當費時費力,這主要是由於與晶體加工、晶圓裝配和包裝相關的密集材料和複雜製造技術。客製化的晶體振盪器甚至可能需要花費更長的時間。為了快速靈活的交付產品應當儘量選擇現有的振盪器產品,或來自代理商的現貨,或來自供應商的快速可程式設計元件。快速取得元件能夠減輕原型設計,加速設計進度。

圖1:需要為控制平面和收發器通道提供外部和內部時脈參考的FPGA設計

收發器時脈

除了可靠性、電源雜訊抑制效能和可用性之外,開發人員應當考慮基於FPGA收發器時脈應用的其它因素。對於高速串列資料通訊(例如10/40/100G乙太網路、光傳輸網路[OTN]、3G-SDI、CPRI和PCI Express)來說,參考時脈的選擇非常重要,因為時脈抖動對收發器的誤碼率產生有害影響。更複雜的是,多速率應用需要一系列不同的參考頻率。如圖1所示,硬體設計人員通常有三種收發器參考時脈可以選擇:

除了可靠性、電源雜訊抑制效能和可用性之外,開發人員應當考慮基於FPGA收發器時脈應用的其它因素。對於高速串列資料通訊(例如10/40/100G乙太網路、光傳輸網路[OTN]、3G-SDI、CPRI和PCI Express)來說,參考時脈的選擇非常重要,因為時脈抖動對收發器的誤碼率產生有害影響。更複雜的是,多速率應用需要一系列不同的參考頻率。如圖1所示,硬體設計人員通常有三種收發器參考時脈可以選擇:

• 內部整數或分數PLL:高效能FPGA包括可用於收發器時脈的內部整數/分數PLL。當運行在整數模式時,這些PLL提供最小抖動。當被用於分數時脈合成時,一些抖動效能受到影響。雖然這種解決方案的抖動在一些應用中是可接受的,但是離散式的振盪器和時脈能夠提供更低的抖動性和最佳化的FPGA收發器效能。

• 振盪器:單頻振盪器可用於固定速率時脈應用。對於多速率收發器來說,可連續程式設計到各種頻率的I2C可程式設計振盪器是更好的解決方案。I2C可程式設計振盪器的一個優勢是他們能夠與FPGA整數PLL搭配。振盪器能夠提供低抖動分數時脈合成,並且FPGA的內部PLL能夠進一步提供整數時脈倍頻和低扭曲時脈路由。

• 時脈產生器/抖動衰減時脈IC:為多FPGA收發器提供時脈的最佳方法是使用多輸出時脈產生器/抖動衰減時脈。頻率靈活的時脈產生器除了提供控制平面時脈之外還能夠被用於時脈收發器。對於需要同步的應用(例如SONET/SDH、同步乙太網路、廣播視頻和CPRI等)來說需要抖動衰減時脈IC。這些元件整合具有低頻寬PLL(通常在0.1Hz-1kHz之間)的超低相位雜訊壓控振盪器(VCO),提供抖動/漂移濾波和超低抖動頻率合成。抖動衰減的時脈也提供無損切換 :一種能夠在切換過程中吸收兩個輸入時脈之間相位差的特性。這最小化了由於時脈重排而導致變頻低頻寬PLL失鎖的風險。最後,抖動衰減時脈提供了參考時脈保持功能,確保收發器在參考時脈失效時維持正常操作。這個關鍵特性對於需要99.999%有效性的通訊應用來說是必不可少的。

總體而言,硬體開發人員應當為他們基於FPGA的應用選擇合適的內部和外部時脈解決方案。相較以往任何時候,現今硬體開發人員擁有更廣泛的時脈選擇(見表1)去最佳化他們接下來的設計。

表1 :推薦用於FPGA應用的Silicon Labs時脈元件

|

元件 |

描述 |

輸出頻率 |

相位抖動 |

|

Si510/11 |

單頻低抖動XO |

0.1 – 250MHz |

0.8ps |

|

Si514 |

I2C程式設計的低抖動XO |

||

|

Si530/31 |

單頻超低抖動XO |

10 – 1417MHz |

0.3ps |

|

Si570 |

I2C程式設計的超低抖動XO |

||

|

Si53306 |

通用時脈緩衝器/電平轉換器,4路輸出 |

1 – 725MHz |

45fs |

|

Si53301 |

通用時脈產生器/電平轉換器,6路輸出 |

||

|

Si53302 |

通用時脈產生器/電平轉換器,10路輸出 |

||

|

Si5335 |

任意頻率、任意輸出時脈產生器,接腳控制 |

1 – 350MHz |

1ps |

|

Si5338 |

任意頻率、任意輸出時脈產生器,I2C控制 |

0.160 – 710MHz |

|

|

Si5317 |

抖動消除器,接腳控制 |

1 – 710MHz |

0.3ps |

|

Si5326 |

任意頻率抖動衰減時脈,I2C/SPI控制 |

0.002 – 1417MHz |

|

|

Si5328 |

10/40/100G同步乙太網路時脈,I2C/SPI控制 |

0.008 – 808MHz |