imec推出NanoIC製程設計套件 首度支援A14邏輯與嵌入式DRAM開發

前言:

全新14埃米(A14)與eDRAM製程設計套件(PDK)的推出加速了邏輯和記憶體微縮技術的研發和創新

2026年2月2日--由比利時微電子研究中心(imec)協調整合的歐洲研究計畫奈米晶片(NanoIC)試驗製程致力於加速2奈米以後的晶片技術創新,今日宣布推出兩套全新製程設計套件(PDK):用於先進邏輯微縮技術的14埃米(A14)路徑探尋PDK及用於先進記憶體創新的嵌入式DRAM(eDRAM)系統探勘PDK。這兩套PDK皆是首創之舉,提供機會率先取得尖端設計規則和流程,並提供使用者研究先進技術節點和嵌入式記憶體設計的獨特管道。

這些NanoIC試驗製程的先進PDK在推進半導體創新方面發揮關鍵作用,讓設計人員在新興技術的硬體問世之前,提早取得實際的設計規則和實作工作流程。NanoIC製程藉由推出A14和eDRAM PDK,率先提供設計人員有關未來運算系統兩大關鍵技術領域的洞見:A14技術節點的邏輯微縮及嵌入式記憶體整合。

透過免費開放這些PDK,NanoIC製程希望能連接早期階段的研究探索與現實世界的整合,幫助研究人員和新創公司探索新興技術節點、預測整合挑戰和參照實際的微縮指標為設計進行基準測試。imec部門處長及NanoIC計畫專案主持人Marie Garcia Bardon說明:「A14和eDRAM等製程設計套件是學習和設計的助力,提供穩健的環境來實務評估和量化比較不同的技術選擇。這套方法實現更快速的學習、減少結構性和設計創新的風險,還能協助設計人員在硬體推出之前,提前籌備先進邏輯節點和嵌入式記憶體技術。」

NanoIC製程研究計畫經理Giuseppe Fiorentino接著表示:「透過推廣這些製程設計套件,我們為大學、業界和新創降低投入新一代技術的門檻。取得實際規則和流程能讓團隊探索全新的研究方向和創新概念,這些探索將會直接為歐洲半導體價值鏈注入動能。」

A14路徑探尋PDK:微縮尺寸到14埃米節點

A14 pathfinding PDK: scaling down to the 14-Angstrom node

作為首批推出的製程設計套件,A14路徑探尋PDK提供用來探索14埃米節點的視覺設計環境,該節點是推進元件尺寸縮小的重大計畫之一。14埃米的一大創新在於引進作為新興微縮加速器的晶背金屬接點。之前的2奈米(N2)製程設計套件運用中段製程矽穿孔封裝(TSVM)的結構來支援晶背供電,14埃米節點進一步發展這項概念,採用更緊湊的直接晶背接點方案來取代TSVM方案。這套新架構直接從晶圓背面建立連接到閘極的電源佈線,還不需要晶圓正面的複雜金屬佈線,成功在相同頻率和單元密度下,達到比2奈米更低的IR壓降、提供18%面積增益和減少7%功耗。

imec率先在該節點推出製程設計套件。該套件包含完整的162-SDC元件庫,並獲得兩大電子設計自動化(EDA)廠商益華電腦(Cadence)、新思科技(Synopsys)的支持。

eDRAM系統探勘PDK:實現嵌入式記憶體的探索

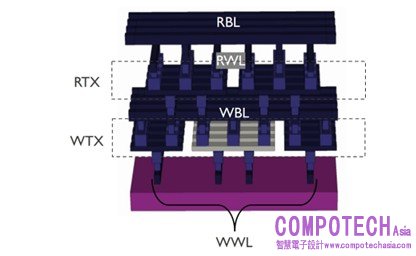

為了提供A14 PDK所推動的邏輯路徑探尋更多助力,NanoIC試驗製程也推出首款eDRAM系統探勘PDK來應對先進系統最大挑戰之一:提供具備高密度及低延遲的內建記憶體。為實現這點,拉近記憶體與處理單元的距離是核心,也是在先進運算架構縮短延遲和改良功率效率的關鍵策略。

目前的eDRAM PDK提供一套探索嵌入式記憶體解決方案的虛擬平台,這些方案填補了高密度但高功耗的外接DRAM與高速但尺寸受限的內建SRAM之間的技術缺口。eDRAM PDK聚焦資料密集和AI運算的系統級表現,設計人員藉此就能評估那些用來縮短高密度記憶體與處理器、圖形處理器(GPU)之間距離的新興記憶體架構和整合策略,減少資料傳輸距離,改良能源效率,以及提升整體系統性能。

展望未來,eDRAM PDK將發展成一套完整的系統探勘平台。這一步發展將能讓設計人員突破虛擬驗證,並分析完整的系統級交互作用。隨著平台趨向成熟,未來的研發階段包含硬體驗證,還有最終在NanoIC試驗製程進行原型設計和投片(tape out)的發展機會。

技術取用與訓練機會

此次推出的兩套PDK,還有之前的N2 PDK,全都可以透過歐洲IC實作平台Europractice取得。為了鼓勵採用和實務探索,NanoIC製程也將在2026年3月25-26日舉行N2與A14 PDA專場研討會,並在2026年5月26日舉行eDRAM PDK專場研討會。這些研討會將提供實務引導、技術見解,還能直接與研發團隊互動。獲取所有技術細節及報名,請造訪NanoIC官網。

本研究部分由奈米晶片試驗製程推動實現。

其採購與運作透過歐盟數位歐洲計畫(Digital Europe,編號101183266)與歐洲展望計畫(Horizon Europe,編號101183277)的晶片聯合承諾(Chips Joint Undertaking)以及會員國比利時(法蘭德斯地區)、法國、德國、芬蘭、愛爾蘭與羅馬尼亞共同資助。了解更多資訊,請造訪nanoic-project.eu。