訊號產生器產生定義的電訊號,其特性會隨著時間的推移而變化。如果這些訊號表現為簡單的週期波形,如正弦波、方波或三角波,那麼這些訊號產生器便稱之為函數產生器,它們通常用於檢查電路或元件的功能。將訊號產生器定義的訊號施加於被測電路的輸入端,並在輸出端連接至相應的量測設備(例如,示波器),如此使用者就可以對電路進行評估。過去,主要的挑戰通常包括如何設計訊號產生器的輸出級。本文將介紹如何設計透過電壓增益放大器(VGA)和電流回饋放大器(CFA)搭建的小型經濟的輸出級。

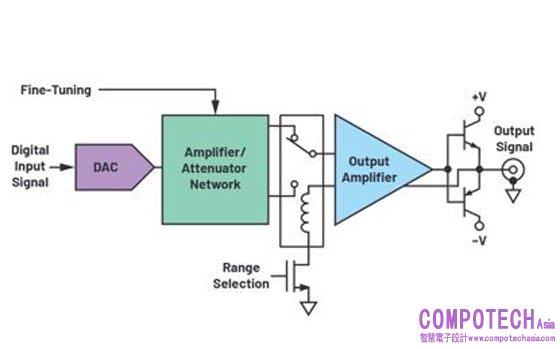

典型的訊號產生器提供25 mV至5 V輸出電壓。為了驅動50 Ω或更高的負載,一般會在輸出端使用功能強大的分立式元件、多個並行元件,或者成本高昂的ASIC。其內部通常具有繼電器,以允許裝置在不同的放大或衰減級之間切換,從而調節輸出電平。根據需要開關繼電器來實現各種增益時,在一定程度上會導致操作斷續。簡化框圖如圖1所示。

圖1.典型的訊號產生器輸出級的簡化框圖

使用新款放大器IC作為輸出級功放,可無需使用內部繼電器而直接驅動負載。因此簡化了訊號產生器的輸出級設計,且進一步降低複雜度和成本。這種輸出的兩個主要元件會構成一個強大的輸出級,提供高速、高壓、高電流,以及具有持續線性微調功能的可變放大器。

圖2.帶VGA的訊號產生器輸出級的簡化框圖

首先,原始輸入訊號必須通過VGA放大或衰減。VGA的輸出訊號可以設置為所需的幅度,這種幅度與輸入訊號無關。例如,如果增益為10時,輸出幅度VOUT為2 V,則VGA的輸出幅度必須調整至0.2 V。遺憾的是,許多VGA因為有限的增益範圍而產生瓶頸。增益範圍很少能大於45 dB。

ADI在低功耗VGA AD8338上實現了0 dB至80 dB可編程增益範圍。因此,在理想條件下,可以將訊號產生器的連續輸出幅度設定在0.5 mV和5 V之間,且無需額外使用繼電器或開關網路。透過去除這些機械元件可以避免不連續的輸出,因為數位類比轉換器(DAC)和直接數位頻率合成器(DDS)元件通常具有差分輸出,所以AD8338提供全差分介面。此外,透過靈活的輸入級,任何不對稱的輸入電流都可以透過內部回饋迴路得到補償。同時,內部節點保持在1.5 V。在正常情況下,最大1.5 V輸入訊號在通過500 Ω輸入電阻時,產成3 mA電流。在輸入幅度較高(例如15 V)時,可能需要在輸入針腳串聯一個更高的電阻。該電阻的阻值也要使得與輸入電壓為1.5V時一樣,產生最大不超過3mA輸入電流。

許多商用訊號產生器在50 Ω(正弦波)負載下提供最大250 mW (24 dBm)的有效輸出功率。但是,這對於具有較高輸出功率的應用通常不夠用,例如測試HF放大器或生成超聲脈衝的要求。因此,還需要使用電流回饋放大器。ADA4870可以在±20 V電源電壓條件下輸出±17 V/1 A。正弦波可以在高達23 MHz的頻率下實現滿負載輸出,這使其成為通用任意波形產生器的理想前端驅動器(輸出級)。為了優化輸出訊號擺幅,因此將ADA4870的增益配置為10,所需的輸入幅度為1.6 V。但是,由於ADA4870具有接地參考輸入,而上游的AD8338具有差分輸出,所以應在兩個部件之間連接差分接收器放大器,以進行差分至到單端的轉換。AD8130提供270 MHz的增益頻寬積(GBWP),壓擺率為1090 V/µs,非常適合此應用。AD8338的輸出限制在±1 V,所以AD8130的中間增益應設計為1.6 V/V。整體電路配置如圖3所示。在22.4 V (39 dBm)幅度和50 Ω負載下,可實現20 MHz頻寬。

圖3.採用分立設計的訊號產生器輸出級的簡化電路

透過更高功率的VGA(AD8338)、大功率的CFA (ADA4870)和差分接收器放大器(AD8130)的組合,可以相對輕鬆地構建精小型高功率訊號產生器輸出級。它具有更高的系統可靠性、更長的服務壽命和更低的成本,因此優於傳統輸出級。

參考文獻

Hunter, David.“兩款新元件重塑訊號產生器。”類比對話,2014年10月。

Hunter, David.“兩款新元件重塑訊號產生器。”類比對話,2014年10月。