線性穩壓器系列文章 1-2：

# 線性穩壓器的電壓輸入至輸出控制——快速入門和優勢

本系列文章由兩部分組成，第一部分介紹電壓輸入至輸出控制 (VIOC) 系統。這種系統通常配置為具有 VIOC 特性的低壓差 (LDO) 穩壓器和降壓拓撲開關穩壓器的組合。隨後，文章針對 VIOC 系統設計提供了具體指導，包括 LDO 和開關穩壓器的建議搭配清單，並說明了搭配的理由。文章最後闡述了如何使用 LDO 的 VIOC 特性來降低 LDO 輸出端的雜訊、優化功耗、在故障期間保護系統，確保系統在啟動和超載等動態條件下正常運行。而系列文章第二部分將在第一部分的基礎上，進一步探討 VIOC 系統設計，並介紹 VIOC 的工作原理和背景。

■作者：Andrew Radosevich / ADI 產品應用資深工程師

Matt Grobelny / ADI 產品行銷經理

## 引言

在電源管理領域，低壓差 (LDO) 穩壓器對確保電子元件獲得高性能電源產生關鍵作用。LDO 的低雜訊性能十分重要，尤其是在精密類比電路、RF 系統和醫療裝置等雜訊敏感型應用中，LDO 可提供純淨的電源，有效降低干擾，增強訊號完整性。LDO 與電壓輸入至輸出控制

(VIOC) 功能及相容的開關穩壓器配合使用時，可形成一個始終維持最佳輸入輸出電壓差的系統。這種設計不僅能顯著降低雜訊，實現高電源電壓抑制比 (PSRR)，還能確保系統高效運行、受到保護且具備強大性能。本文深入探討了實現 VIOC 的複雜細節，並闡述 VIOC 的優勢和實際應用。透過瞭解 VIOC 的協同作用，

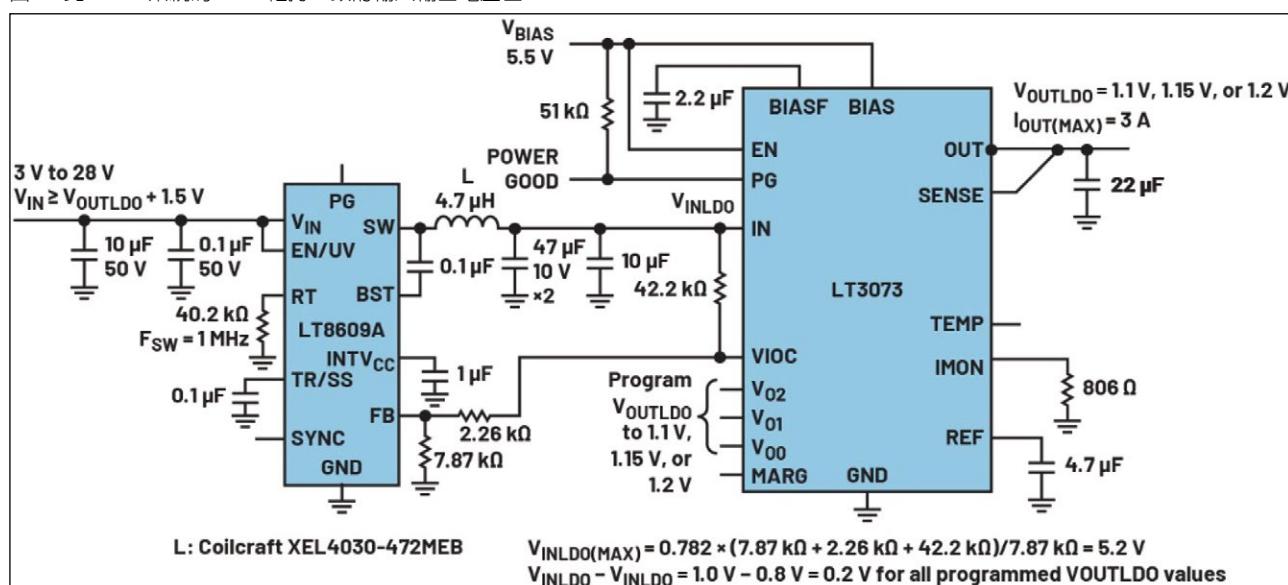

圖 1：此 VIOC 系統為 LDO 維持一致的輸入輸出電壓差

工程師可以優化各種電子裝置的電源管理解決方案。

無論是否具有 VIOC，LDO 都屬於電源管理產品類別。電源管理涉及使用穩壓器或轉換器等積體電路 (IC) 來為放大器、資料轉換器或處理器等電子負載供電。LDO 是電源管理 IC 的一個子類，目的在為電子負載直接供電，主要作用包括：提升負載性能，有效降低負載之間不必要的相互干擾，確保系統中的電源 IC 和負載按正確時序上電和關斷。

具有 VIOC 的 LDO 透過內部電路提供一個外部訊號來控制為 LDO 供電的開關穩壓器的輸出，進而使 LDO 的輸入輸出電壓差保持恆定，如圖 1 所示。線性穩壓器本質上是電晶體電路，能夠以相對較低的雜訊供電，但對輸入輸出電壓差很敏感，效率也由此決定。開關穩壓器透過功率電晶體 (開關) 的快速切換來傳輸能量。開關穩壓器使用功率開關及電感和二極體，高效地將輸入電壓轉換為更適合為 LDO 供電的電壓。

## 使用 VIOC 將降壓轉換器與 LDO 相結合以增強性能

典型的 VIOC 電路採用降壓開關穩壓器來為具有 VIOC 特性的 LDO 供電。由此得到的電路是一種非常強大的配置，兼具降壓穩壓器的高效率特性和 LDO 的低雜訊性能。降壓穩壓器又稱為降壓轉換器，是一種開關轉換器，能夠高效地將輸入轉換為低於輸入電壓的穩定輸出。

創建 VIOC 電路的第一步是選擇 LDO 和開關穩壓器。ADI 提供多種整合 VIOC 功能的 LDO。LT3045-1 和 LT3041 系列及 LT3073、LT3074 和 LT3078 系列均有最新版本的 VIOC 特性。LT3045-1 和 LT3041 線性穩壓器的輸出電流範圍為 500 mA 至 1 A，輸入電壓範圍約為 2 V 至 20 V，只需要一個輸入電源。LT3073、

LT3074 和 LT3078 的輸出電流範圍為 3 A 至 5 A，輸入電壓範圍為 0.6 V 至 5.5 V，需要一個額外的低電流 BIAS 輸入電源。任何具有回饋 (FB) 接腳的開關穩壓器都可以與這些使用 VIOC 的 LDO 組合使用，但在選擇設計所用開關穩壓器之前，請注意以下事項：

- 支援 VIOC 的 LDO 可與任何類型的開關穩壓器拓撲配合使用，但最常與降壓穩壓器配合使用。

- LT3045-1 和 LT3041 LDO 必須與 FB 電壓為 1 V 或更低的開關穩壓器搭配，使得 LDO VIOC 接腳可以在 1 V 電壓下工作 (有關詳細資訊，請參閱產品手冊)。

- 在 VIOC 系統中，具有補償接腳的開關穩壓器相較於沒有補償接腳的開關穩壓器，可能更容易穩定。

- 開關穩壓器和 LDO 評估板可以方便地評估 VIOC 系統硬體的工作。

- 具有 VIOC 功能的 LDO 不能與 Silent Switcher 3 (SS3) 開關穩壓器搭配使用，因為 SS3 穩壓器沒有常規 FB 接腳。

- 相較於典型 VIOC 電路，具有整合高側回饋電阻的 Module 穩壓器無法使 LDO 保持恆定的輸入輸出電壓差。

- 使用 VIOC 的電路需要專用電壓軌作為 LDO 前級，而不是支援多個電壓軌的前級。

- 相較於獨立 LDO 設計，VIOC 需要更多元件。VIOC 電路所需的額外元件包括：為 LDO 供電的開關穩壓器的回饋分壓器中的額外電阻器，以及開關穩壓器輸出通常使用的額外電容。

為了簡化設計過程，ADI 提供指導來說明哪些降壓開關穩壓器最適合搭配帶有 VIOC 特性的特定 LDO 使用。表 1 列出了與具有 VIOC 的推薦 LDO 組合使用的合適開關穩壓器，並

表 1：推薦用於 VIOC 系統的 LDO 和開關穩壓器

| LDO      | LDO 說明                                          | 推薦的開關穩壓器 1 | 推薦的開關穩壓器 2 | 推薦的開關穩壓器 3 |

|----------|-------------------------------------------------|------------|------------|------------|

| LT3041   | 具有 VIOC 控制功能的 20 V、1 A、超低雜訊、超高 PSRR 線性穩壓器       | LT8608     | LTC3307A   | LTC3626    |

| LT3045-1 | 具有 VIOC 控制功能的 20 V、500 mA、超低雜訊、超高 PSRR 線性穩壓器    | LT8608     | LTC3307A   | LTC3626    |

| LT3073   | 3 A、超低雜訊、高 PSRR、45 mV 壓差超快線性穩壓器                 | LT8609A    | LTC3309A   | LTC8640    |

| LT3074   | 具有 PMBus 的 5.5V、3A、超低雜訊、高 PSRR、45mV 壓差<br>線性穩壓器 | LT8609A    | LTC3309A   | LTC8640    |

| LT3078   | 5.5 V、5 A、超低雜訊、高 PSRR、55 mV 壓差、超快<br>線性穩壓器      | LTM4658    | LTC3309A   | LT8642S    |

表 2：表 1 推薦的開關穩壓器的說明

| 用於 VIOC 的<br>開關穩壓器 | 開關穩壓器說明                                                                                   | 回饋接腳<br>電壓 (VFB) | 可編程為脈衝跳略或<br>強制連續模式 | 評估板       | 是否有補<br>償接腳？ | 備註              |

|--------------------|-------------------------------------------------------------------------------------------|------------------|---------------------|-----------|--------------|-----------------|

| LT8608             | 具有 2.5 $\mu$ A 靜態電流的 42 V、<br>1.5 A 同步降壓穩壓器                                               | 0.778 V          | 是                   | DC2458A   | 否            |                 |

| LT8609A            | 具有 2.5 $\mu$ A 靜態電流的 42 V、<br>3 A 同步降壓穩壓器                                                 | 0.782 V          | 是                   | DC2195B-A | 否            |                 |

| LT8640             | 具 2.5 $\mu$ A 靜態電流的 42 V、<br>5 A 同步降壓型 Silent Switcher                                    | 0.97 V           | 是                   | DC2202A   | 否            |                 |

| LT8642S            | 18V、10A 同步降壓型超低雜<br>訊開關穩壓器 2                                                              | 0.597 V          | 是                   | DC2560A   | 是            |                 |

| LTC3307A           | 5V、3A 同步降壓型 Silent<br>Switcher 穩壓器，提供 2 mm<br>x 2 mm LQFN 封裝和 1.6 mm<br>x 1.6 mm WLCSP 封裝 | 0.5 V            | 是                   | DC2990A   | 否            |                 |

| LTC3309A           | 5 V、3 A 同步降壓型<br>Silent Switcher 穩壓器，採用<br>2 mm x 2 mm LQFN 封裝                            | 0.5 V            | 是                   | DC2745A   | 否            |                 |

| LTC3626            | 20 V、2.5 A 同步單晶片降壓<br>穩壓器，具有電流和溫度監測<br>功能                                                 | 0.6 V            | 是                   | DC1768A   | 是            | 無脈衝<br>跳略模<br>式 |

| LTM4658            | 低 VIN、高效率 10A 降壓型<br>DC-DC $\mu$ Module 穩壓器                                               | 0.5 V            | 是                   | DC2861A   | 是            |                 |

提供所有 LDO 的說明。這些搭配基於前面列出的考慮因素，因此在建構由降壓穩壓器和具有 VIOC 特性的 LDO 組成的 VIOC 電路時，請遵循上述文章內容和表 1 提供的指導。表 1 所列 LDO 的產品手冊中並提供了許多 VIOC 電路參考設計。

表 2 則提供了表 1 所列降壓穩壓器的詳細說明。這些資訊有助於設計人員選擇不僅滿足電氣要求，而且符合限制條件（例如開關穩壓器的輸入電壓範圍、負載電流能力和工作電流）的穩壓器。除了推薦用於 VIOC 的開關穩壓器外，

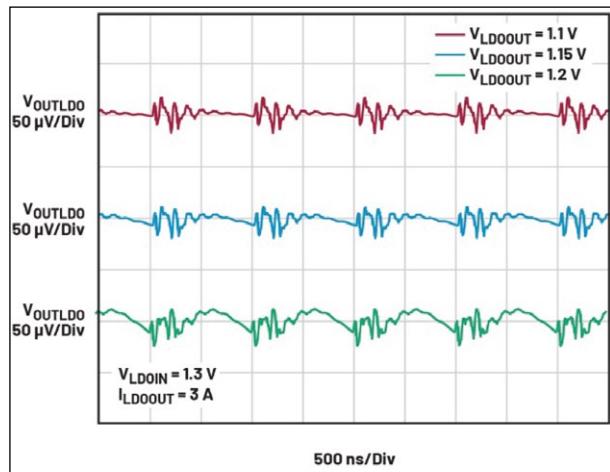

圖 2：這些示波器截圖針對的是圖 3 中的電路，表示隨著 LDO 輸出電壓提高，PSRR 引起的雜訊會加劇

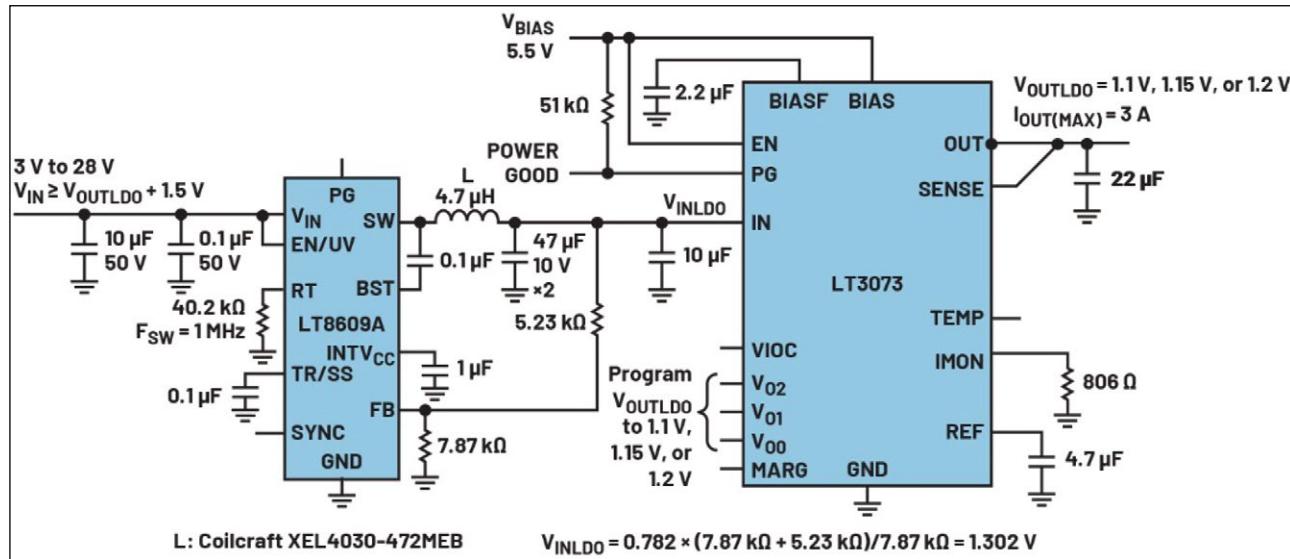

圖 3：此電路不使用 VIOC

表 2 還列出了開關穩壓器的回饋接腳電壓、可用模式、評估板產品型號和補償接腳的可用性。

## VIOC 的雜訊最小化和高 PSRR 優勢

如上所述，當 LDO 與 VIOC 功能及相容的開關穩壓器配合使用時，可形成一個始終維持最佳輸入輸出電壓差的系統，進而不僅顯著降低雜訊，實現高 PSRR，還能提升性能。

有些使用者只是想改變 LDO 的輸出電壓，但不希望採用複雜的方案來調節給 LDO 電源供電的開關穩壓器的輸出電壓。與圖 1 中的電路相反，圖 3 所示的電路沒有 VIOC，因此當調高或調低 LDO 輸出時，開關穩壓器的輸出保持不變。圖 2 顯示，圖 3 電路的 PSRR 性能在 LDO 輸出電壓較高情況下會下降，原因是在 LDO 輸出電壓增加而 LDO 輸入不增加的情況下，開關穩壓器的輸出電壓漣波在 LDO 輸出端引起的雜訊會增加。

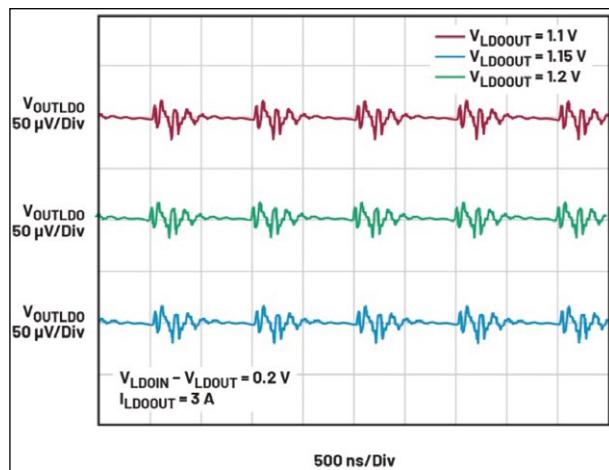

現在考慮一下 VIOC 相較於圖 2 和圖 3 所示例子的優勢。圖 1 電路所示的 VIOC 系統會在 LDO 輸出發生變化時，維持 LDO 的輸入輸出電壓差一致，使基於有效抑制雜訊的 PSRR 保持高水準。開關穩壓器的輸出電壓會在 LDO 輸出

降低時自行調低，在 LDO 輸出提高時自行調高。因此，當 LDO 的輸出電壓變化到三個不同位準時，開關穩壓器的輸出電壓漣波在 LDO 輸出端引起的雜訊依然保持較低水準，如圖 4 所示。

## VIOC 的優勢：提升效率、加強保護和優化運行

除了雜訊最小化、高 PSRR 優勢之外，具有 VIOC 的系統還能始終保持最佳的輸入輸出電壓差，使其工作高效、安全且性能強大。效率方面的優勢是顯而易見的，因為當 LDO 輸出電壓降低而 LDO 輸入電壓保持不變時（如圖 3 電路所示），LDO 的功耗會增加，效率會降低。對於圖 1 中的 VIOC 系統，即使 LDO 輸出發生變化，VIOC 也能使 LDO 保持恆定的輸入輸出電壓差，因此功耗保持不變。

此外，在不使用 VIOC 的系統中，某些情

圖 4：這些示波器截圖針對的是圖 1 中的電路，表示 PSRR 引起的雜訊始終很低，原因是該電路使 LDO 保持恆定的輸入輸出電壓差

況和故障可能會導致 LDO 輸入輸出電壓差增大到不可接受的水準。例如，如果開關穩壓器輸出和 LDO 輸出都被設定為相對較高的電壓，並且 LDO 上存在輸出短路故障，則 LDO 輸入輸出電壓差可能會急劇增大。LDO 上的輸出短路故障

會導致 LDO 兩端的輸入輸出電壓差過高，因為沒有 VIOC 來強制開關穩壓器的輸出電壓降低並維持設定的 LDO 輸入輸出電壓差。當 LDO 輸出短路時，故障期間 LDO 的高輸入輸出電壓差會大幅增加 LDO 的功耗，使得 LDO 溫度可能超過建議工作溫度，進而造成可靠性降低。

當 LDO 輸出短路時，故障期間 LDO 的高輸入輸出電壓差還會阻止 LDO 在短路輸出故障消除後正常恢復，因為許多高壓 LDO 具有一種稱為限流折返的保護特性。

限流折返是電源和穩壓器中使用的一種保護技術，用於在發生過流或短路情況時降低輸出電流。與在故障期間維持恆定電流的簡單限流不同，折返限流會同時降低輸出電壓和電流，進而降低電路元件的功耗。這有助於保護電源和相連元件免於因過熱和過大電流而受損。<sup>1</sup>

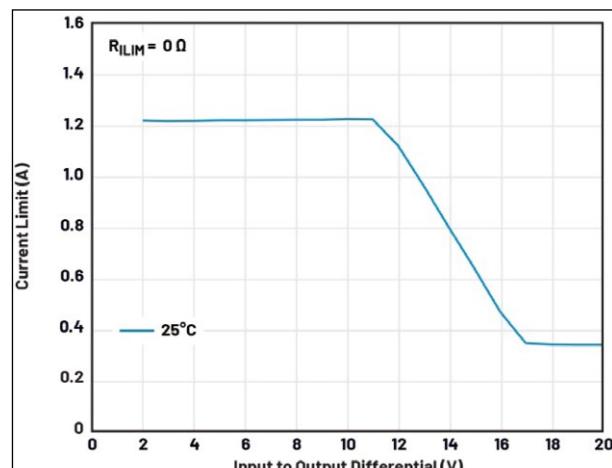

圖 5 顯示了 LT3041 LDO 的典型限流折返。注意在圖 5 中，當輸入輸出電壓差大於 11 V 時，LDO 能夠輸出更小的電流。ADI 的許多 LDO 產品手冊都包含一個名為「超載恢復」的章節，其中解釋了當 LDO 輸出上的短路故障消除後，為什麼限流折返可以阻止輸出電壓設定值和負載相對較高的 LDO 恢復到正確的輸出電壓。

無 VIOC 的電路中的限流折返也會阻止高

圖 5：LT3041 LDO 的典型限流折返

電壓電路正常啓動，因為當電路開啓時，LDO 的輸出電壓最初為 0V，然後逐漸上升至正常運行期間的期望輸出穩定電壓。如果輸入電壓在開啓時相對較高，限流折返可能會過度限制 LDO 電流，並阻止 LDO 輸出電壓上升至期望的穩定電壓。VIOC 自動維持正確的開關穩壓器輸出電壓，進而維持正確的 LDO 輸入輸出電壓差，確保電路在故障和啓動情況下都能正常工作。

## 結語

本系列文章的第一部分在於協助讀者理解如何使用支援 VIOC 的 LDO 與降壓穩壓器的組合（現代應用中最普遍的配置）來針對設計高

效、低雜訊電源系統奠定基礎。本文並探討推薦的 LDO 與開關穩壓器搭配方案及其背後的依據，說明深思熟慮的元件選擇能夠顯著提升系統性能，接著展示如何利用 VIOC 特性降低輸出雜訊、提高熱效率，並增強啓動和超載恢復期間的系統保護和性能。

系列文章的第二部分則將探討這些元件如何保持恆定的輸入輸出電壓差，並介紹可簡化 VIOC 系統實現的實用工具。

## 參考文獻

- <sup>1</sup> T.K.Hareendran , “Foldback Current Limiting - Little Secrets” , Codrey , 2021 年 11 月。

CTA

## 資策會攜手中科院簽署合作備忘錄 打造國防可信任生態系

為深化我國人工智慧與資通安全關鍵技術研發能量，財團法人資訊工業策進會（資策會）與國家中山科學研究院（中科院）正式簽署合作備忘錄，雙方將聚焦資策會 AI 應用、系統整合與場域驗證的實務經驗，結合中科院在國防自主武器系統研發、航太與無人載具技術、資通安全與國防資安等領域深厚能量，共同打造兼具創新與國家戰略價值的技術研發平台，提升產業競爭力與防衛韌性。

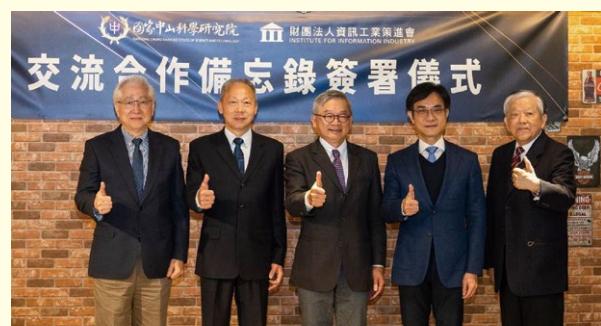

本次簽署儀式由中科院李世強院長與資策會黃仲銘董事長共同簽署，並邀請國家科學及技術委員會主委吳誠文、工業技術研究院董事長吳政忠見證，展現政府、研究機構與產業界對本次合作的高度重視與支持。

資策會與中科院將聚焦資通訊軟體開發、視覺辨識與影像處理、人工智慧治理與評測、資安場域與安全鑑測、泰德 TAIDE (Trustworthy AI Dialogue Engine，可信任生成式 AI 對話引擎) 精進與知識蒸餾、人工智慧技術深耕與認證等六大合作範疇，期待透過雙方合作，能提升資通系統韌性與軟體工程品質，推動安全、可信且可擴展的系統架構。此外，雙方亦結合 AI 演算法與實際場域應用，建立可信、透明、可評測之 AI 治理與驗證機制，回應國際 AI 法規與倫理趨勢，並深化國防產業人工智慧人才培育與技術基礎。

資策會強調，推動人工智慧與資通安全發展，核心目的在於回應社會公共需求，以行動支持國家數位發展策略，透過與中科院合作，將科研能量轉化為可落地、可驗證的系統與服務，強化國防與關鍵基礎設施安全，降低資安風險對社會造成的衝擊，資策會與民興利，促進產業與人才體系健全發展，共同為臺灣打造一個更具韌性、更安全的數位未來。

圖說：資策會與中科院為強化 AI 應用與關鍵技術研發，打造國防可信任生態系，正式合作。圖左起為工業技術研究院董事長吳政忠、中科院院長李世強、國家科學及技術委員會主委吳誠文、資策會董事長黃仲銘、台灣無人機產業技術整合協會理事長高志明共同合影。