## 應用筆記

# 優化 AD9081 及 AD9082 的射頻性能 (II)

■文：ADI

## AD9081 和 AD9082 ADC 模型

AD9081 包含四個 12 位元、4 GSPS 速率 ADC 核心，而 AD9082 包含兩個 12 位、6 GSPS 核心。由於如此差異，此兩款 ADC 具有不同的輸入阻抗和模型。

## ADC S 參數分析

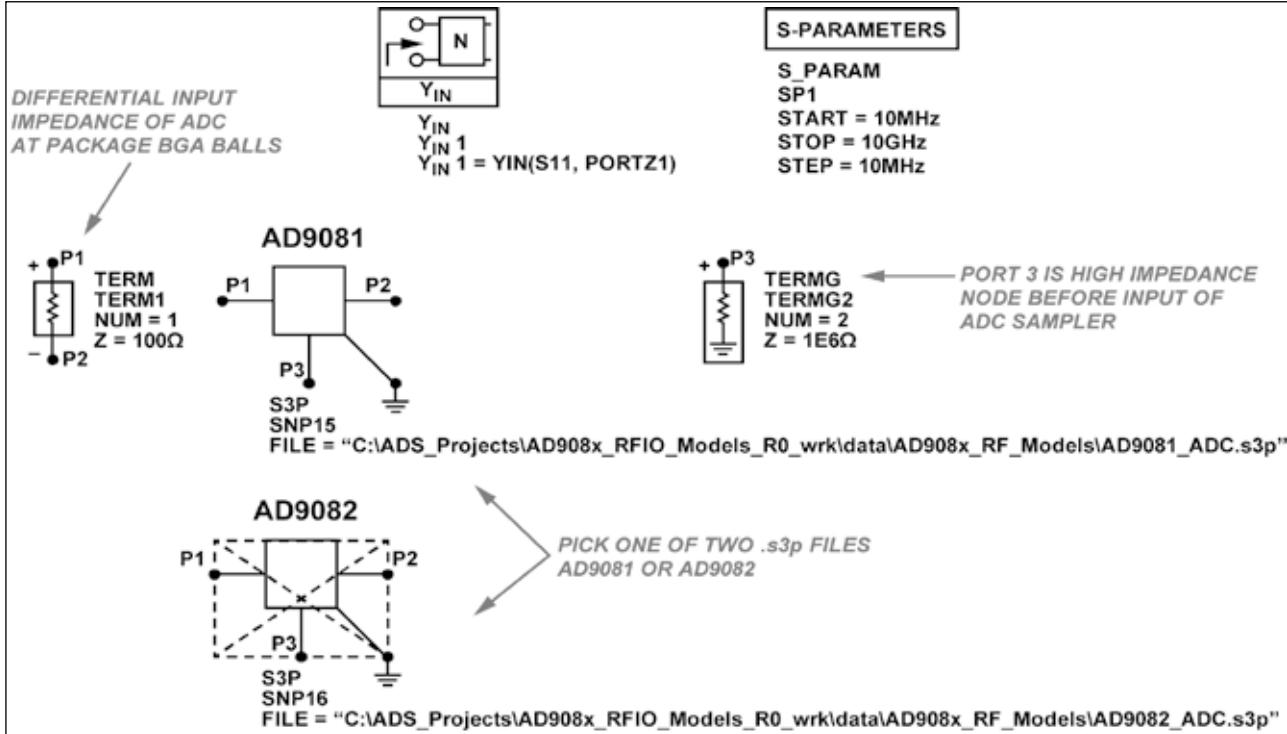

ADS 檔案中的 ADC\_S-parameter\_Analysis 原理圖（參見圖 31）可用於查看封裝 BGA 接腳處 AD9081 和 AD9082 的 ADC 輸入阻抗。透過啟能或禁用兩個 .s3p 檔中的一個，用戶可以選擇 AD9081 或 AD9082 ADC。.s3p 檔的埠 3 是 ADC 採樣器輸入端的高阻抗節點；因此，對於 S 參數分析，該埠以高阻抗端接。

對於非 ADS 用戶，AD9081/2\_RF\_Models.zip 檔中包含同樣的 .s3p 檔，任何電路模擬器都可以使用。

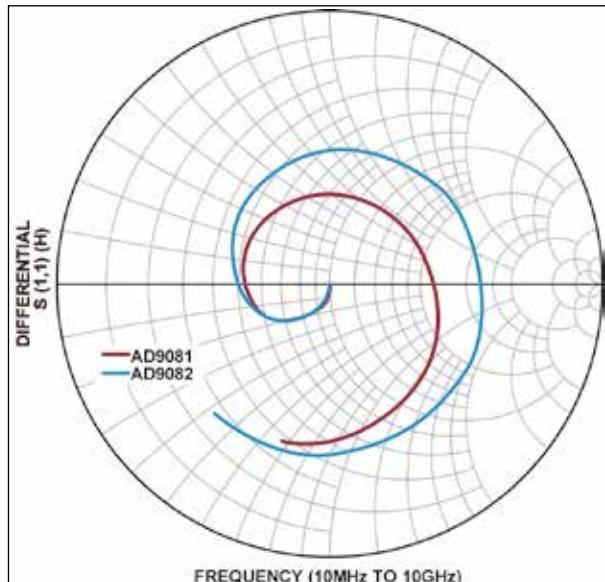

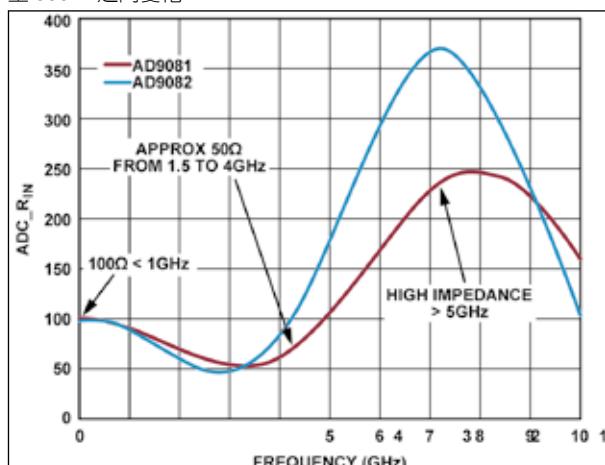

圖 29 顯示了運行 ADC S 參數分析模擬的結果。AD9081 曲線與圖 1 相匹配，但由於 AD9082 ADC 前端具有更高的晶片內寄生效應，因此其輸入阻抗隨頻率的變化比 AD9081 稍大。圖 30 顯示，ADC 輸入導納的實部在低頻時接近  $100 \Omega$ ，在 2 GHz 到 4 GHz 之間時下降到  $50 \Omega$  附近，然後在 4 GHz 以上時增大。

## ADC 電路分析

ADS 檔案中的 ADC\_Circuit\_Analysis 原理圖

圖 29: AD9081 和 AD9082 ADC 輸入阻抗隨頻率變化顯著

圖 30: AD9081 和 AD9082 ADC 輸入導納的實部隨頻率在  $50 \Omega$  至  $350 \Omega$  之間變化

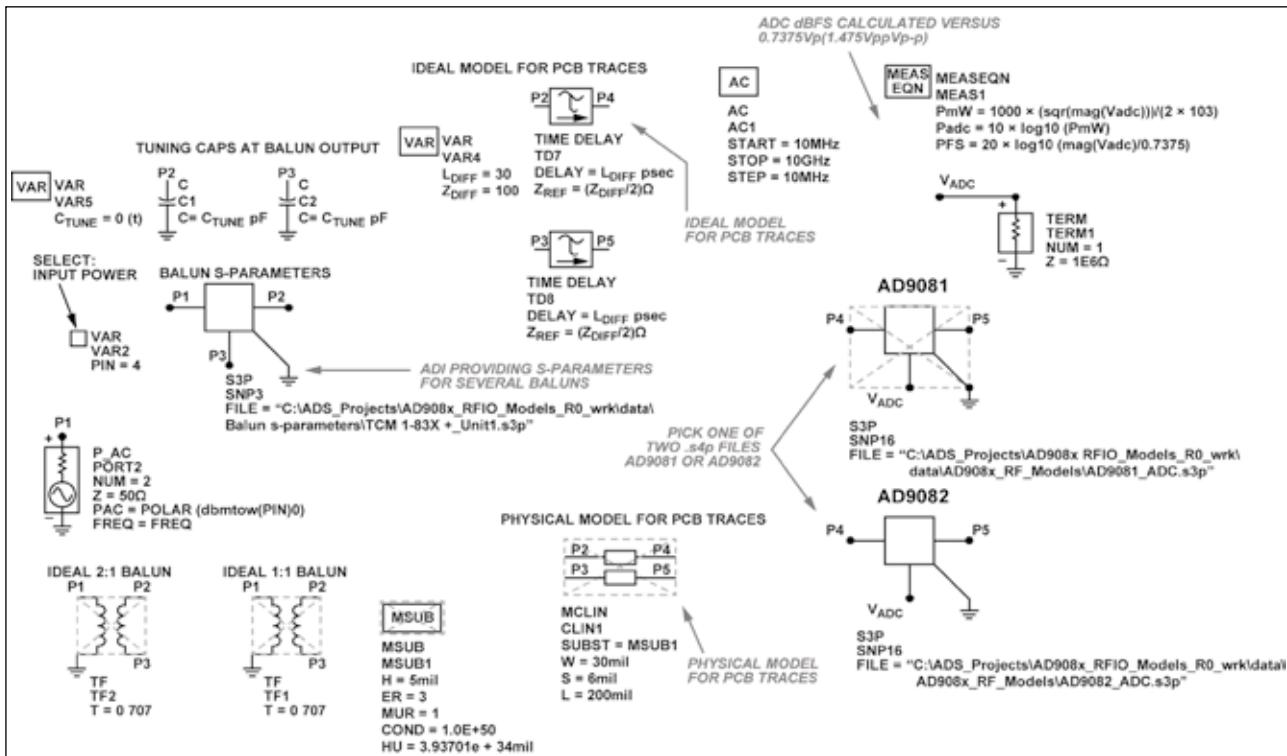

（參見圖 32）可用於模擬和優化特定頻率範圍內的 ADC 性能。用戶選擇所需的輸入功率 (dBm)，然後

圖 31: 用於 ADC S 參數分析的 ADS 電路原理圖

圖 32: 用於 ADC 電路分析的 ADS 電路原理圖

像 S 參數原理圖一樣，透過啟能或禁用兩個 .s3p 檔，

其以高阻抗端接。

用戶可以選擇 AD9081 或 AD9082 ADC。

接下來，用戶便可為其打算使用的特定巴倫選擇 S 參數。

.s3p 模型的埠 3 是 ADC 採樣器的輸入，因此

埠 3 是 ADC 採樣器的輸入，因此

圖 32 包含巴倫輸出和 ADC 輸入之間的 PCB 佈線的兩個簡化模型。對於理想模型，使用者選擇 PCB 佈線的差分阻抗 ( $\Omega$ ) 和佈線的電氣長度 (psec)。此種理想分析可用於分析不同 PCB 線路阻抗和長度對應的 ADC 性能。

對於 PCB 佈線的物理模型，使用者在 MSUB 模組中定義 PCB 的基本資訊（電介質厚度、介電常數和金屬厚度），然後在 MCLIN 模組中輸入 PCB 佈線的特定資訊（線寬、線距和線長）。物理分析可用於模擬不同 PCB 設計的 ADC 性能。

在實踐中，為使模擬的和測量的 ADC 頻率響應具有很好的一致性，ADI 發現有必要對 PCB 佈線執行 EM 模擬。

只要佈線和連接到巴倫單端輸入的同軸連接器與  $50\ \Omega$  匹配良好，就沒有必要將其納入 ADC 模擬中。

如果使用者計畫使用差模訊號直接驅動 AD9081 和 AD9082 ADC，那麼運行電路分析的簡單方法是禁用巴倫 .s3p 檔並使能理想 1:1 巴倫。然後可以修改埠 2 的電阻，以向 ADC 提供任何所需的差分源阻抗。

圖 32 中顯示的 MeasEqn 模組中的方程式用於感測傳送到 ADC 採樣器的電壓，並基於 0.7375 V 峰值 (1.475 V p-p) 的滿量程 ADC 輸入電壓將其轉換為 dBFS 值。出於除錯目的，ADC 採樣電壓也被轉換為功率 (dBm) 值（假設負載阻抗為  $100\ \Omega$ ）。

## ADI 評估板上測量和模擬的 ADC 頻率響應

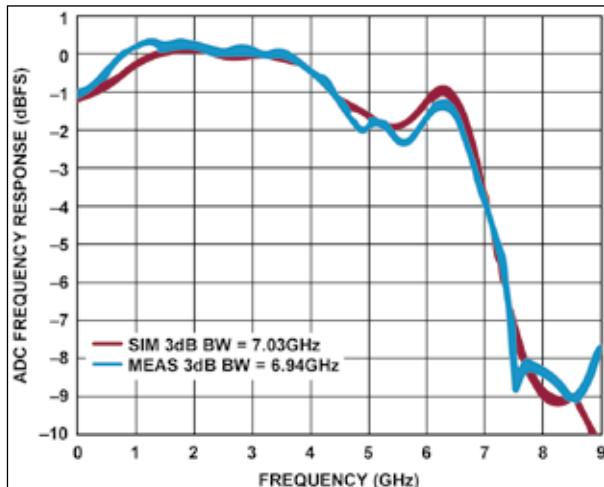

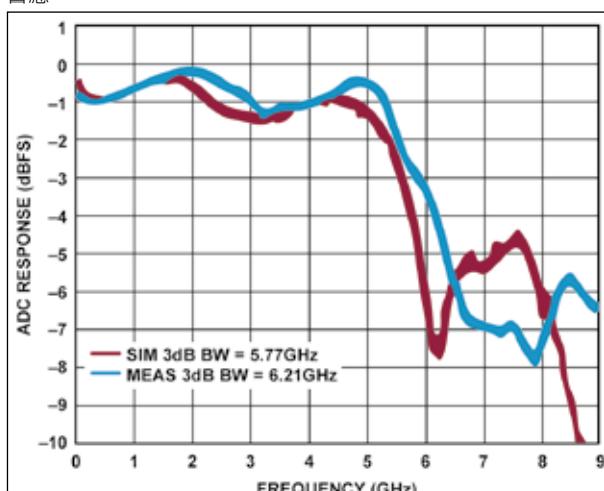

借助系統 PCB 的準確 EM 模型和所用巴倫的 s 參數，可以使用圖 32 所示的 ADC\_Circuit\_Analysis 原理圖來準確預測 AD9081 和 AD9082 ADC 的頻率響應。圖 33 和圖 34 顯示了使用 TCM1-83X+ 和 BALH-0009 巴倫的 AD9081 ADC 的模擬回應和測量回應。這些模擬是透過 PCB 的完整 EM 模擬完成的，其中包括佈線和巴倫輸出上的同軸連接器。

測量得出的和建模得出的 POUT 之間的一致性表明，AD9081 和 AD9082 ADC 模型為優化系統板

圖 33：使用 TCM1-83X+ 巴倫測量的和模擬的 AD9081 ADC 頻率響應

圖 34：使用 BALH-0009 巴倫測量的和模擬的 AD9081 ADC 頻率響應

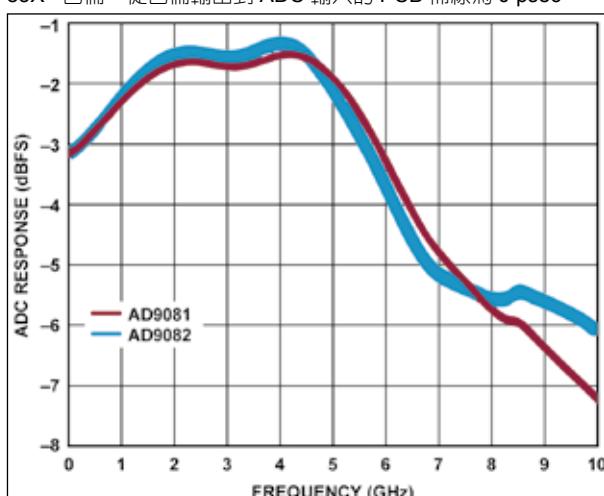

圖 35：AD9081 和 AD9082 的模擬頻率響應比較，使用 TCM1-83X+ 巴倫，從巴倫輸出到 ADC 輸入的 PCB 佈線為 0 psec

設計以實現所需 ADC 性能提供了一個有用的工具。

## 使用 AD9081 和 AD9082 ADC 模型優化系統性能

AD9081 和 AD9082 ADC 的輸入阻抗略有不同。圖 35 顯示了使用 TCM1-83X+ 巴倫的兩個不同模型的模擬頻率響應。由於寄生效應略高，AD9082 在較高頻率下的滾降速度比 AD9081 稍快。

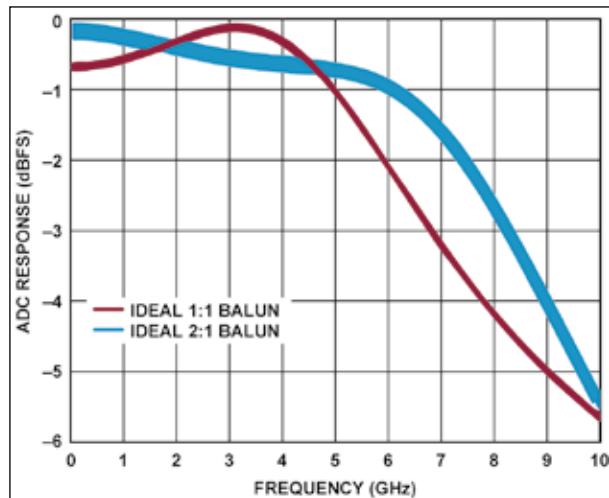

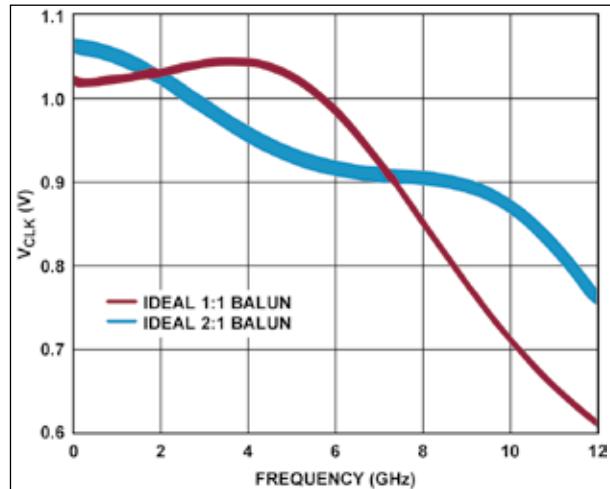

圖 36 顯示了 AD9081 的模擬 ADC 回應，其輸入端具有理想的 1:1 和 2:1 巴倫。根據圖 30，2:1 巴倫在較低和較高頻率時提供理想 ADC 回應，此時 ADC 輸入阻抗接近  $100\Omega$ 。但在 2 GHz 至 4 GHz

圖 36: 使用理想 1:1 和 2:1 巴倫的模擬 AD9081 ADC 回應

圖 37: 使用 TCM1-83X+ 巴倫的模擬 AD9081 ADC 回應，PCB 佈線長度為 30 psec

頻率範圍內，ADC 阻抗更接近  $50\Omega$ ，理想 1:1 巴倫為 ADC 輸入提供更大訊號。

根據圖 36 中使用理想巴倫進行的模擬，2:1 巴倫為 AD9081 和 AD9082 ADC 提供的頻寬似乎較好。然而，巴倫阻抗隨頻率變化明顯，巴倫輸出和 ADC 輸入之間的 PCB 佈線長度也提供了阻抗變換。基於模擬和測量確定，理想 ADC 頻寬是使用 1:1 巴倫（例如 TCM1-83X+）和  $100\Omega$  差分 PCB 佈線獲得的。

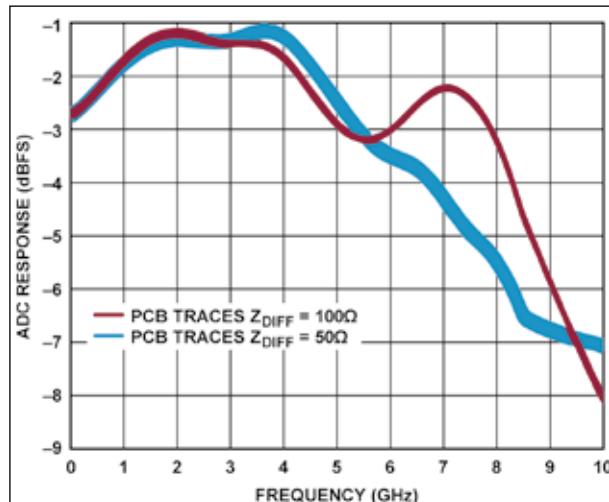

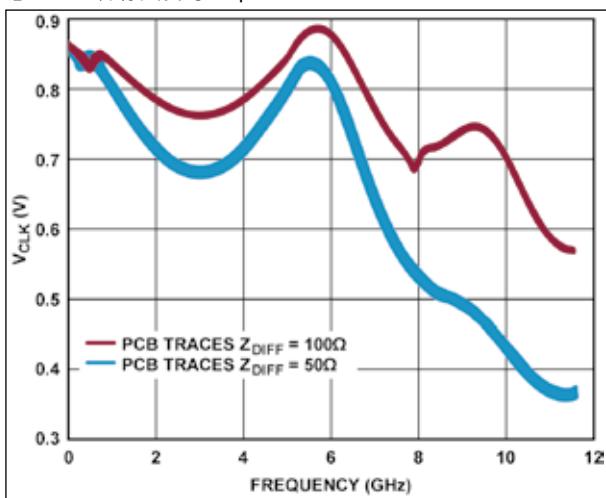

選擇巴倫之後，PCB 設計的第二重要的特性是用於將巴倫連接到 ADC 輸入的差分佈線。圖 37 顯示了 ADC 輸入和 TCM1-83X+ 巴倫之間使用理想  $100\Omega$  和  $50\Omega$  差分對的模擬 ADC 回應。圖 37 顯示， $100\Omega$  差分對可提供較好的整體性能。考慮到 TCM1-83X+ 是 1:1 巴倫，此結果出乎意料。巴倫輸出阻抗隨頻率變化明顯，AD9081 ADC 輸入阻抗也是如此。因此，這些阻抗與 PCB 佈線阻抗和長度之間的相互作用是一個複雜的阻抗匹配問題，只能透過電路模擬器來解決。

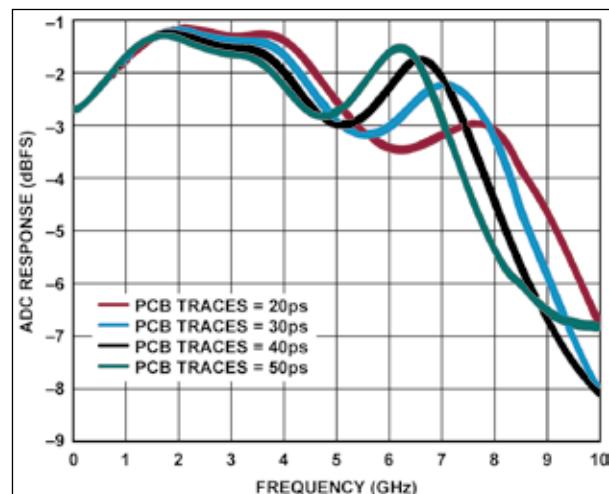

除了巴倫和 ADC 之間的 PCB 佈線的阻抗之外，這些佈線的長度還充當巴倫輸出阻抗和 ADC 輸入阻抗之間的調諧元件。圖 38 顯示，對於 TCM1-83X+ 巴倫，較短的  $100\Omega$  差分對線長可提供理想的 3 dB 頻寬。

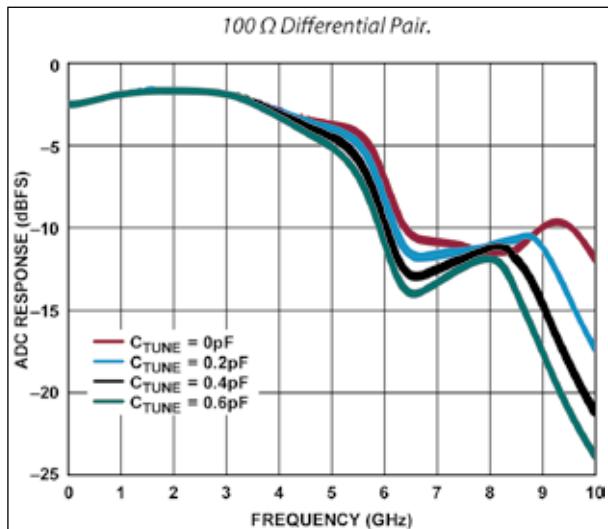

優化 AD9081 和 AD9082 ADC 回應的最後調

圖 38: 使用 TCM1-83X+ 巴倫和  $100\Omega$  差分對的模擬 AD9081 ADC 回應

圖 39：使用 TCM1-83X+ 的模擬 AD9081 ADC 頻率響應，巴倫輸出端有並聯調諧電容

諧手段是可以在巴倫的輸出埠增加小的並聯調諧電容。圖 39 表明，在 TCM1-83X+ 巴倫輸入端增加並聯電容會降低更高頻率下的性能。EM 模擬顯示，透過將巴倫的 GND 層從 PCB 的第 2 層移動到第 3 層，可以減少巴倫焊墊的寄生電容，並改善 ADC 的高頻響應。

## 在更高頻率下優化 AD9081 和 AD9082 ADC 性能

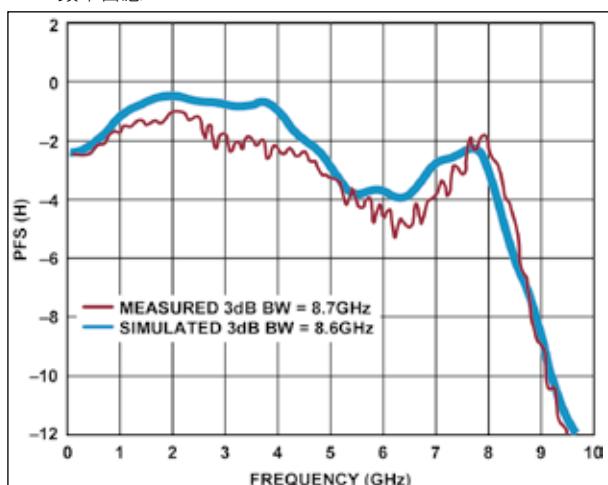

如 圖 33 所 示，AD9081 ADC 模型以及 AD9081 和 AD9082 評估板的 EM 模擬，提供了

圖 40：在更新的 PCB 設計上使用 TCM1-83X+ 測量的 AD9082 ADC 頻率響應

模擬的和測量的 ADC 回應與頻率的關係，使用 TCM1-83X+ 巴倫時，3 dB 頻寬接近 7 GHz。為了展示 7 GHz 以上的 ADC 性能，ADC 重新設計了使用 TCM1-83X+ 的 PCB。

對 Rev B PCB 設計的更改包括：移除巴倫輸出和 ADC 輸入之間的一些額外可選 SMT 元件，並使用圖 32 所示的 ADC 電路分析原理圖來調整連接巴倫到 ADC 的 100 Ω 差分對的長度。圖 40 顯示，這些設計調整提供的測量的和模擬的 AD9082 3 dB 頻寬大於 8.5 GHz。

## ADC 小結

AD9081 和 AD9082 ADC 的輸入阻抗隨頻率變化明顯，因此有必要使用模擬工具進行巴倫選擇和 PCB 設計，以優化 ADC 在特定目標頻段的響應。ADS 檔案中的 ADC\_Circuit\_Analysis 原理圖（參見圖 32）可用來執行此任務。

優化 ADC 性能的關鍵設計參數如下：

- 巴倫選擇。

- 巴倫輸出和 ADC 輸入之間的 PCB 佈線的阻抗。

- 巴倫輸出和 ADC 輸入之間的 PCB 佈線的長度。

- 巴倫輸出端的並聯電容。

除了前面列出的專案，還應注意巴倫輸入端的任何 PCB 佈線或同軸電纜連接器也應很好地匹配 50 Ω。

為使模擬的和測量的 AD9081 和 AD9082 ADC 頻率響應實現良好的相關性，有必要對所有 PCB 佈線進行全 EM 模擬，以考慮所有寄生效應（例如安裝焊墊、貫孔和同軸電纜連接器）。

透過適當選擇巴倫並精心設計 PCB，AD9081 和 AD9082 ADC 可以實現大於 7.5 GHz 的 3 dB 頻寬。

## AD9081 和 AD9082 時脈模型

AD9081 和 AD9082 可由高達 12 GHz 的外部時脈訊號驅動。ADS 檔案提供了一個模型協助優化 PCB 設計，以盡可能提高特定頻率範圍內提供給時脈輸入的電壓。

## 時脈 S 參數分析

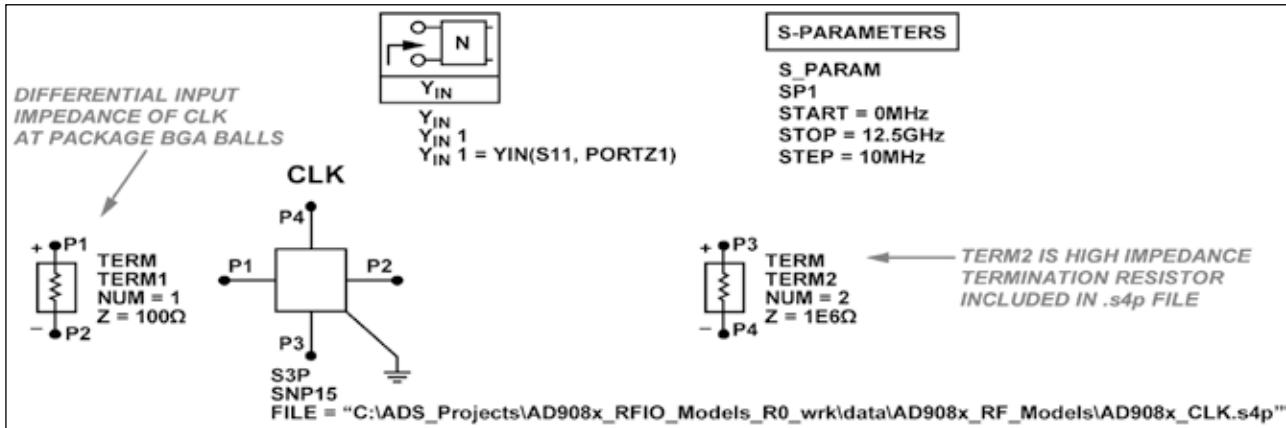

ADS 檔案中的時脈 s 參數分析原理圖 (參見

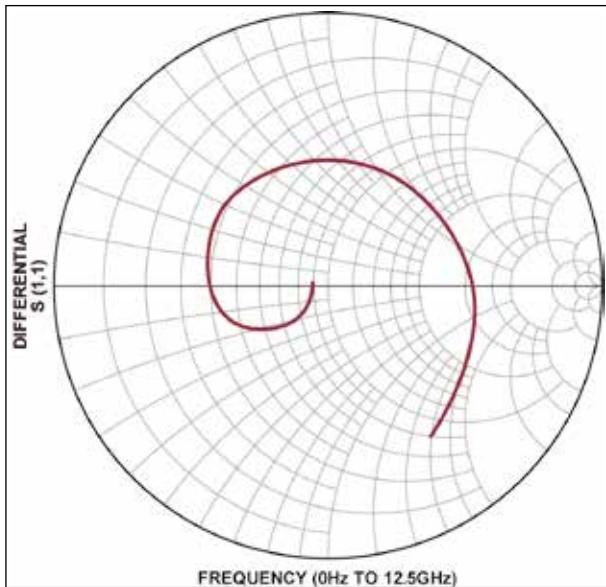

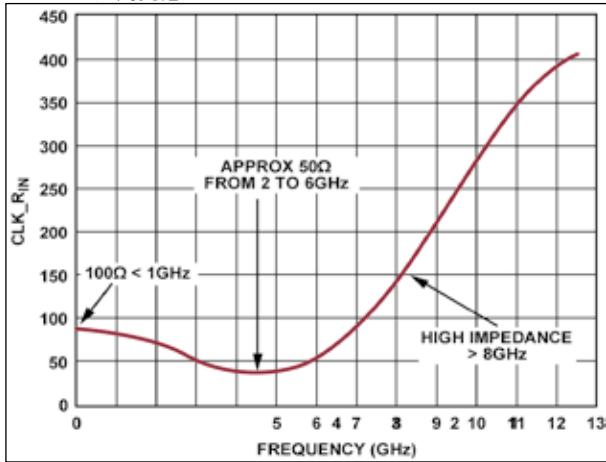

圖 41:AD9081 和 AD9082 CLK 輸入阻抗隨頻率變化明顯

圖 42:AD9081 和 AD9082 時脈輸入導納的實部隨頻率在 50 Ω 至 400 Ω 之間變化

圖 43: 用於時脈 S 參數分析的 ADS 電路原理圖

圖 43) 可用於查看封裝 BGA 接腳處 AD9081 和 AD9082 的時脈輸入阻抗。TERM2 是時脈輸入緩衝器的高阻抗節點。因此，對於 S 參數分析，TERM2 以  $1 M\Omega$  電阻端接。

對於非 ADS 用戶，AD9081/2\_RF\_Models.zip 檔中包含同樣的 .s4p 檔，任何電路模擬器都可以使用。

圖 41 和圖 42 顯示了運行 CLK\_S-parameter\_Analysis 模擬的結果。圖 42 顯示，時脈輸入導納的實部在低頻時接近  $100 \Omega$ ，在 3 GHz 到 6 GHz 之間時下降到  $50 \Omega$  附近，然後在 12 GHz 時增加到  $400 \Omega$ 。

## 時脈電路分析

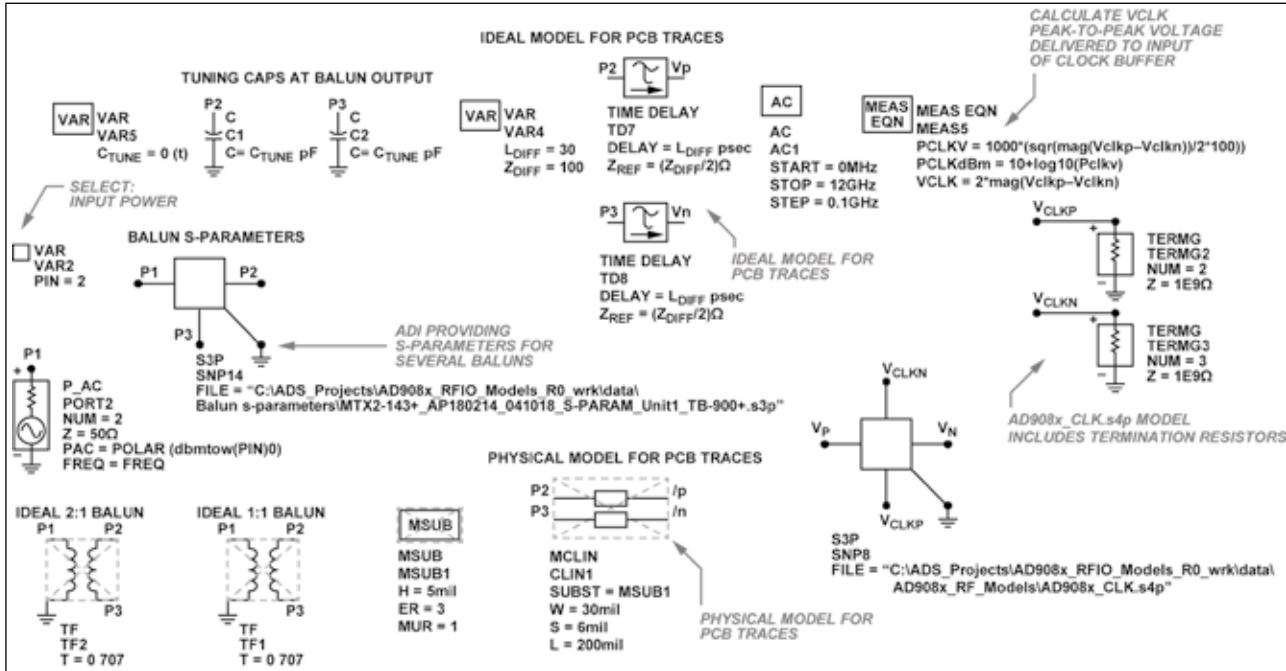

ADS 檔案中的 CLK\_Circuit\_Analysis 原理圖 (參見圖 44) 可用於模擬和優化特定頻率範圍內的時脈性能。

.s4p 模型的埠 3 和埠 4 是時脈緩衝器的輸入，二者均以高阻抗端接。為獲得理想時脈性能，透過這兩個埠傳送的電壓必須大於  $1.0 V$  p-p。

在圖 44 中，用戶可以選擇不同的巴倫 .s3p 檔用於電路模擬。

圖 44 所示的原理圖還包含巴倫輸出和時脈輸入之間的 PCB 佈線的兩個簡化模型。對於理想模型，使用者選擇 PCB 佈線的差分阻抗 ( $\Omega$ ) 和佈線的電氣長度 (psec)。這種理想分析可用於分析不同 PCB 線路阻抗和長度對應的時脈性能。

對於 PCB 佈線的物理模型，使用者在圖 44 所

圖 44: 用於時脈電路分析的 ADS 電路原理圖

示原理圖的 MSUB 模組中定義 PCB 的基本資訊 (電介質厚度、介電常數和金屬厚度)，然後在 MCLIN 模組中輸入 PCB 佈線的特定資訊 (線寬、線距和線長)。物理模型可用於模擬不同 PCB 設計的時脈性能。

如果使用者計畫使用差模訊號直接驅動 AD9081 和 AD9082 時脈，那麼運行 ADC 分析的簡單方法是禁用巴倫 .s3p 檔並致能理想 1:1 巴倫。然後可以修改埠 2 阻抗的電阻，以向時脈提供任何所需的差分源阻抗。

圖 44 所示 ADS 原理圖中的 MeasEqn 模組中的方程式用於感測傳送至時脈緩衝器的峰對峰值電壓。出於除錯目的，時脈電壓也被轉換為功率 (dBm) 值 (假設負載阻抗為  $100\Omega$ )。

## 使用 AD9081 和 AD9082 時脈模型優化系統性能

圖 45 顯示了 AD9081 和 AD9082 的模擬時脈響應，其輸入端具有理想的 1:1 和 2:1 巴倫。如圖 42 所示，時脈輸入阻抗隨頻率變化明顯。圖 45 顯示，2:1 巴倫在較低和較高頻率時提供理想時脈響應，但在 2 GHz 至 6 GHz 頻率範圍內 (圖 42 顯示

圖 45: 使用理想 1:1 和 2:1 巴倫的模擬 AD9081 時脈響應

此時時脈阻抗更接近  $50\Omega$ ），理想 1:1 巴倫為時脈輸入提供的電壓最高。

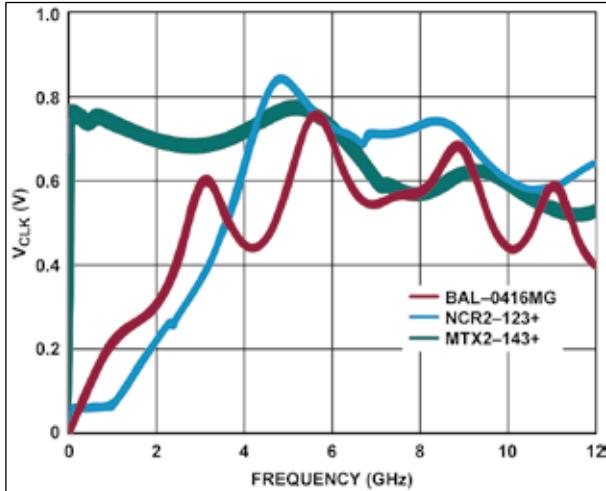

為了在 12 GHz 的最大時脈速率下獲得理想性能，建議 AD9081 和 AD9082 使用 2:1 巴倫。圖 46 提供了以下巴倫對應的模擬 VCLK 電壓：Marki BAL-0416SMG (4 GHz 至 16 GHz 2:1)、Mini-Circuits MTX2-143+ (5.5 GHz 至 13.5 GHz 2:1) 和 NCR2-123+ (4.7 GHz 至 12 GHz 2:1)。

選擇巴倫之後，PCB 設計的第二重要的特性是

圖 46: 使用不同巴倫的模擬 AD9081 時脈響應

用於將巴倫連接到時脈輸入的差分佈線。圖 47 顯示 100 Ω 差分對向時脈輸入提供的電壓擺幅大於 50 Ω PCB 佈線。

圖 47: 使用 MTX2-143+ 巴倫的模擬 AD9081 和 AD9082 時脈回應，PCB 佈線長度為 30 psec

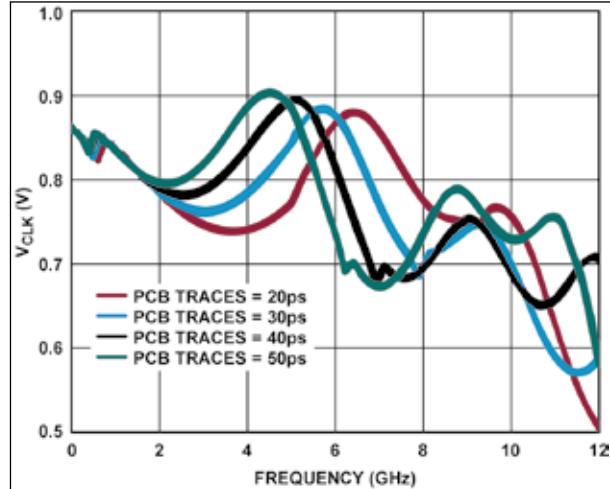

除了巴倫和時脈輸入之間的 PCB 佈線的阻抗之外，這些佈線的長度還充當巴倫輸出阻抗和時脈輸入阻抗之間的調諧元件。圖 48 顯示，對於 MTX2-143+ 巴倫，將巴倫連接到時脈輸入的 100 Ω 差分對的長度導致實際傳送至時脈緩衝器的電壓出現明顯的峰值和穀值。因此，必須調整此 PCB 佈線的長度，以在特定目標時脈頻率時達到最大值。

對於超過 4.5 GHz 的高 RF 時脈頻率產生，可以考慮使用寬頻頻率合成器 IC，例如 ADF5610 或

圖 48: 使用 MTX2-143+ 巴倫和 100Ω 差分對的模擬 AD9081 和 AD9082 時脈回應

ADF4372。這些 IC 具有基頻壓控振盪器 (VCO) 模式，分別擴展到 7.3 GHz 和 8.0 GHz，內部時脈倍頻器用於合成超出基頻 VCO 限值的輸出頻率。

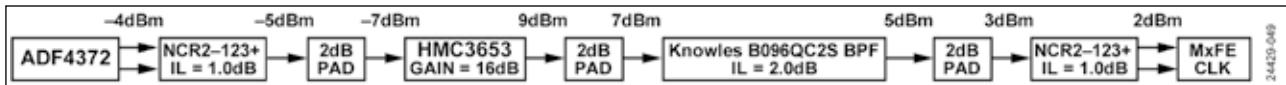

圖 50 顯示了以 12 GHz 驅動 AD9081 和 AD9082 時脈輸入的建議解決方案。ADF4372 倍頻器輸出經過調整，可提供 -4 dBm 的輸出功率。Mini-Circuits NCR2-123+ 巴倫用於將 ADF4372 差分輸出轉換為 50 Ω 單端，然後由 HMC3653 增益模組放大，並由 Knowles B096QC2S 8 GHz 至 12 GHz 帶通濾波器進行濾波。最後，第二個 NCR2-123+ 巴倫將濾波器的單端輸出轉換為差模訊號，以驅動 AD9081 和 AD9082 時脈輸入。可選的 2 dB 焊

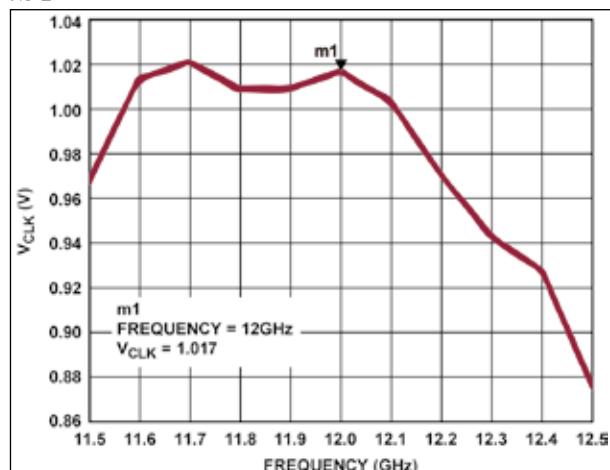

圖 49: 使用建議時脈解決方案時輸送到內部時脈輸入緩衝器的模擬電壓

圖 50: 以 12 GHz 驅動 AD9081 和 AD9082 時脈輸入的建議解決方案

墊用於降低各種元組件之間的電壓駐波比 (VSWR) 相互作用。

模擬顯示，該訊號鏈可為 AD9081 和 AD9082 時脈輸入緩衝器提供所需的 1.0 V p-p 電壓 (參見圖 49)。

## 時脈小結

AD9081 和 AD9082 時脈的輸入阻抗隨頻率變化明顯，因此有必要使用模擬工具進行巴倫選擇和 PCB 設計，以優化其在特定目標頻段的性能。圖 43 所示的時脈電路分析原理圖可用於執行此任務。

優化傳送至時脈輸入緩衝器的電壓的關鍵設計

參數如下：

- 巴倫選擇。

- 巴倫輸出和時脈輸入之間的 PCB 佈線的阻抗。

- 巴倫輸出和時脈輸入之間的 PCB 佈線的長度。

除了前面列出的專案，還應注意巴倫輸入端的任何 PCB 佈線或同軸電纜連接器也應能更匹配 50 Ω。

為了準確預測時脈頻率響應，有必要對時脈 PCB 佈線進行全 EM 模擬，以考慮所有寄生效應 (安裝焊墊、貫孔和同軸電纜連接器)。CTA

## SEMI:2024 年全球半導體產能將達每月 3,000 萬片新高

SEMI 國際半導體產業協會公佈最新一季全球晶圓廠預測報告 (World Fab Forecast, WFF)，全球半導體產能繼 2023 年以 5.5% 成長至每月 2,960 萬片晶圓 (wpm, wafers per month) 之後，預計 2024 年將增速成長 6.4%，突破 3,000 萬片大關。

不同於 2023 年的產能擴張溫和主要受到市場需求走緩，半導體進入庫存調整期所致；2024 年包含生成式 AI 和高效能運算 (HPC) 等應用推動，以及晶片在終端需求的復甦，加速先進製程和晶圓代工產能擴增。

最新一季全球晶圓廠預測報告顯示，2022 年至 2024 年預測期間，全球半導體產業計劃將有 82 座新設施投產，其中 2023 年及 2024 分別有 11 座及 42 座投產，涵蓋了 4 吋 (100mm) 到 12 吋 (300mm) 晶圓的生產線。

### 中國推升半導體產業擴展

受惠於政府資金挹注和其他獎勵措施，預期中國將擴大其在全球半導體產能的占比。中國晶片製造商預計 2024 年將展開 18 座新晶圓廠，產能年增率將從 2023 年的 12% 提升至 2024 年的 13%，產能將從 760 萬片推升成長至 860 萬片。

台灣仍將維持全球第二大半導體產能排名，產能年增率分別為 2023 年的 5.6% 及 2024 年的 4.2%，每月產能由 540 萬片成長至 570 萬片，預計自 2024 年起將有 5 座新晶圓廠投產。

全球半導體產能排名第三的韓國，預計 2024 年將有 1 座新晶圓廠投產，產能將從 2023 年 490 萬片成長

5.4% 至 2024 年 510 萬片；而產能位居全球第四的日本，預計 2024 年將有 4 座新晶圓廠投產，產能將從 2023 年 460 萬片成長至 2024 年 470 萬片，年成長率約 2%。

全球晶圓廠預測報告顯示，美洲地區到 2024 年將有 6 座新晶圓廠投產，晶圓產能年增率將達 6% 提升至 310 萬片。歐洲和中東地區在 2024 年將有 4 座新晶圓廠投產，預計將增加 3.6% 產能，達到 270 萬片。東南亞 2024 年將展開 4 座新晶圓廠投產，預計產能將增加 4%，來到 170 萬片。

### 晶圓代工領域產能持續強勁成長

晶圓代工業者合計將持續採購最多的半導體設備，引領半導體產業擴張，其產能提升將從 2023 年的 930 萬片，至 2024 年達 1,020 萬片的新紀錄。受到個人電腦和智慧型手機等消費性電子產品需求疲軟影響，2023 年記憶體領域產能擴張趨緩；DRAM 領域產能預計在 2023 年微幅增加 2% 至 380 萬片，2024 年則增加 5% 至 400 萬片；3D NAND 每月產能預計 2023 年持平，保持在 360 萬片，隔年則將成長 2% 至 370 萬片。

分離元件和類比領域，電動車進展仍是產能擴張的關鍵驅動因素。分離元件產能預計將在 2023 年成長 10%，達到 410 萬片，到 2024 年將成長 7%，達到 440 萬片；而類比領域產能預計將在 2023 年成長 11%，達到 210 萬片，到 2024 年則將成長 10%，達到 240 萬片。