IBIS 建模—第 2 部分：

# 爲何以及如何創建您自己的 IBIS 模型 (II)

本文提供創建 IBIS 模型時如何使用 LTspice 的指南，涵蓋從 IBIS 預建模程式到 IBIS 模型驗證的整個過程，並詳細介紹如何在 LTspice 中為 IBIS 模型準確擷取 I-V、V-T、斜坡和 C\_comp 數據。此外，本文並提供定性和定量 FOM 方法，用於驗證 IBIS 模型的性能。該應用案例展示了為假設的 ADxxxx 三態數位緩衝器開發 IBIS 模型的過程，其中包含適合輸入和三態 CMOS 介面的可用 IBIS 範本，有助於即刻開始創建您的 IBIS 模型。

■作者：Rolynd Aquino, Janchris Espinoza / 產品應用工程師

Francis Ian Calubag / 系統應用工程師

## 建構 IBIS 模型

所有提取的 I-V 和 V-T 數據都將編譯到 BIS 模型 (.ibs) 文件中。以下是 IBIS 檔的實際範本，使用者可以在建構 IBIS 模型時用作參考。

.ibs 檔以 [IBIS Ver] 關鍵字開頭，後接檔案名和修訂號。IBIS 版本 3.2 將在 [IBIS Ver] 關鍵字中使用，因其是建構 3 態輸出緩衝器所需的最低版本。.ibs 檔的檔案名應和 [檔案名稱] 關鍵字中的檔案名相同；否則，解析器會將其檢測為錯誤。此外，檔案名不得包含任何大寫字母，因為解析器只允許檔案名使用小寫字母。有關其他重要的關鍵字，將在後面章節中討論。

```

|

[Component] ad3000

[Manufacturer] Analog Devices, Inc.

[Package]

[Variable]

R_pkg    3.59E-02    NA    NA

L_pkg    2.52E-09    NA    NA

C_pkg    1.38E-12    NA    NA

|

[Pin]  signal_name  model_name

1     VDD1          Power

2     DIN1          cmos_dil

3     EN             cmos_en

4     DOUT1         cmos_out1

5     GND            GND

6     NC             NC

```

.ibs 檔的下一部分包括 [組件]、[製造商]、[封裝] 和 [接腳] 關鍵字。ADxxxx 有兩個輸入緩衝器

(DIN1 和 EN) 和一個輸出緩衝器 (DOUT1)，因此其 IBIS 模型總共有三個緩衝器模型。[封裝] 關鍵字透過 RLC 封裝寄生值作為元件的封裝模型。所有元件緩衝器的模型名稱在 [接腳] 關鍵字下定義，這與在 [模型] 關鍵字下定義命名變數類似。

```

*****

Model: cmos_dil

*****

|

[Model]      cmos_dil

Model_type   Input

Vin1=0.36

Vinh=1.44

variable     typ      min      max

C_comp       1.645481e-012  NA      NA

|

[Temperature Range]  25    NA      NA

[Voltage Range]      1.8   NA      NA

[Power Clamp Reference]  1.8  NA      NA

[GND Clamp Reference]  0    NA      NA

|

[Power_clamp]

|  Voltage  I (typ)  I (min)  I (max)

|  -1.800000  1.096645E+00  NA      NA

|  -1.700000  1.714524E+00  NA      NA

|  -1.600000  1.511816E+00  NA      NA

|

|  1.700000   7.601960E-12  NA      NA

|  1.800000   2.800000E-12  NA      NA

|  3.600000  -4.400000E-12  NA      NA

|

[GND_clamp]

|  Voltage  I (typ)  I (min)  I (max)

|  -1.800000  -1.895275E+00  NA      NA

|  -1.700000  -1.710353E+00  NA      NA

|  -1.600000  -1.507553E+00  NA      NA

|

|  1.700000   1.455209E-11  NA      NA

|  1.800000   1.620648E-11  NA      NA

|  3.600000   2.140000E-11  NA      NA

|

*****

End of Model: cmos_dil

*****

```

在 .ibs 檔的下一部分，使用測量得出的 I-V 和 V-T 數據建構元件的數位緩衝器的模型。緩衝器模型的內容因 Model\_type 變數中指定的緩衝區類型而異。由於模型 cmos\_di1 是一個輸入緩衝器，其緩衝器模型只包含 C\_comp、[Power\_Clamp] 和 [GND\_Clamp] 數據。輸入緩衝器模型並包括  $V_{INH}$  和  $V_{INL}$  值，這兩個值都可以在元件的產品手冊中找到。由於 DIN1 和 EN 都是輸入緩衝器，所以其緩衝器模型具有相同的結構。

另一方面，3 態緩衝器模型包含一些與輸入緩衝器模型類似的關鍵字，但包含額外的 I-V 和 V-T 數據。cmos\_out1 的緩衝器模型包括一個額外的子參數 Cref，其代表輸出電容負載，並包括 Vmeas，其代表基準電壓位準。通常情況下，使用的 Vmeas 是 VDD 值的一半。

```

*****

Model:cmos_out1

*****

[Model]

cmos_out1

Model_type 3-state

Cref=15pF

Vmeas=0.9

| variable   typ   min   max

C_comp      4.143501E-11 NA    NA

|

[Temperature Range] 25   NA    NA

[Voltage Range] 1.8   NA    NA

[POWER Clamp Reference] 1.8   NA    NA

[GND Clamp Reference] 0    NA    NA

[Pullup Reference] 1.8   NA    NA

[Pulldown Reference] 0    NA    NA

|

[POWER_clamp]

| Voltage   I (typ)   I (min)   I (max)

-1.800000E+00 2.074265E+00 NA    NA

-1.700000E+00 1.887999E+00 NA    NA

-1.600000E+00 1.685262E+00 NA    NA

|

1.700000E+00 -6.471900E-11 NA    NA

1.800000E+00 -1.606903E-10 NA    NA

3.600000E+00 -8.012131E-10 NA    NA

|

[GND_clamp]

| Voltage   I (typ)   I (min)   I (max)

-1.800000E+00 -2.047257E+00 NA    NA

-1.700000E+00 -1.861165E+00 NA    NA

-1.600000E+00 -1.658421E+00 NA    NA

|

1.700000E+00 1.221660E-10 NA    NA

1.800000E+00 1.638958E-10 NA    NA

3.600000E+00 5.271379E-10 NA    NA

|

```

除了 C\_comp、[Power\_Clamp] 和 [GND\_Clamp]，3 態緩衝器還包含額外的 I-V 數據：[上拉] 和 [下拉]。

最後，所有 IBIS 模型都應該用 [結尾] 關鍵字作為結尾。

```

[Pullup]

| Voltage   I (typ)   I (min)   I (max)

-1.800000E+00 2.075567E+00 NA    NA

-1.700000E+00 1.889618E+00 NA    NA

-1.600000E+00 1.686874E+00 NA    NA

|

1.700000E+00 -2.166668E-02 NA    NA

1.800000E+00 -2.181376E-02 NA    NA

3.600000E+00 -2.453158E-02 NA    NA

|

[Pulldown]

| Voltage   I (typ)   I (min)   I (max)

-1.800000E+00 -2.048355E+00 NA    NA

-1.700000E+00 -1.862534E+00 NA    NA

-1.600000E+00 -1.659785E+00 NA    NA

|

1.700000E+00 1.934561E-02 NA    NA

1.800000E+00 1.942086E-02 NA    NA

3.600000E+00 2.086263E-02 NA    NA

|

[Rising Waveform]

R_fixture = 50

V_fixture = 1.8

|

| time   V (typ)   V (min)   V (max)

0.000000E+00 8.722465E-01 NA    NA

4.000854E-10 8.722824E-01 NA    NA

8.001709E-10 8.723076E-01 NA    NA

|

3.880829E-08 1.799903E+00 NA    NA

3.920837E-08 1.799910E+00 NA    NA

4.000000E-08 1.799923E+00 NA    NA

|

[Falling Waveform]

R_fixture = 50

V_fixture = 1.8

|

| time   V (typ)   V (min)   V (max)

0.000000E+00 1.800005E+00 NA    NA

5.001068E-10 1.799995E+00 NA    NA

1.000214E-09 1.799995E+00 NA    NA

|

4.851036E-08 8.723745E-01 NA    NA

4.901047E-08 8.723730E-01 NA    NA

5.000000E-08 8.723702E-01 NA    NA

|

[Rising Waveform]

R_fixture = 50

V_fixture = 0

|

| time   V (typ)   V (min)   V (max)

0.000000E+00 -5.744911E-06 NA    NA

1.050224E-09 7.964322E-06 NA    NA

2.100449E-09 4.059370E-05 NA    NA

|

1.018718E-07 1.004326E+00 NA    NA

1.029220E-07 1.004331E+00 NA    NA

1.050000E-07 1.004340E+00 NA    NA

|

```

## IBIS 模型驗證

正如本系列文章的第一部分所述，IBIS 模型驗證由解析器測試和相關過程組成。這些是確保 IBIS

檔符合 IBIS 規範的必要步驟，並且模型的執行盡可能接近參考 SPICE 模型。

## 解析器測試

對於上一節中創建的 IBIS 檔，首先應進行解析器測試，然後再繼續執行相關過程。`ibischk` 是用於檢查 IBIS 檔的 **Golden Parser**。其用於檢查 IBIS 檔是否符合 IBIS 協會設定的規範。有關更多資訊，請參閱 [ibis.org](http://ibis.org)。本文撰寫時，使用的最新解析器是 `ibischk` 版本 7。

**Visual IBIS Editor** 工具有助於簡化語法檢查。但是，如果用戶沒有這些工具，可以瀏覽 [ibis.org](http://ibis.org) 免費下載可執行代碼。它是在各種作業系統上編譯的，所以用戶不必擔心應使用哪種作業系統。

## 相關程式

在這個驗證階段，需要檢查 IBIS 模型的性能是否與參考模型（在本例中為 SPICE 模型）相同。表 7 顯示不同的 IBIS 品質級別（從 0 級到 3 級）。其描述了經受不同程度測試後，IBIS 模型的精準程度。在本例中，由於參考模型是 ADxxxx SPICE 模型，所以產生的 IBIS 模型的品質等級為 2a。表示其通過了解析器測試，具有產品手冊中所描述的一組正確完整的參數，並通過了相關程式。

表 7:IBIS 品質等級

| 品質等級 | 說明                                               |

|------|--------------------------------------------------|

| 0 級  | 通過 <b>Golden Parser</b> ( <code>ibischk</code> ) |

| 1 級  | 與檢查清單檔中一樣完整、正確。                                  |

| 2a 級 | 與模擬相關                                            |

| 2b 級 | 與測量相關                                            |

| 3 級  | 以上全部                                             |

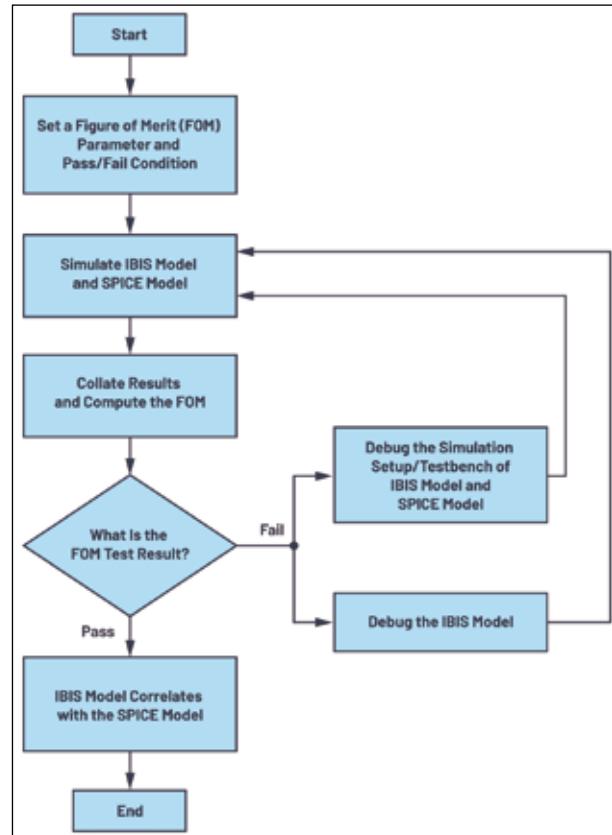

要將 IBIS 模型與參考 SPICE 模型關聯起來，可以按照一些常規步驟執行操作。圖 30 中的流程圖總結了這些步驟。

## 設定品質因數

關聯的基礎是在相同的載入條件和輸入刺激

圖說 30:IBIS 與 SPICE 模型的關聯流程圖。

下，IBIS 模型的行為應該與 SPICE 模型數位介面相同。這表示從理論上，其輸出應該重疊在一起。一般來說，有兩種方法可以描述 IBIS 模型的輸出與 SPICE 參考模型的接近程度：定性方法和定量方法。使用者可以使用此兩種方法來確定 IBIS 模型與 SPICE 模型之間的關係。

定性 FOM 測試需要依靠使用者的觀察能力。其要求對兩個輸出進行目視檢查，以確定是否通過相關性檢查。這可以透過疊加 IBIS 和 SPICE 的輸出結果來實現，並使用工程判斷來確定圖形是否相關。在進行定量 FOM 測試之前，這可以作為相關性初步檢查。當介面以相對較低的頻率或位元速率運行時，此測試就已足夠。

IBIS IO 緩衝器精度手冊中提出了另一種定性 FOM 測試，即曲線包絡度。其使用過程電壓溫度極值定義的最小和最大曲線。最小和最大曲線作為相關性的邊界。要通過測試，IBIS 結果中的所有點都應該在最小和最大曲線之內。此種方法在本文中不

適用，因其僅適用於典型條件。

定量 FOM 測試使用數學運算來衡量 IBIS 與 SPICE 之間的相關性。在 IBIS IO 緩衝器精度手冊中也提出了曲線包絡度，其使用 IBIS 和 SPICE 輸出的數據點。計算 IBIS 和參考數據點之間 x 軸或 y 軸差值的絕對值除以軸上使用的總範圍和點數的乘積的總和。具體如公式 3 所示，此方法適合作為檢測本文所示的應用案例的關聯方法。但是，還需要考慮其他因素。公式 3 中提供的 FOM 要求將 IBIS 和 SPICE 的結果映射到一個通用的 x-y 網格上，這將用到數值演算法和插值方法。如果用戶想要執行快速定量 FOM 測試，本文提出了另一種方法，即使用曲線和 x 軸所限定的面積的曲線面積度量。

$$FOM_{COM} = 100\% \times \left[ 1 - \frac{\sum_{i=1}^N |x_i(\text{reference}) - x_i(\text{IBIS})|}{\Delta x \times N} \right] \quad (3)$$

曲線面積度量以 SPICE 結果為參考，比較 IBIS 曲線下的計算面積。具體如公式 4 所示。但是，在進行曲線面積度量測試之前，所創建的模型必須通過定性測試。這確保了 IBIS 和 SPICE 曲線是同步的，並且相互疊加。在擷取曲線下的面積時，因為對 IBIS 和 SPICE 結果使用了相同的方法，所以用戶可以使用數值方法，例如梯形規則或中點規則。在使用這種方法時，建議使用盡可能多的點，以更接近該面積。

$$FOM_{CAM} = 100\% \times \left[ 1 - \frac{|A_{\text{IBIS}} - A_{\text{SPICE}}|}{A_{\text{SPICE}}} \right] \quad (4)$$

### 驗證 ADxxxx IBIS 模型

IBIS 模型驗證的第一步是解析器測試。圖 31

圖說 31:ADxxxx 解析器測試結果。

顯示 adxxxx.ibsIBIS 模型檔的解析器測試結果，該檔是使用 HyperLynx Visual IBIS Editor 編寫的。使用者執行解析器測試時，目標是不會出現任何錯誤。如果出現任何錯誤或警告提示，模型建構人員需要加以解決。如此可以保證 IBIS 模型在模擬工具之間的相容性。

下一步是設定 FOM 參數。本文僅使用定性 FOM 和曲線面積度量作為衡量相關性的方法。該測試可能會使用 IBIS 和 SPICE 在相同負載條件和輸入刺激下的瞬態響應曲線。曲線面積度量  $FOM \geq 95\%$  才能通過相關性測試。DOUT1、DIN1 和 EN 的相關性如下所示。

### DOUT1

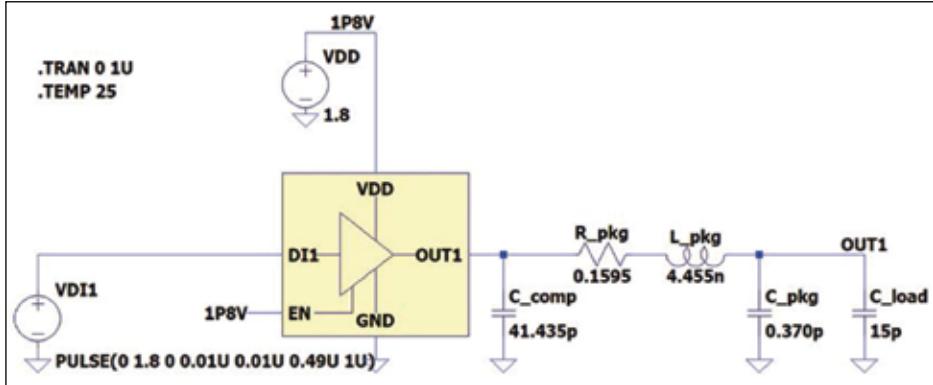

圖 32 顯示了 LTspice 上用於檢測 DOUT1 相關性的 SPICE 測試台。在原理圖上提供適當的電壓電源以啟動驅動器，並且為 DIN1 接腳提供脈衝訊號源來驅動 DOUT1。要在 LTspice 中完成 DOUT1 驅動器模型，還需要使用額外的元件。C\_comp 代表晶片電容。將 C\_comp 和 C\_load 添加到 LTspice 模型後，繼續加入 RLC 封裝寄生 (R\_pkg、L\_pkg、C\_pkg) 和 C\_load。

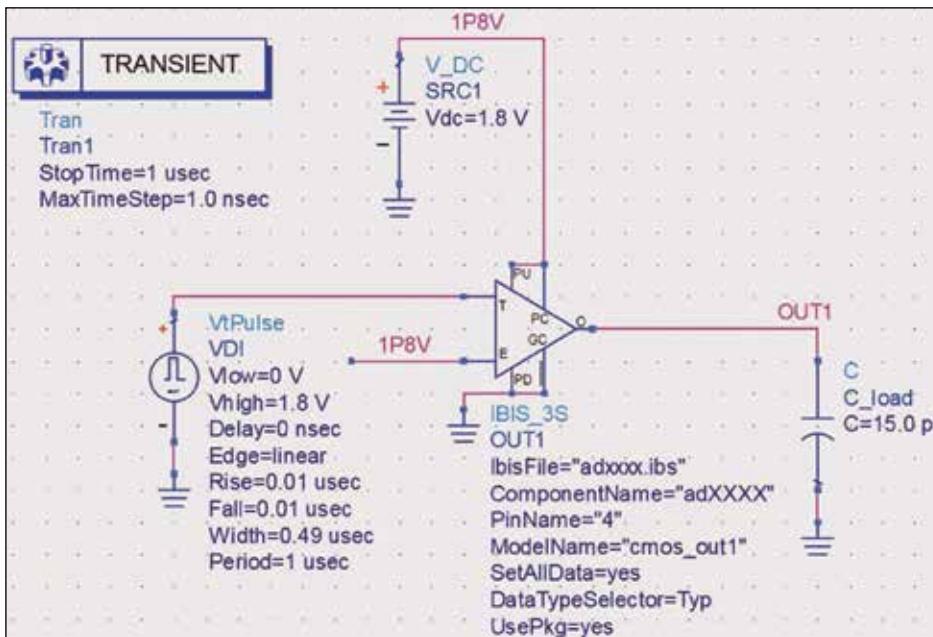

DOUT1 IBIS 模型相關性測試台建立在 Keysight 先進設計系統 (ADS) 上，如圖 33 所示。與 LTspice 測試台一樣，使用相同的輸入激發、C\_load、電壓電源和瞬態分析。但是，未在原理圖中顯示 C\_comp 和 RLC 封裝寄生，因其已經包含在 3 態 IBIS 模組中。

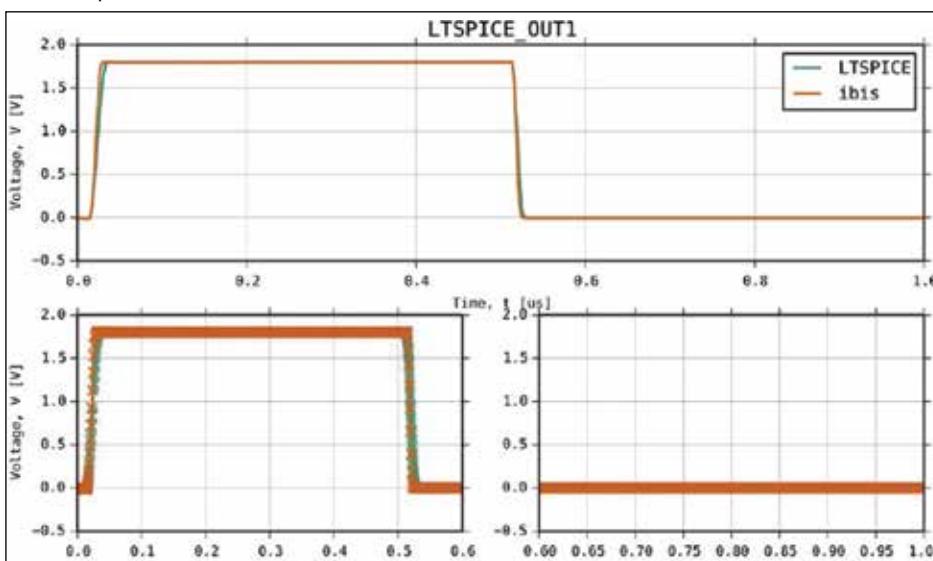

瞬態響應曲線根據 C\_load 測量得出。我們比較 LTspice 和 ADS 結果，並將其疊加在一起進行定性 FOM 分析。如圖 34 所示，LTspice 和 ADS DOUT1 的響應非常相似。可以使用曲線和度量來量化它們之間的差異。計算 1  $\mu$ s 瞬態時間內曲線下的面積。計算得出的曲線面積度量為 99.79%，滿足設定的  $\geq 95\%$  的通過測試條件。所以，DOUT1 IBIS 模型與 SPICE 模型相關。

圖 32: 用於檢測 DOUT1 相關性的 SPICE 測試台

圖 33: ADS OUT1 相關性測試台。

圖 34: LTspice 與 IBIS 模型 OUT1 回應。

### DIN1 和 EN

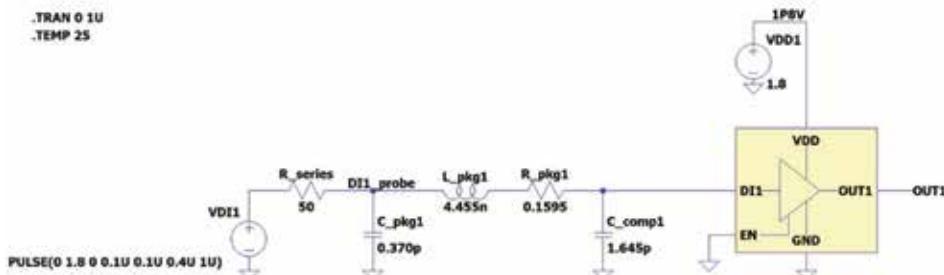

在驗證輸入埠時，透過定性 FOM 和曲線面積度量來關聯 LTspice 和 ADS 的瞬態響應曲線。LTspice 中的測試台如圖 35 所示。這適用於 DIN1 和 EN 接腳。與 DOUT1 一樣，將擷取的 C\_comp 置於 DIN1 埠位置，後接 RLC 封裝寄生效應。然後，連接 50 Ω R\_series 電阻，該電阻後接輸入刺激脈衝電壓電源。測量回應的探頭點在 DIN1\_probe 位置。

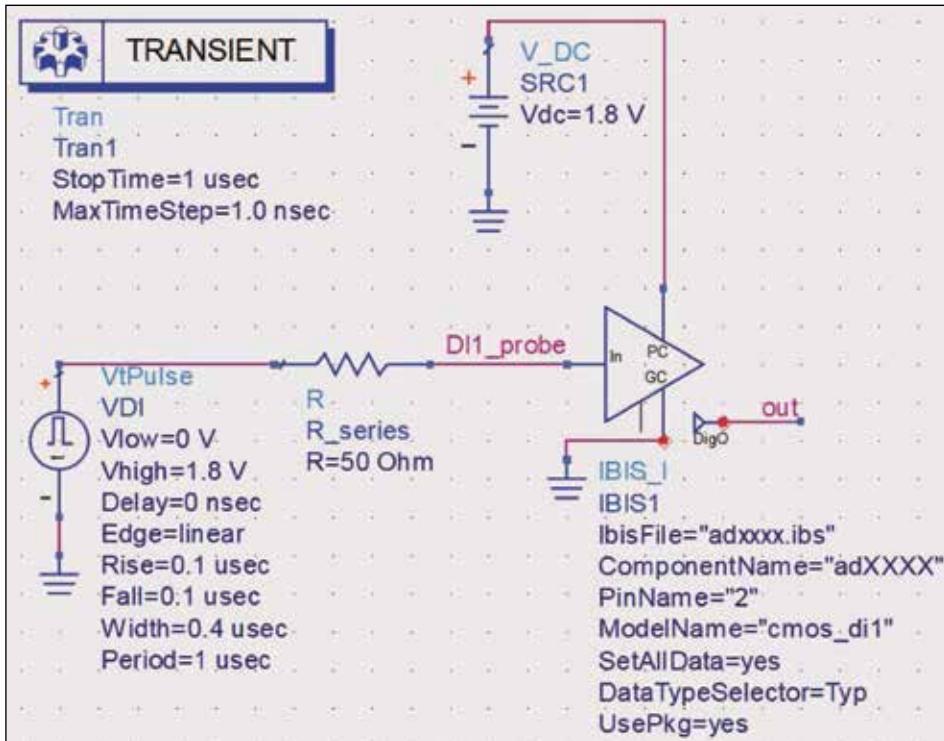

用於驗證輸入埠的 Keysight ADS 測試台如圖 36 所示。同樣，在輸入埠前放置一個 R\_series 50 Ω 電阻，並使用相同的輸入脈衝刺激。此處未顯示 C\_comp 和 RLC 寄生效應，因其已經包含在 IBIS 模組中。用於測量瞬態響應的探頭位於 DI1\_probe 位置。

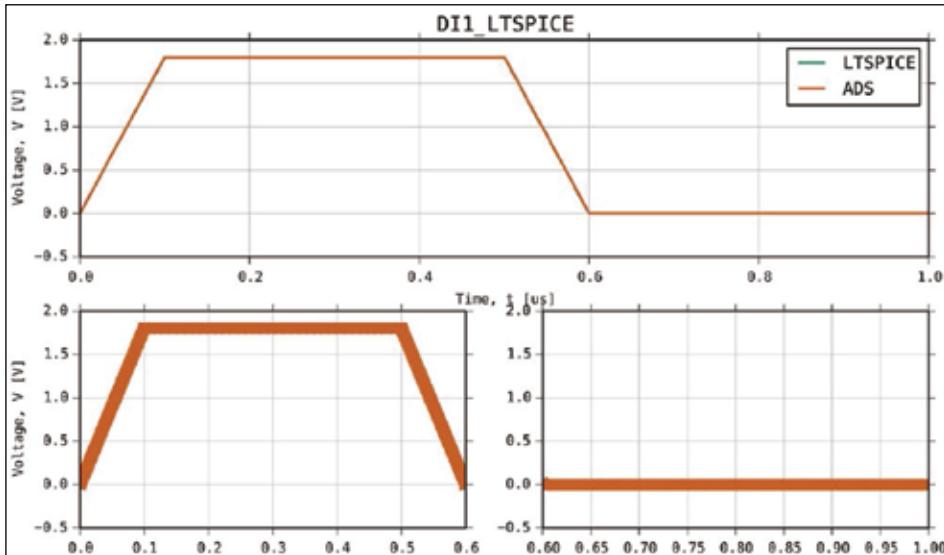

將 LTspice 和 ADS 的瞬態響應曲線疊加在一起進行 FOM 定性測試。如圖 37 所示，曲線是相同的，LTspice 曲線完全與 ADS 曲線重疊。計算得出的 DI1 的曲線面積度量為 100%，滿足所設定的  $\geq 95\%$  的通過測試條件。EN 接腳相關性結果也提供了相同的圖形和曲線面積度量。

圖 35:LTspice DI1 相關性測試台。

圖 36:ADS DI1 相關性測試台。

圖 37:LTspice 與 IBIS 模型的 DI1 回應。

## 總結

本文介紹如何使用 LTspice 來提取數據和建構 IBIS 模型。並提出透過定性 FOM 和曲線面積度量的定量 FOM 將 IBIS 模型與參考 SPICE 模型關聯起來的方法。如此便可以讓使用者確信 IBIS 模型的行為與 SPICE 模型類似。儘管還有本文未介紹其他類型的數字 IO，但提取 C\_comp、I-V 數據和 V-T 數據的程式可以作為創建其他類型 IO 模型的基礎。

您可以免費下載和安裝 LTspice，並開始創建自己的 IBIS 模型。

## 參考電路

- Casamayor, Mercedes。『AN-715 應用筆記：走近 IBIS 模型：什麼是 IBIS 模型？它們是如何產生的？』ADI，2004 年。

- IBIS。I/O 緩衝器精度手冊。IBIS 開放論壇，2000 年 4 月。

- Roy Leventhal 和 Lynne Green。半導體建模：用於訊號、功率和電磁完整性模擬。Springer，2006 年。

- Michael Mirmak、John Angulo、Ian Dodd、Lynne Green、Syed Huq、Arpad Muranyi、Bob Ross。IBIS 建模手冊 (IBIS 4.0 版)。IBIS 開放論壇，2005 年 9 月。 [CTA](#)