提供顯著跳頻 (FH) 優勢

# 下一代軟體定義無線電 (SDR) 收發器

本文深入探討了跳頻 (FH) 的概念，以及如何透過彈性設計 ADRV9002 SDR 收發器的鎖相迴路 (PLL) 架構來實現四大跳頻特性。這些特性可為用戶提供強大的跳頻功能，使其能夠處理單通道和雙通道操作模式下的 Link 16 和快速即時載波頻率負載等應用。此外，跳頻與多晶片同步 (MCS) 和數位預失真 (DPD) 技術的結合使 ADRV9002 SDR 收發器成為一種非常有吸引力的解決方案，可滿足現今複雜通訊系統中的更高要求。

■作者：Michelle Tan / ADI 產品應用工程師

## 簡介

與傳統的無線電通訊不同，跳頻 (FH) 定義了一種透過快速改變載波頻率<sup>1</sup>來發送無線電訊號的方法，Nikola Tesla 在 1903 年的美國專利「訊號傳輸方法」中首次提到了這種方法。後來，在 1942 年，女演員 Hedy Lamarr 和作曲家 George Antheil 進一步鞏固了這一概念，他們從鋼琴的按鍵數量得到啓發，在 88 個頻率之間切換，以防止魚雷的無線電控制受到干擾。一百多年來，從第一次世界大戰中固定指揮點之間的非即時、低速通訊，到當代飛機、艦船和陸地系統之間的即時、高速多媒體通訊，跳頻在軍事領域的應用已進入了一個嶄新的時代。此外，跳頻已廣泛應用於許多無線個人通訊網路，如藍牙個人區域網路 (PAN)，以及消費性電子和業餘無線電領域，如對講機、汽車模型和無人機。

## 什麼是跳頻？

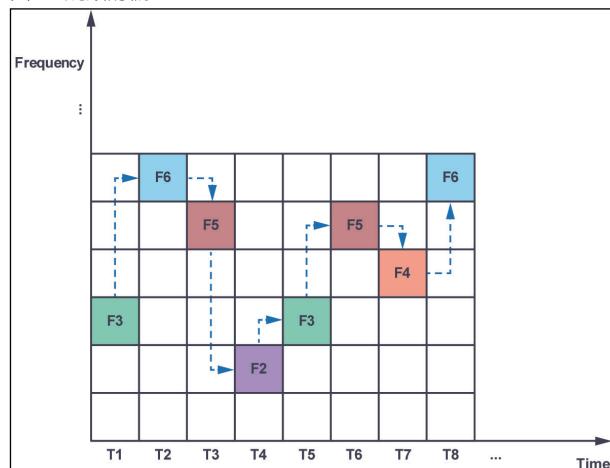

跳頻的概念如圖 1 所示。如果將整個頻段和持續時間劃分為二維網格，那麼在任何給定的時隙，將會使用不同的頻率子頻進行通訊。跳頻模式的隨機性相當於增加了另一個只能在發送器和接收器之間解碼的安全層，使其具有較高的抗窄頻干擾能力，和較強的抗惡意攔截和封鎖的能力。此外，跳頻訊

圖 1：跳頻的概念。

號相互干擾小，可以和其他傳統通訊共用頻寬，實現更高的頻譜效率。隨著跳頻速率加快且使用更多的子頻段，跳頻的優勢變得更加突出，成為對許多不同應用有吸引力的解決方案。

## 下一代 SDR 收發器

ADRV9002 是一款雙窄頻和寬頻 SDR 收發器，提供卓越的 RF 性能和先進的系統功能，例如 DPD 和跳頻。ADRV9002 的工作頻率為 30 MHz 至 6 GHz，覆蓋超高頻 (UHF) 頻段；特高頻 (VHF) 頻段；工業、科學和醫療 (ISM) 頻段和行動通訊頻段。

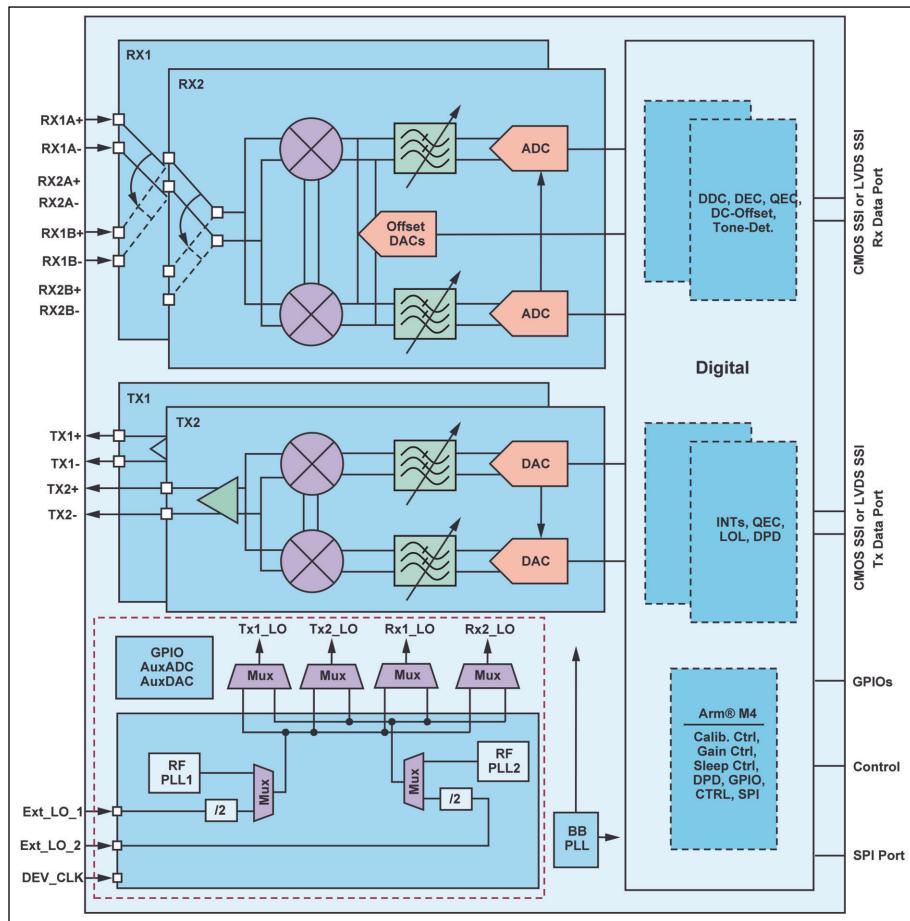

可以支援窄頻 (kHz) 和不超過 40 MHz 的寬頻操作。圖 2 顯示了 ADRV9002 的簡化示意框圖。其中包括發送和接收雙通道，以及一組高階數位訊號處理演算法。許多其他收發器都是將一個 PLL 專用於接收資料路徑，另一個專用於發送資料路徑，而以紅色方框中顯示的 ADRV9002 PLL 結構則比較獨特，它在元件中使用兩個 RF PLL，並且可以選擇將兩個 PLL 提供給任何接收器或發送器使用，兩個一起用或一個都不用。這種彈性是在各種 TDD 應用中支援

圖 2：採用彈性的 PLL 設計的 ADRV9002 簡化示意框圖。

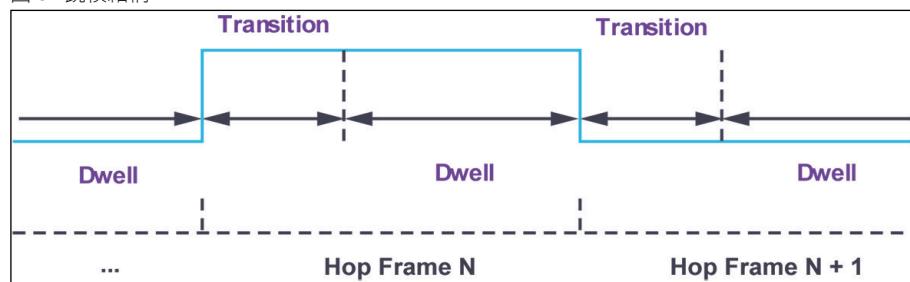

圖 3：跳幀結構。

跳頻的關鍵，例如單通道和雙通道操作，包括僅發送模式 (1T/2T)、僅接收模式 (1R/2R) 和發送 / 接收模式 (1T1R/2T2R)。雙通道操作支援通道分集和通道多工。此外，可以在乒乓模式下使用兩個 PLL，以滿足嚴格的跳頻時序要求。

## ADRV9002 的四大跳頻特性

透過兩個 PLL 多工和 PLL 快速重新調諧實現特快速跳頻

跳頻是透過在切換到不同頻率之前重新調諧 PLL 來實現的。ADRV9002 根據 PLL 的使用情況提供不同的跳頻模式。

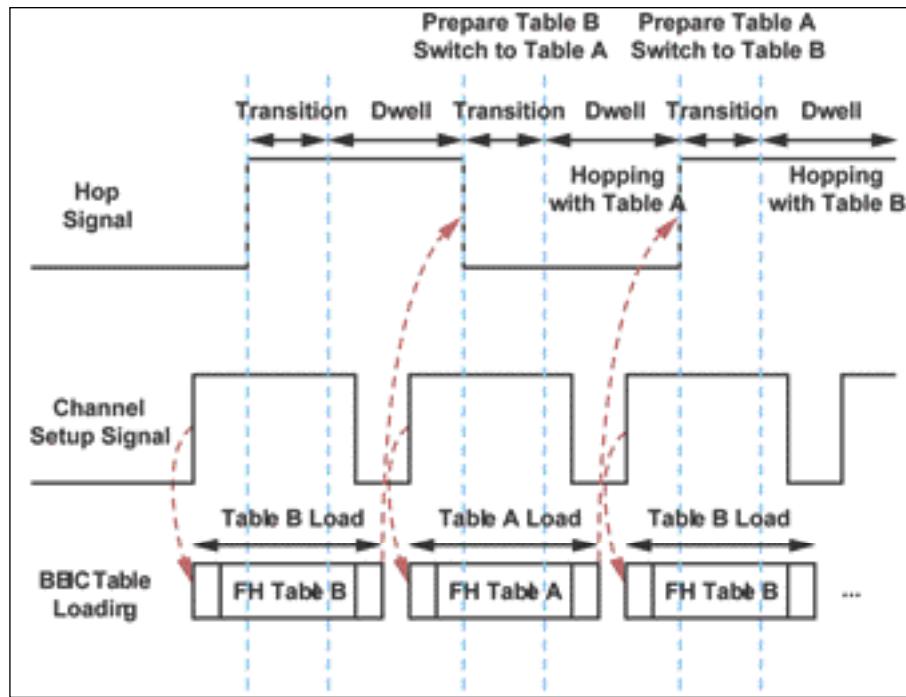

<sup>2</sup> 圖 1 中的每個時隙代表一個跳幀，可以分為一個轉換時間段和一個停留時間段，如圖 3 所示。

在較慢的跳頻模式下，如果頻率變化之間的轉換時間夠長 (比通道設定時間和所需的 PLL 調諧時間長)，則 TDD 操作中的一對發送和接收通道只需要一個 PLL (稱為一個 PLL 重新調諧模式)。為了實現更快的跳頻和更短的轉換時間 (比通道設定時間和所需的 PLL 調諧時間短)，在元件中則可以使用兩個鎖相迴路 (稱為兩個 PLL 多工模式)。兩個 PLL 以乒乓方式相互協調：當一個 PLL 用於目前頻率時，另一個 PLL 則重新調諧至下一個頻率。這樣就可以實現快速跳頻，從而大幅縮短不同頻率變化之間所需的轉換時間。表 1 總結了這兩種模式。

如表 1 所示，要選擇兩種模式中的哪一種，由用戶定義

表 1:DRV9002 跳頻模式 (基於 PLL 的使用情況)

| 跳頻模式     | 轉換時間        | 通道對的 PLL | 允許的 PLL 重新調諧時間  |

|----------|-------------|----------|-----------------|

| PLL 多工   | <PLL 重新調諧時間 | 兩個 PLL   | < 兩次轉換 + 一次停留時間 |

| PLL 重新調諧 | >PLL 重新調諧時間 | 一個 PLL   | < 一次轉換時間        |

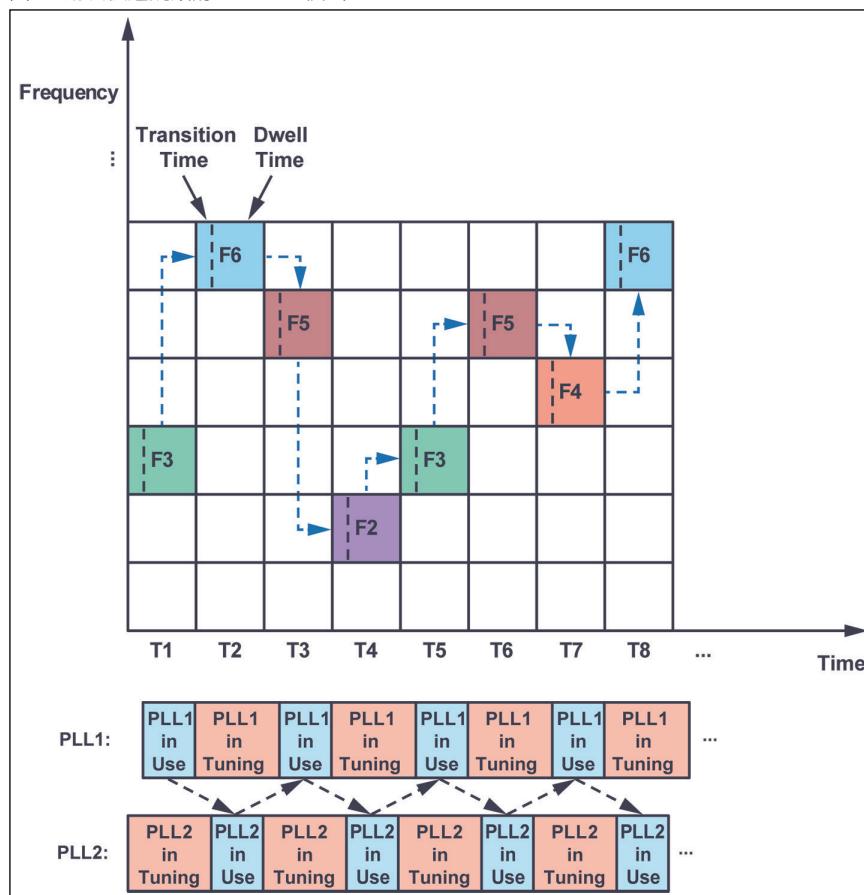

圖 4: 用於快速跳頻的 PLL 多工模式。

的轉換時間決定。

圖 4 進一步解釋了 PLL 多工模式概念。如前所述，每個時隙代表一個跳幀，它由一個轉換時間段和一個停留時間段組成。當一個 PLL 在停留時間內使用時，另一個 PLL 從同一跳幀的轉換時間開始時即開始進行調諧。它可以一直進行調諧，直到下一個跳幀的轉換時間段結束為止。所以，只要所需的 PLL 調諧時間比一次停留時間和兩次轉換時間的總和短，PLL 多工模式就是成功的。

PLL 多工模式下的跳頻對軍事應用來說非常重要，例如 Link 16。Link 16 被認為是北大西洋公約組織 (NATO) 使用的最重要的戰術資料連結標準之一，它使用 960 MHz 至 1.215 GHz 射頻頻段的抗

表 2: 使用快速 PLL 重新調諧模式時的 PLL 重新調諧時間

| PLL 參考時脈速率 (MHz) | PLL 重新調諧時間 (μs) |

|------------------|-----------------|

| 30               | 91              |

| 38.4             | 77              |

| 50               | 56              |

| 100              | 27              |

| 150              | 21              |

| 200              | 20              |

| 250              | 17              |

| 300              | 15              |

干擾高速數位資料連結。<sup>3</sup> 透過在初始化時準確校準整個跳頻範圍，ADRV9002 採用快速 PLL 重新調諧模式來滿足嚴格的時序要求。PLL 重新調諧時間取決於 ADRV9002 PLL 參考時脈速率。表 2 顯示在不同的 PLL 參考時脈速率下所需的快速 PLL 重新調諧時間。PLL 參考時脈速率為 300 MHz 時，快速 PLL 重新調諧時間約為 15 μs。Link 16 的跳幀長度為 13 μs 時，如果轉換時間大於 2 μs，在使用 PLL 多工模式時使用 15 μs 的 PLL 重新調諧時間即可滿足時序要求，具體如表 1 所示。

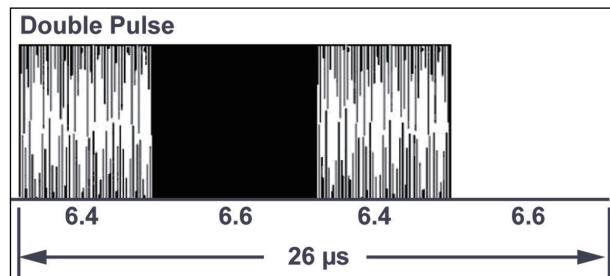

正如論文「在存在窄頻干擾的情況下，透過緩慢、平坦的 Nakagami 衰減通道傳輸的 JTIDS/Link 16 型波形的性能分析」<sup>3</sup> 中所述，Link 16 消息資料可以作為單脈衝或雙脈衝發送，具體由包裝結構決定。單脈衝結構包含 6.4 μs 開啓時間和 6.6 μs 關閉

圖 5: 標準的 Link 16 雙脈衝結構。

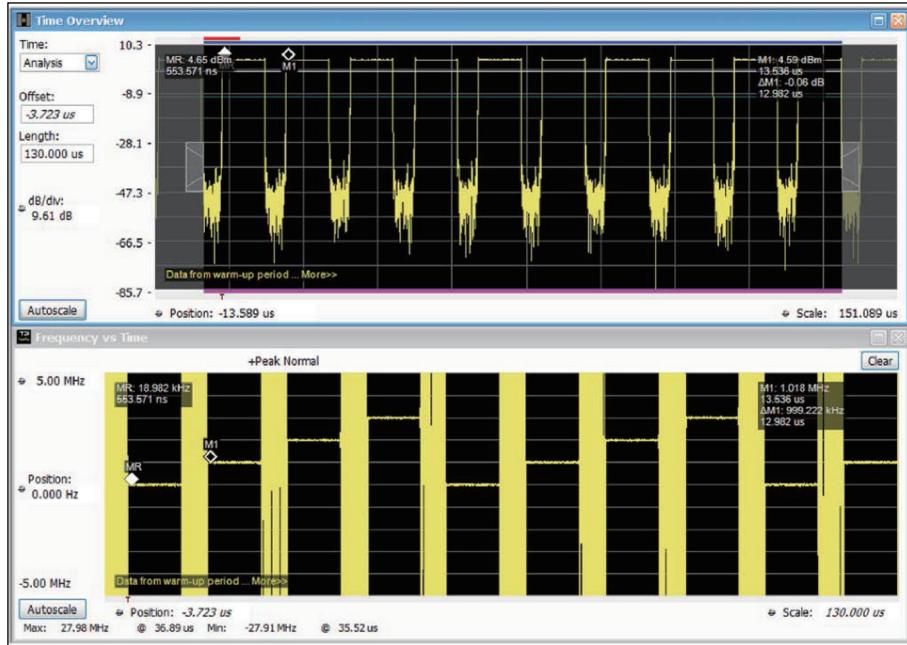

圖 6:Link 16 Tx 跳頻的發送輸出。

時間，總持續時間為  $13 \mu\text{s}$ 。雙脈衝結構由兩個單脈衝組成，它們傳輸相同的資料，但使用不同的載波頻率，如圖 5 所示。所以，轉換時間大致為  $6.6 \mu\text{s} (>2 \mu\text{s})$ ，因此使用 ADRV9002 實現 Link 16 跳頻完全可行的。

圖 6 顯示 ADRV9002 發送輸出（功率與時間以及頻率與時間之間的關係），採用 Link 16 型跳幀（為簡化起見，僅使用發送跳頻）。注意，為了顯示 ADRV9002 可實現的最短轉換時間，實驗未使用圖 5 中所示的標準 Link 16 脈衝結構，而是開啓時間從  $6.4 \mu\text{s}$  增加到  $11 \mu\text{s}$ ，關閉時間從  $6.6 \mu\text{s}$  縮短到  $2 \mu\text{s}$ 。將 Tektronix RSA306B 頻譜分析儀連接至 ADRV9002 評估板的發送輸出埠，以進行觀察。上方的圖顯示功率與時間的關係。從圖中可以看出，每隔  $13 \mu\text{s}$  就會進行發送跳頻，連續發送跳幀之間的轉換時間大約為  $3 \mu\text{s}$ 。下方的圖顯示頻率與時間的關係。在這個實驗中，發送載波頻率以  $1 \text{ MHz}$  的步長在四個不同的頻率之間迴圈。正如預期的一樣，下方的圖證實了發送輸出也以  $1 \text{ MHz}$  的步長在四個不同的頻率之間迴圈，並且在整個停留時間段內都具備出色的頻率精度。

透過使用更先進的測試設備（例如 Keysight

E5052B 和 R&S FSWP）可以進一步測量 Link 16 跳頻的頻率精度。在表 3 所示的測量示例中，發送載波頻率在  $400 \text{ MHz}$ 、 $400.1 \text{ MHz}$ 、 $400.2 \text{ MHz}$  和  $400.3 \text{ MHz}$  時跳頻。發送輸入訊號也相應的同步變換頻率從而使所有跳幀產生  $400 \text{ MHz}$  的頻率輸出。測量持續時間設定為  $100 \mu\text{s}$ ，其中包括 7 個完整的跳幀。每隔  $128 \text{ ns}$  測量一次頻率。可以看出，在停留時間開始時，PLL 已經完全鎖定。停留時間期間的頻率誤差取決於相位雜訊性能。表 3 顯示這 7 個連續跳幀的平均、

最大和最小頻率偏移（輸出頻率和  $400 \text{ MHz}$  之間的絕對差值）性能。在大多數幀中，平均頻率誤差低於  $1 \text{ ppm}$ 。數十次實驗顯示出同樣的結果。注意，測量值可能因設備和測試配置而異。

ADRV9002 還提供了用戶微調 PLL 遷路濾波器頻寬的能力。當 PLL 遷路濾波器頻寬配置為  $1200 \text{ kHz}$  時，可以實現表 3 所示的性能。較大的 PLL 濾波器頻寬可以減少 PLL 重新調諧時間，確保在停留時間開始前 PLL 完全鎖定。建議用戶進一步評估其應用中所需的相位雜訊性能來選擇最合適的遷路濾波器頻寬。

表 3:Link 16 跳頻的頻率精度性能

| 跳幀編號 | 平均頻率誤差 (Hz) | 最大頻率誤差 (Hz) | 最小頻率誤差 (Hz) |

|------|-------------|-------------|-------------|

| 1    | 348         | 730         | 46          |

| 2    | 424         | 997         | 4           |

| 3    | 267         | 563         | 20          |

| 4    | 327         | 892         | 7           |

| 5    | 253         | 569         | 2           |

| 6    | 394         | 903         | 12          |

| 7    | 253         | 677         | 17          |

## 使用靜態和動態的方式載入高達 128 個不同頻率的跳頻表

ADRV9002 對所有跳頻模式使用跳頻表概念。<sup>2</sup> 跳頻表中的每一項包含了跳幀的頻率和其他指令引數。跳頻表可以是靜態載入的，這表示它在初始化期間載入，之後不允許即時更改。它也可以是動態載入的，即在執行跳頻期間載入；在這種情況

下，使用者可以即時更改表的內容。

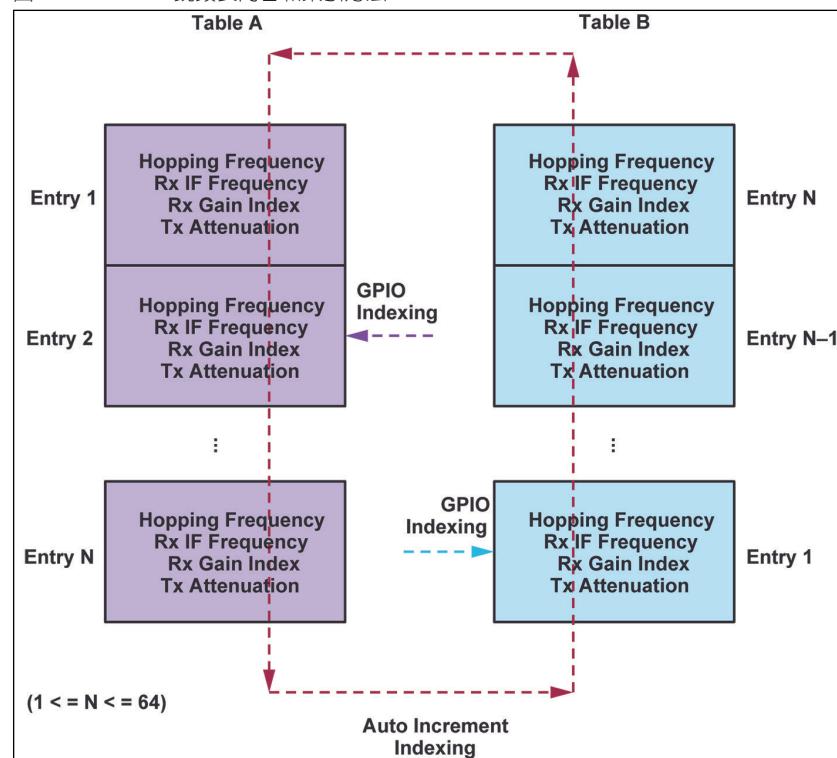

此外，還使用了類似乒乓的概念，因此用戶可以選擇性地載入兩個不同的表，每個表包含最少 1 個、最多 64 個項。在一個表用於目前跳幀時，載入另一個表，準備用於下一個跳幀。每個項都會通知 ADRV9002 關於某個跳幀的配置。可以透過自動遞增索引方式（如果是兩個跳頻表，則是從第一個表的第一項開始，到第二個表的最後一項，然後重新回到第一個表的第一項，如果是一個跳頻表，則是連續迴圈），或透過數位 GPIO 指示的特定項對跳頻表進行隨時索引。

圖 7 顯示跳頻表 A 和 B，每個包含 N 個項 ( $1 \leq N \leq 64$ )。表中的每個項包含 4 個重要參數：跳頻、中頻（僅用於接收 IF 模式）、接收增益表的索引，以及發送衰減。在 TDD 操作中，用戶必須透過專用的通道設定訊號（每個發送通道一個，每個接收通道一個）來通知 ADRV9002 為每個跳幀啓用了哪個通道（發送或接收）。所以，儘管跳頻表中的每項同時包含接收和發送參數，但只會使用相關參數。

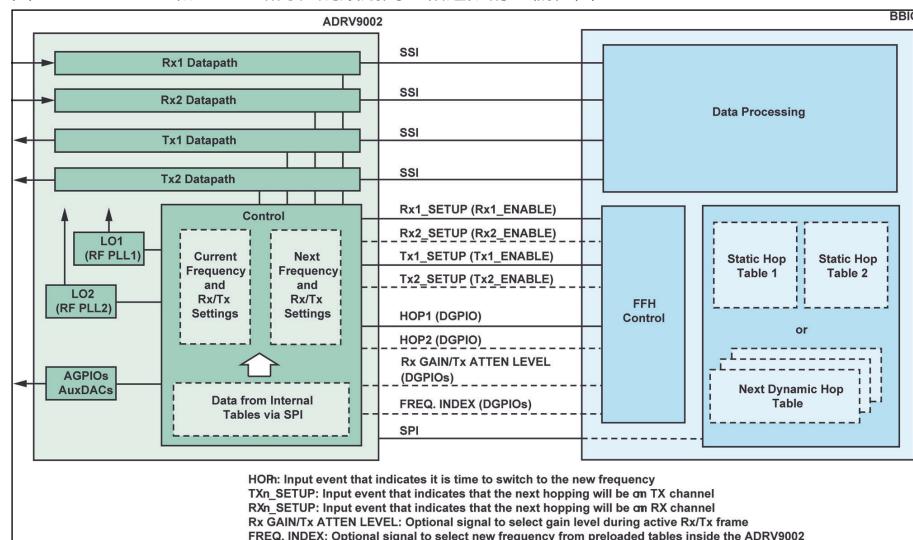

在進一步探討如何在跳頻模式中使用跳頻表之前，需要先瞭解 ADRV9002 和基頻積體

電路 (BBIC) 之間的大致的通訊方式。

如圖 8 所示，BBIC 作為跳頻操作的主要部分，會設定跳頻模式、通道設定訊號 (Rx1\_ENABLE、Rx2\_ENABLE、Tx1\_ENABLE 和 Tx2\_ENABLE)、HOP 訊號 (HOP1 和 HOP2)，以及靜態或動態跳頻表（包含跳頻、接收 IF 頻率、接收增益表的索引和發送衰減）。BBIC 透過 SPI 介面或 GPIO 與

圖 7: ADRV9002 跳頻表內容和索引方法。

圖 8: ADRV9002 和 BBIC 如何在跳頻期間互相通訊的大概框圖。

HOPr: Input event that indicates it is time to switch to the new frequency

TXn\_SETUP: Input event that indicates the next hopping will be on TX channel

RXn\_SETUP: Input event that indicates the next hopping will be on RX channel

Rx GAIN/Tx ATTEN LEVEL: Optional signal to select gain level during active Rx/Tx frame

FREQ. INDEX: Optional signal to select new frequency from preloaded tables inside the ADRV9002

圖 9: 在 PLL 多工模式下，動態的使用跳頻表載入一個頻率的示例。

ADRV9002 通訊。ADRV9002 作為一個節點接收來自 BBIC 的訊號，然後相應配置資料路徑和 LO 進行跳頻。

圖 9 所示為一個動態表示例，每個跳頻表 A 和 B 僅載入一個頻率。這是一種極端情況，允許使用

者即時更改每個幀的跳頻。本示例使用 PLL 多工模式。如圖 8 所示，跳頻訊號的上升邊緣和下降邊緣定義跳幀的時序邊界，如之前所述，每個跳幀由轉換時間和停留時間組成。通道設定訊號上升邊緣定義一個幀延遲（在 PLL 多工模式下，這種延遲是必要的）之後的跳框架類型。

注意，通道設定訊號既可以表示發送設定訊號，也可以表示接收設定訊號。圖 9 顯示了該訊號的簡化版本示意圖。由於 TDD 操作同時涉及發送和接收，使用者需要分別配置發送設定訊號和接收設定訊號。

除了指示跳框架類型，通道設定訊號還可以用來觸發 BBIC 進行跳頻表載入。跳頻表載入應在通道設定訊號下降邊緣之後的那個跳頻訊號邊緣之前完成，然後 PLL 在同一跳頻訊號邊緣開始調諧到該頻率，並為由下一個跳頻邊緣指示的下一個跳幀做好

圖 10: 用動態載入跳頻表的方法每次載入 4 項和 8 項的跳頻結果比較。

準備。表 A 和表 B 以乒乓模式運行，這樣載入完成後，一個表的頻率用來進行跳頻操作，同時對另一個表的頻率進行調諧。

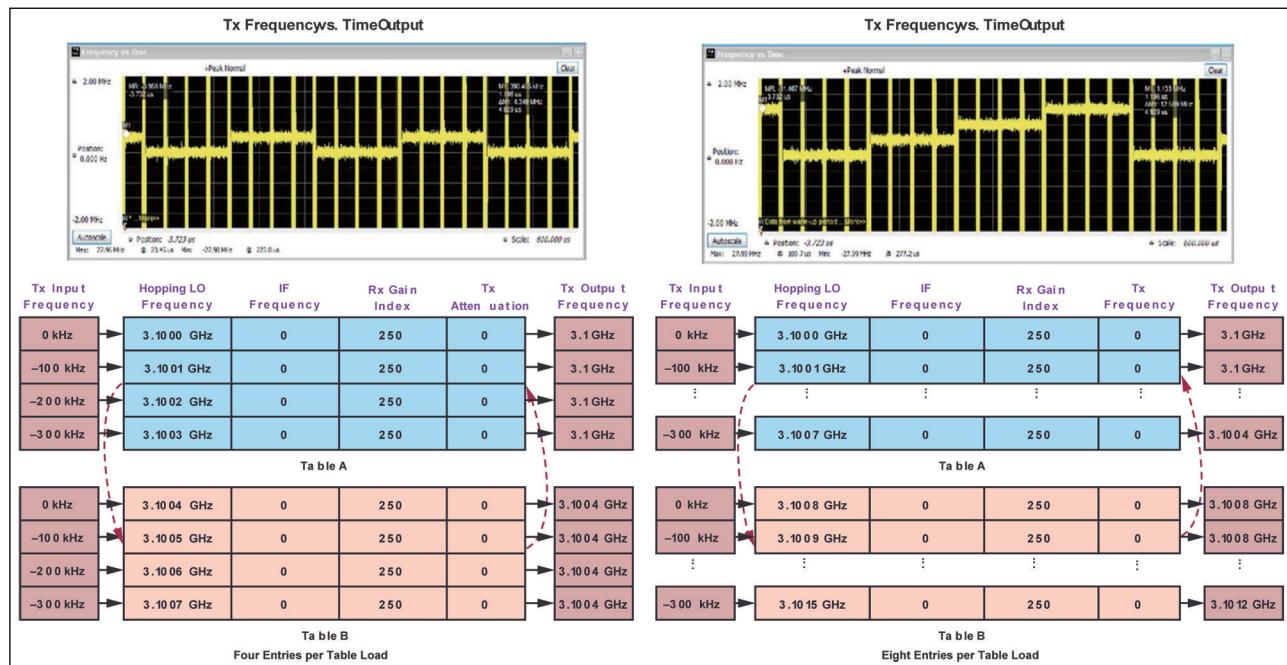

圖 10 顯示透過動態方式使跳頻表每次載入 4 個項和 8 個項時發送輸出頻率與時間之間的關係。發送輸入具有 0 kHz、-100 kHz、-200 kHz 和 -300 kHz 頻率的 4 個幀，並透過連續迴圈這些幀將其饋送到 ADRV9002。它與跳幀完全匹配和同步，所以 0 kHz 輸入幀對應 3.1 GHz LO。跳頻期間，當 LO 變更為下一頻率，發送輸入頻率也變更為下一頻率。

在執行跳頻時，動態載入表 A 和表 B (為了簡化和便於觀察，每次載入時表內容不改變)。對於每次載入 4 項，在 3.1 GHz 輸出頻率會看到四個連續的發送輸出幀，然後在 3.1004 GHz 輸出頻率也會看到四個連續的發送輸出幀，然後以這種模式循環重覆。對於每次載入 8 項，在 3.1 GHz 輸出頻率會看到四個連續的發送輸出幀，在 3.1004 GHz 輸出頻率 4 個連續幀，在 3.1008 Hz 輸出頻率四個連續

圖 11：透過 TES 配置跳頻。

## FH Mode Configuration

**Internal LO1 (Hopping)**

|                        |           |

|------------------------|-----------|

| PLL1 Power Consumption | Low Power |

| LO1 Optimization       | Automatic |

| PLL1 Calibration       | Fast      |

**Configuration**

|                         |                |    |

|-------------------------|----------------|----|

| Shortest Frame Duration | 60             | μs |

| Transition Time         | 30             | μs |

| Hop Mode                | MUX Preprocess |    |

| Table Index Control     | Ping Pong      |    |

| Hop Pin 1               | Pin 00         |    |

| Hop Pin 2               | Unassigned     |    |

Dynamic Table Load (requires Automated TDD)

Number of Hops per Dynamic Table Load

Our FPGA and evaluation software constrain the number of hops per dynamic table load. The product does not.

**Internal LO2 (Hopping)**

|                        |           |

|------------------------|-----------|

| PLL2 Power Consumption | Low Power |

| LO2 Optimization       | Automatic |

| PLL2 Calibration       | Fast      |

**Channels**

|                                                 |                                      |

|-------------------------------------------------|--------------------------------------|

| <input checked="" type="checkbox"/> Rx1 Enabled | <input type="checkbox"/> Rx2 Enabled |

| <input checked="" type="checkbox"/> Tx1 Enabled | <input type="checkbox"/> Tx2 Enabled |

**Bounds of Operation**

|                   |                      |                          |

|-------------------|----------------------|--------------------------|

| Carrier Frequency | Minimum<br>310000000 | Maximum<br>3101500000 Hz |

| Rx Gain Index     | 250                  | 250                      |

| Tx Attenuation    | 0                    | 0 dB                     |

| HoppingTable Configuration      |                          |               |                     |  |

|---------------------------------|--------------------------|---------------|---------------------|--|

| Hop Table A: ADRV9001_FH_CUST01 |                          |               |                     |  |

| Carrier Frequency (Hz)          | Rx Offset Frequency (Hz) | Rx Gain Index | Tx Attenuation (dB) |  |

| 3100000000                      | 0                        | 250           | 0                   |  |

| 3100100000                      | 0                        | 250           | 0                   |  |

| 3100200000                      | 0                        | 250           | 0                   |  |

| 3100300000                      | 0                        | 250           | 0                   |  |

| Hop Table B: ADRV9001_FH_CUST01 |                          |               |                     |  |

|---------------------------------|--------------------------|---------------|---------------------|--|

| Carrier Frequency (Hz)          | Rx Offset Frequency (Hz) | Rx Gain Index | Tx Attenuation (dB) |  |

| 3100400000                      | 0                        | 250           | 0                   |  |

| 3100500000                      | 0                        | 250           | 0                   |  |

| 3100600000                      | 0                        | 250           | 0                   |  |

| 3100700000                      | 0                        | 250           | 0                   |  |

## GPIO Configuration

Control Hopping by GPIO

|                       |                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table Index Sequence  | <input type="text" value="hop-table-index-sequence"/> <small>(Uploading a sequence of integers corresponding to row indices in the hop tables)</small> |

| Table Select Sequence | <input type="text" value="switch-sequence-l-to-entire"/> <small>(Uploading a sequence of A and B or 0 and 1 to switch tables)</small>                  |

| Gain / Attenuation    | <input type="text" value="gain-after-sequence=0-1"/> <small>If enabled, upload a sequence of row indices in gain/attenuation table</small>             |

Our FIFO will log GPIO pins to set the log table, hop table index, and gain / attenuation table index according to a sequence you upload. In the real use case, you control the pins in real-time.

Executed Sequence

| Hop Table | Hop Index | Gain / Attenuation | Carrier (Hz) | Gain | Attenuation (mDB) |

|-----------|-----------|--------------------|--------------|------|-------------------|

| A         | 00        | 000                | 3100000000   | 255  | 12000             |

| A         | 01        | 001                | 3100000000   | 252  | 12500             |

| A         | 10        | 010                | 3100000000   | 248  | 13000             |

| A         | 11        | 011                | 3100000000   | 245  | 13000             |

| B         | 00        | 100                | 31004000000  | 240  | 13500             |

| B         | 01        | 101                | 31004000000  | 237  | 14000             |

| B         | 10        | 110                | 31006000000  | 235  | 14000             |

| B         | 11        | 111                | 31007000000  | 232  | 14000             |

| A         | 00        | 200                | 31007000000  | 225  | 12000             |

GPIO Pins for Control of Hop Table

|                          |                                       |

|--------------------------|---------------------------------------|

| Table Select Pin         | <input type="text" value="Pin 04"/>   |

| Table Index Pin 1        | <input type="text" value="Pin 05"/>   |

| Table Index Pin 2        | <input type="text" value="Pin 06"/>   |

| Table Index Pin 3        | <input type="text" value="Unsigned"/> |

| Table Index Pin 4        | <input type="text" value="Unsigned"/> |

| Table Index Pin 5        | <input type="text" value="Unsigned"/> |

| Table Index Pin 6        | <input type="text" value="Unsigned"/> |

| Gain / Attenuation Pin 1 | <input type="text" value="Pin 01"/>   |

| Gain / Attenuation Pin 2 | <input type="text" value="Pin 02"/>   |

| Gain / Attenuation Pin 3 | <input type="text" value="Pin 03"/>   |

## TDD Timing Configuration

Enable Automated TDD State Machine for FPGA.

### TDD Configuration

Choose an existing TDD configuration: **LTE\_40M\_TX\_ONLY\_FH\_DUAL\_HOP.json**

|                                                                                                                                                                                        |                                                                                   |                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|

| <b>Frames and Sequences</b><br>Frame Duration: <b>143987</b> Clock Cycles<br>Sequencing of Frames: <b>Repeat one sequence forever</b><br>Number of Frames in Sequence: <b>3</b> Frames | <b>TDD Clock</b><br>TDD Clock Rate: <b>200 MHz</b><br>TDD Period: <b>5.000 ns</b> | <b>DMA Sync</b><br><input type="checkbox"/> Enable DMA Sync |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|

---

| Enable                                                   | Signal            | Sync to Sample        | Primary Asset | Secondary Asset | Primary Frame Deassert | Secondary Frame Deassert | Secondary Frame Assert | GPIO                              | X                                 |

|----------------------------------------------------------|-------------------|-----------------------|---------------|-----------------|------------------------|--------------------------|------------------------|-----------------------------------|-----------------------------------|

| <input checked="" type="checkbox"/>                      | Tx1 Pin           | <input type="radio"/> | 10            | 170969          | 72000                  | 143989                   | 0                      | 3                                 | <input type="checkbox"/> (Unused) |

| <input checked="" type="checkbox"/>                      | Tx2 Pin           | <input type="radio"/> | 36910         | 107969          | 35991                  | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | CirTx Pin         | <input type="radio"/> | 70341         | 107969          | 35991                  | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | CirRx Pin         | <input type="radio"/> | 112248        | 37247           | 0                      | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | Tx1 DMA           | <input type="radio"/> | 94717         | 2143            | 2210                   | 74142                    | 0                      | 3                                 | <input type="checkbox"/> (Unused) |

| <input checked="" type="checkbox"/>                      | Tx2 DMA           | <input type="radio"/> | 112248        | 12429           | 36219                  | 110142                   | 0                      | 3                                 | <input type="checkbox"/> (Unused) |

| <input checked="" type="checkbox"/>                      | CirTx DMA         | <input type="radio"/> | 70341         | 12429           | 0                      | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | CirRx DMA         | <input type="radio"/> | 112248        | 37247           | 0                      | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | Hop Pin           | <input type="radio"/> | 3207          | 12426           | 0                      | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | Hop Pin 1         | <input type="radio"/> | 2247          | 12426           | 0                      | 0                        | 3                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | SMA1 Trigger      | <input type="radio"/> | 12159         | 12200           | 0                      | 0                        | 1                      | <input type="checkbox"/> (Unused) |                                   |

| <input checked="" type="checkbox"/>                      | Antenna Selection | <input type="radio"/> | 13150         | 12200           | 0                      | 0                        | 1                      | <input type="checkbox"/> (Unused) |                                   |

| <b>GPIO Trigger</b> <input type="button" value="Apply"/> |                   |                       |               |                 |                        |                          |                        |                                   |                                   |

幀，以及 3.1012 GHz 輸出頻率四個連續幀，然後以這種模式循環重覆。圖 8 所示的發送輸出證實動態表載入操作如預期完全一致。

# 使用雙通道來實現通道分集與通道多工

如圖 2 所示，ADRV9002 支援發送和接收雙通道。可以對兩個通道應用跳頻，以實現通道分集或通道多工。

要實現分集，需使用同樣的 PLL (一個或兩個)、同樣的跳頻表和 TDD 時序配置使兩個通道同時跳頻。用戶可以啓用 ADRV9002 提供的 MCS 功能，確保同一個或不同 ADRV9002 元件上的多個通道彼此完全同步，以保證確定性延遲。還可以透過 MCS 實現相位同步，但必須在每次 PLL 重新調諧頻率時執行相應操作。通過 MCS，實現了多個通道在跳頻期間的同步，使 ADRV9002 成為對涉及跳頻

的 MIMO 分集應用而言非常具吸引力的解決方案。瞭解在跳頻期間使用 MCS 的要求和限制的更多詳細資訊，請參閱 ADRV9001 系統開發使用者指南。<sup>2</sup>

對於通道多工，每對發送和接受通道使用一個 PLL，彼此獨立執行跳頻。其中一個限制是特快跳頻（要求為一個發送和接收通道對配備兩個 PLL）無法用於使一個 ADRV9002 元件的兩對通道進行多工。

除了 2T2R 模式，值得一提的是：ADRV9002 還支援 1T2R 和 2T1R 的跳頻操作，因而可以更彈性滿足用戶的特定要求。

## 支援跳頻與 DPD 操作同時進行

ADRV9002 並支援窄頻和寬頻應用的 DPD 操作。它在實現符合標準的相鄰通道功率洩漏比 (ACPR) 性能的同時，修正功率放大器 (PA) 的非線性，從而明顯提升功率放大器的效率。

ADRV9002 的一個進階功能是 DPD 可以和跳頻一起執行。在這種情況下，ADRV9002 允許使用者配置多達 8 個頻率區域，而 DPD 演算法為每個頻率區域創建一個優化解決方案。針對每個區域，DPD 解決方案作為一組係數，可以分別在傳輸開始和結束時進行儲存和載入。這可以確保在整個跳頻範圍內保持 PA 線性度。

由於 DPD 是一個自我調整濾波過程，必須週期性地擷取一組樣本進行係數計算，因此跳幀長度需要夠長才能滿足 DPD 擷取長度要求。但是，如果用戶只使用初始載入的 DPD 係數，無需進行 DPD 更新，則不存在這種限制。

ADRV9002 的追蹤校準通常不會在快速跳頻期間進行。但是，會根據使用者的跳頻配置，基於多

個頻率區域執行初始校準，以實現最佳性能。

## 使用 ADRV9002 收發器評估軟體 (TES) 進行跳頻性能評估

使用者可以透過 ADRV9002 TES 軟體在評估板上充分測試跳頻性能。TES 支援 Xilinx ZC706 和 ZCU102 FPGA 評估板。<sup>2</sup> 如圖 11 所示，可以輕鬆使用跳頻配置頁面來配置跳頻參數，包括跳頻操作模式、跳頻表、GPIO 設定和 TDD 時序等。TES 內建 FPGA 同步功能，因此用戶能夠準確控制 TDD 時序，確保發送或接收幀能完全與跳幀同步。TES 中還提供許多跳頻示例，供用戶進一步分析研究。

## 結論

跳頻是下一代 SDR 收發器 ADRV9002 的先進系統特性之一。ADRV9002 使用兩個 PLL、多種跳頻模式，以及透過彈性載入和索引跳頻表的方法，為用戶提供卓越的跳頻能力，以便因應各種應用並滿足更高系統要求。所有功能都可以透過 ADRV9002 TES 和軟體發展套件 (SDK) 進行全面評估。

## 參考電路

<sup>1</sup> John G. Proakis。數位通訊，第 3 版。McGraw-Hill，1994 年 3 月。

<sup>2</sup> UG-1828 : ADRV9001 系統開發使用者指南。ADI，2021 年 10 月。

<sup>3</sup> Kao Chin-Han。「在存在窄頻干擾的情況下，透過緩慢、平坦的 Nakagami 衰減通道傳輸的 JTIDS/Link 16 型波形的性能分析」。美國海軍研究生院，2008 年。

**COMPOTECHAsia 榆書**

**每週一、三、五與您分享精彩內容**

**<https://www.facebook.com/lookcompotech>**