## Part I :

## 基準電壓雜訊為何非常重要？

■作者：Anshul Shah / ADI 應用工程師

## 介紹

從航空航天和防務、天然氣探勘到製藥和醫療設備製造，這些產業越來越需要能夠實現高於 24 位元解析度的超高精度測量。例如，製藥產業使用高精度實驗室天秤，該天秤在 2.1 g 滿量程範圍內提供 0.0001 mg 解析度，所以需要使用解析度高於 24 位元的類比數位轉換器 (ADC)。校準和測試這些高精度系統對儀器儀錶產業來說是一大挑戰，要求提供解析度達到 25 位元以上、測量精度至少 7.5 數位元的測試設備。

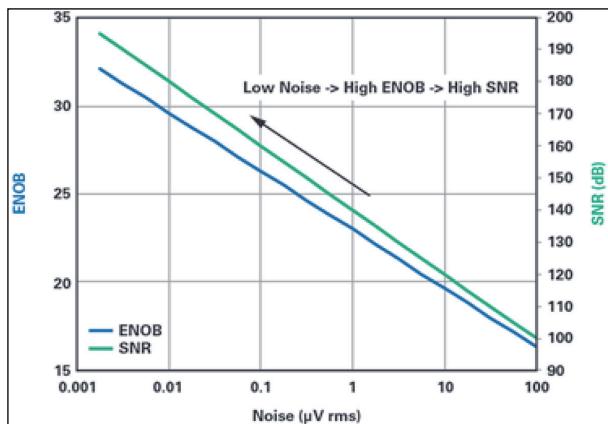

為了實現這種高解析度，需要使用低雜訊訊號鏈。圖 1 顯示雜訊與有效位元數 (ENOB) 和訊號雜訊 (SNR) 之間的關係。注意，雜訊是基於基準電壓 ( $V_{REF}$ ) = 5 V，ADC 輸入設定為滿量程範圍來計算的。舉例來講，要實現 25 位元解析度，或者 152 dB 動態範圍，可允許的最大系統雜訊為 0.2437  $\mu$ V rms。

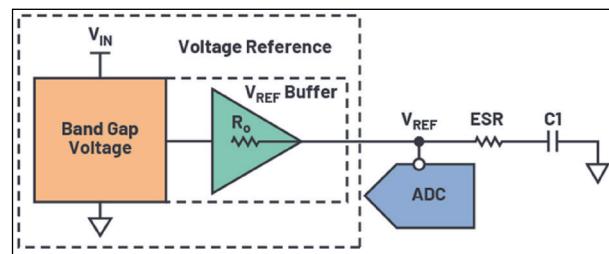

基準電壓設定輸入類比訊號的限值，ADC 可以解析該訊號。公式 1 是 ADC 的理想轉換函數，其中輸出數位碼 (小數形式) 透過類比輸入訊號  $V_{IN}$ 、基

圖 1：雜訊與 ENOB 和 SNR。

準電壓  $V_{REF}$  和 ADC 位數 N 計算得出。

$$ADC\ Code = V_{IN} \times \frac{2^N}{V_{REF}} \quad (1)$$

一般來說，ADC 資料手冊中的解析度是基於輸入短路技術得出，其中 ADC 輸入連接至 GND，或者 ADC 差分輸入連接至共源極。ADC 輸入短路技術有助於確定 ADC 解析度的絕對限值特性，方法是忽略 ADC 輸入源雜訊，消除  $V_{REF}$  雜訊的影響。結果確實如此，因為  $V_{IN}$  設定為 0 V，使得  $V_{IN}/V_{REF}$  比也等於 0 V。

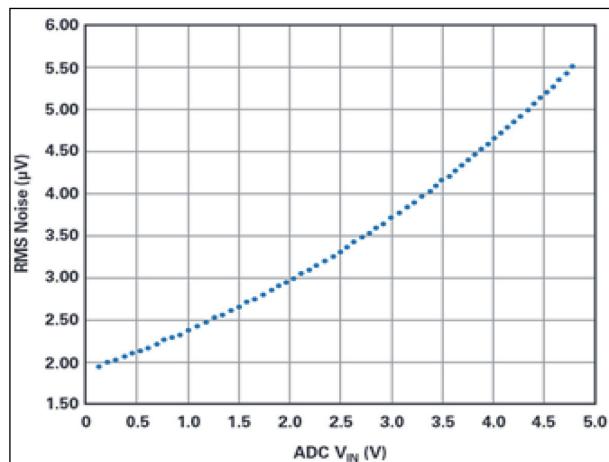

為了研究基準電壓雜訊對整體系統雜訊的影響，圖 2 顯示了總系統雜訊 (rms) 和 ADC 輸入直流源電壓之間的關係。實施本次測試期間，我們使用了 AD7177-2 32 位元 ADC，其  $V_{REF}$  輸入連接至 LTC6655-5?(5 V)，ADC 輸入則連接至低雜訊直流源。ADC 輸出資料速率設定為 10 kSPS。注意，在整個 ADC 輸入電壓範圍內，ADC 雜訊保持恆定 (35 nV/ $\sqrt{Hz}$ )，但 ADC 直流輸入源雜訊增大 ( $\leq 6$  nV/ $\sqrt{Hz}$ )，與基準電壓雜訊 (96 nV/ $\sqrt{Hz}$ ) 相比，仍保持較低水準。如圖 2 所示，總體雜訊與 ADC 直流輸入電壓成正比。這是因為  $V_{IN}$ (5 V)，ADC 輸入則連接至低雜訊直流源。ADC 輸出資料速率設定為 10 kSPS。注意，在整個 ADC 輸入電壓範圍內，ADC 雜訊保持恆定 (35 nV/ $\sqrt{Hz}$ )，但 ADC 直流輸入源雜訊增大 ( $\leq 6$  nV/ $\sqrt{Hz}$ )，與基準電壓雜訊 (96 nV/ $\sqrt{Hz}$ ) 相比，仍保持較低水準。如圖 2 所示，總體雜訊與 ADC 直流輸入電壓成正比。這是因為  $V_{IN}/V_{REF}$  比隨之增大，所以在 ADC 使用滿量程輸入時， $V_{REF}$  雜訊主導整體系統雜訊。訊號鏈中各元件的雜訊會以和方根 (RSS) 的方式疊加，導致曲線形狀如圖 2 所示。

圖 2 : ADC  $V_{IN}$  與 rms 系統雜訊之間的關係。 $V_{REF}$  設定為 LTC6655-5。

為了實現 25 位元或以上的高測量解析度，即使是市面上最好的獨立基準電壓（具備低雜訊規格）也需要獲取一些幫助來衰減其雜訊。添加外部電路（例如濾波器）可以幫助衰減雜訊，以達到所需的 ADC 動態範圍。

本文的其餘部分介紹各種類型的低通濾波器，以及如何使用這些濾波器來衰減基準電壓雜訊。本文還會討論濾波器設計技術和與濾波器有關的取捨。本文將以衰減基準電壓雜訊為基礎，介紹兩種類型的低通濾波器，分別是簡單的被動 RC 低通濾波器 (LPF) 和基於主動訊號流程圖 (SFG) 的低通濾波器。電路性能部分會展示系統評估結果，用  $\Sigma$ - $\Delta$

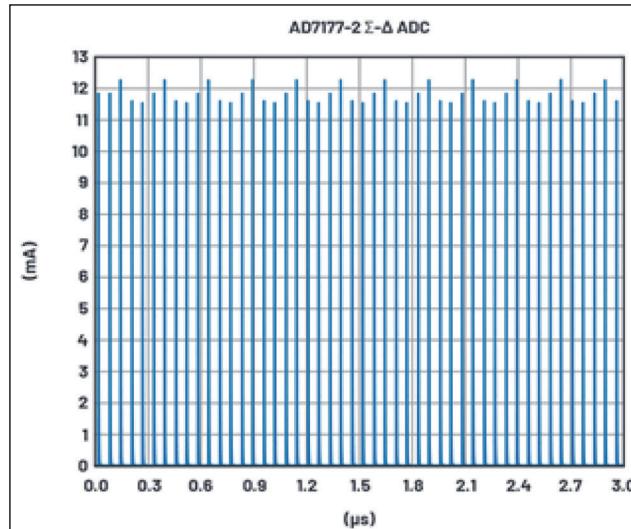

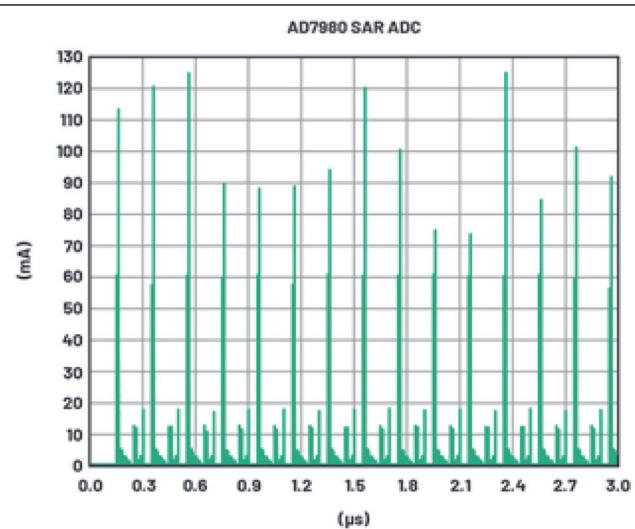

圖 4 : AD7177-2 和 AD7980 類比動態基準電流回應。

ADC 表示測試。

### 使用被動低通濾波器來降低雜訊

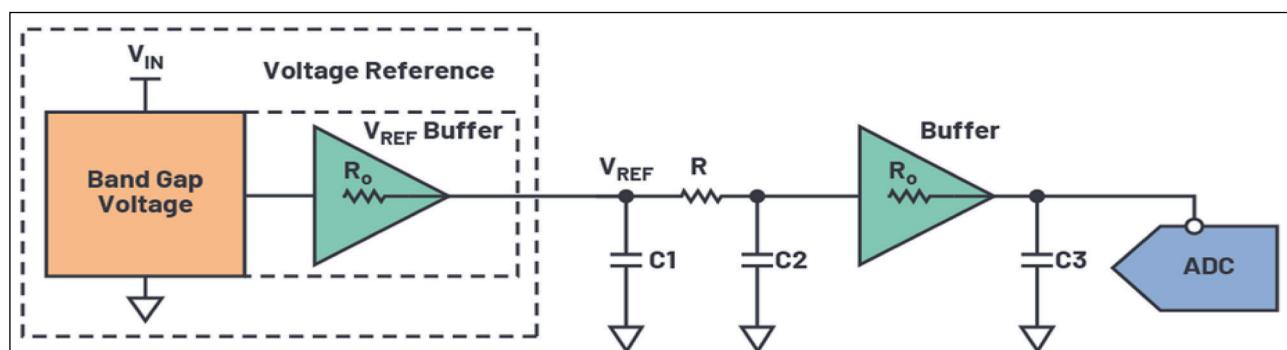

圖 3 顯示基準電壓透過低通濾波器驅動 ADC，該濾波器採用了外部儲能電容  $C_1$ 、儲能電容的等效串聯電阻 (ESR)，以及基準電壓運算放大器 (運放) 的輸出阻抗。 $R_o$

$$f_C = \frac{1}{2\pi R C} \quad (2)$$

從公式可以看出，頻寬與電阻  $R$  和電容  $C$  成反比。

從公式可以看出，頻寬與電阻  $R$  和電容  $C$  成反比。

儲能電容  $C_1$  也可以用於本地電源記憶體，用於補償 ADC 基準電壓電路突然要求負載電流發生變化時產生的電壓尖峰。圖 4 顯示  $\Sigma$ - $\Delta$  ADC AD7177-2 和 SAR ADC AD7980 動態基準電流回應。

用戶可以選擇  $C_1$  電容的值來滿足 LPF 截止頻率要求，但是有些 SAR ADC 要求基準輸入端採用至少  $10 \mu\text{F}$  電容，以保證正常運行。最小的  $10\mu\text{F}$   $C_1$  電容可以降低基準電壓源緩衝器的相位餘裕。隨著

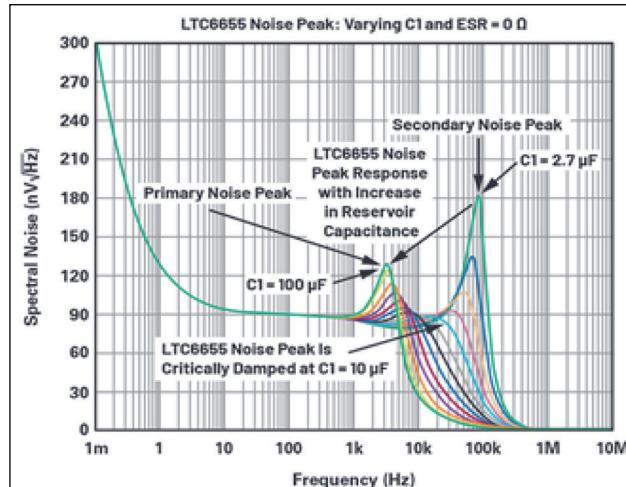

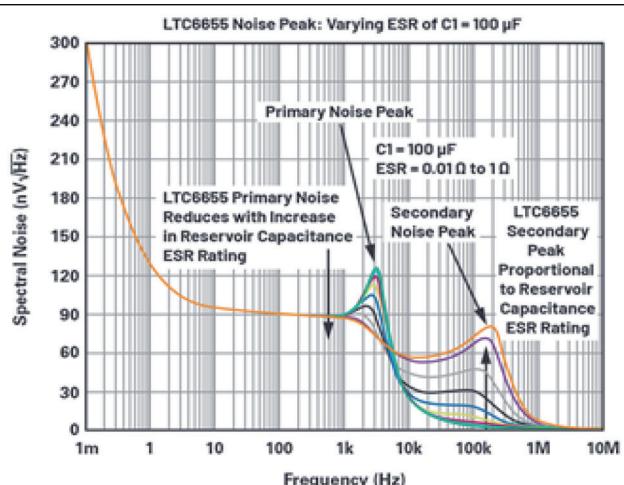

相位餘裕降低，緩衝器回饋不再為負。1 在單位增益交叉頻率附近的訊號與輸入訊號同相回饋。1 這導致閉迴響應在交叉頻率附近出現雜訊峰值。1 由於源自截止頻率 ( $-3\text{ dB}$  點) 的頻寬最高達到  $16\text{ MHz}$ ，總整合雜訊 (rms) 由雜訊峰值主導。即使基準電壓儲能電容  $C_1$  作為雜訊濾波器使用，並補償電壓尖峰，也需注意雜訊峰值。圖 5 顯示 LTC6655 基準電壓的雜訊峰值，該峰值因儲能電容  $C_1$  引起。雜訊峰值幅度由儲能電容的值和其 ESR 額定值決定。

大多數基準電壓都具備複雜的輸出級，以驅動適用於 ADC 基準電壓源電路的大型負載電容。例如，LTC6655 輸出級設計用於採用設定為  $10\text{ }\mu\text{F}$  的儲能電容來執行關鍵衰減。LTC6655 的儲能電容設定為最小  $2.7\text{ }\mu\text{F}$ 、最大  $100\text{ }\mu\text{F}$  時，會產生雜訊峰值。

$V_{\text{REF}}$  輸出儲能電容的等效串聯電阻會消除主要的雜訊峰值，但是會在  $100\text{ kHz}$  和以上頻率時產生二次雜訊峰值。究其原因，可能是因為電容的 ESR

圖 5：LTC6655 基準電壓雜訊峰值密度。

圖 6：被動 RC LPF，後接緩衝器。

產生零雜訊，可以改善相位餘裕和降低主要雜訊峰值。但是，這個零雜訊與 LTC6655 固有的零雜訊結合在一起，產生了二次雜訊峰值。注意，圖 5 所示的雜訊響應只適用於 LTC6655 基準電壓源。

過濾基準電壓雜訊、消除雜訊峰值，以及合理驅動 ADC 的另一種解決方案是增加被動 RC LPF，然後增加緩衝器。透過增加緩衝器，我們可以隔離 LPF 和 ADC 基準電壓源輸入電容之間的設計限制。請參見圖 6。

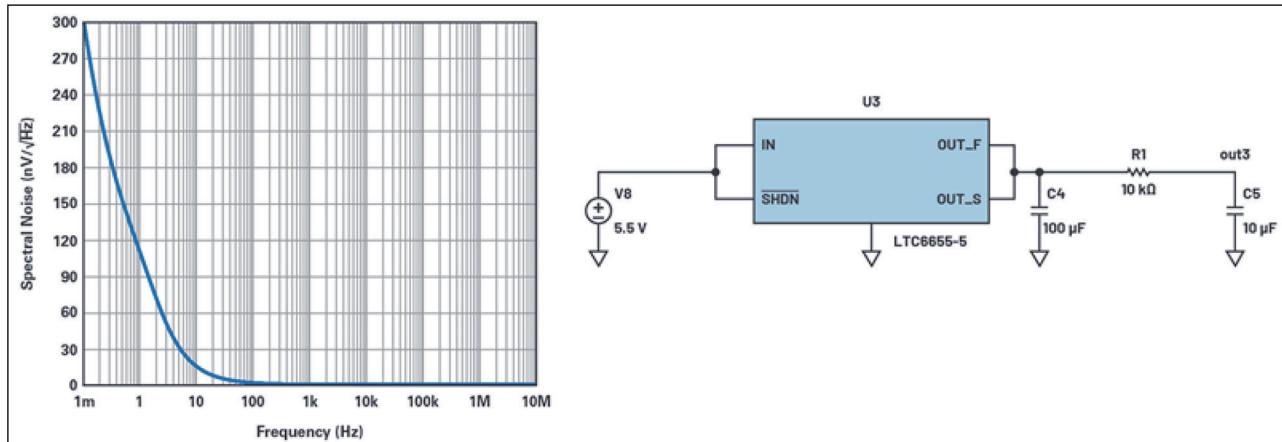

將被動 RC LPF 截止頻率設定為遠低於單位增益交越頻率，不止可以降低寬頻和低頻率雜訊，還可以避免出現雜訊峰值。例如，圖 7 顯示 LTC6655 雜訊回應，其中  $C_1 = 100\text{ }\mu\text{F}$  ( $\text{ESR} = 0\text{ }\Omega$ )，後接被動 LPF，其中  $R = 10\text{ k}\Omega$ 、 $C_2 = 10\text{ }\mu\text{F}$  ( $\text{ESR} = 0\text{ }\Omega$ )，在  $1.59\text{ Hz}$  時產生極點。

增大低通濾波器電阻  $R$  可以協助實現低截止頻率，但是也可能會降低精密基準電壓的直流精度。

圖 7:LTC6655-5，後接被動 RC LPF 雜訊響應。

增加被動 RC LPF 時，使用者還必須考慮對負載調整和  $V_{REF}$  緩衝器回應 ( $\tau = RC$ ) 的影響，在驅動 ADC 時，這會影響其瞬變性能。

要達到所需的瞬變性能，建議如圖 6 所示使用緩衝器。選擇緩衝器時，要考慮的關鍵規格包括超低雜訊、支援高負載電容的能力、低失真、傑出的壓擺率，以及寬增益頻寬。建議採用的緩衝器為 ADA4805-1 和 ADA4807-1。

## 使用主動 LPF 降低雜訊

表 1 指明了所需的動態範圍和必須滿足的可允許最大系統雜訊要求，以實現所需的 ENOB ADC 解析度。根據表 1 條件： $V_{REF} = 5$  V，ADC 輸入設定為滿量程範圍

| ENOB | SNR (dB) | 雜訊 (μV rms) |

|------|----------|-------------|

| 20   | 122.16   | 7.798301    |

| 21   | 128.18   | 3.89942     |

| 22   | 134.2    | 1.949845    |

| 23   | 140.22   | 0.97499     |

| 24   | 146.24   | 0.487528    |

| 25   | 152.26   | 0.243781    |

| 26   | 158.28   | 0.121899    |

| 27   | 164.3    | 0.060954    |

| 28   | 170.32   | 0.030479    |

| 29   | 176.34   | 0.015241    |

| 30   | 182.36   | 0.007621    |

| 31   | 188.38   | 0.003811    |

| 32   | 194.4    | 0.001905    |

低精密基準電壓的直流精度。但是，基於主動元件設計更高階的 LPF 可以在輸入和輸出之間提供良好的隔離，大幅避免基準電壓直流精度下降，並提供低輸出阻抗來驅動 ADC 的基準電壓源路。

$$SNR = 6.02N + 1.76 \text{ dB} \quad (3)$$

$$LSB = \frac{V_{REF}}{2^N} \quad (4)$$

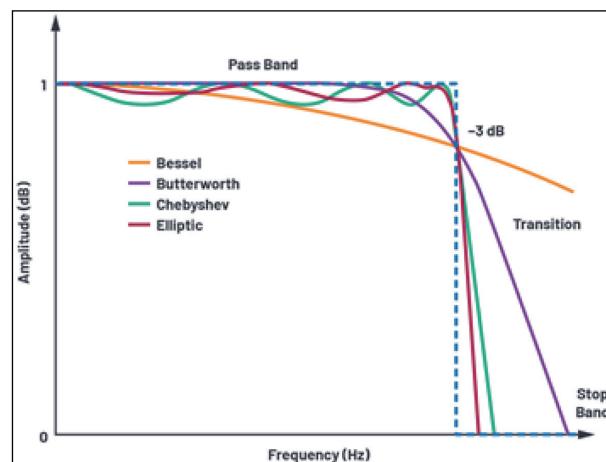

圖 8: 濾波器振幅回應示意圖。

現在提供幾種不同類型的主動低通濾波器，例如，Bessel、Butterworth、Chebyshev 和 elliptic，具體如圖 8 所示。採用平坦帶通或無漣波帶通，可以大幅地避免降低精密基準電壓的直流精度。在所有濾波器類型中，基於 Butterworth 拓撲的 LPF 設計可以實現平坦的帶通和陡峭的衰減。

(下期待續…)