# FPGA 技術 用於先進視頻處理解決方案

■文：Achronix

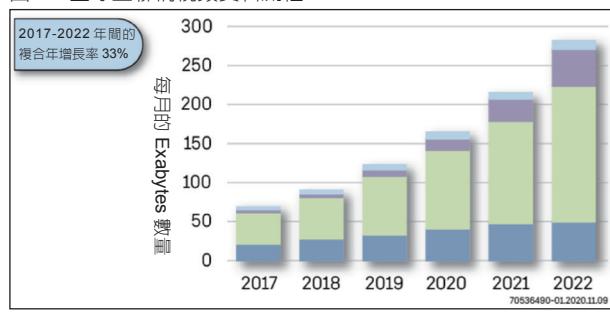

部署先進的網路基礎設施不僅可以解決資料傳輸量激增的問題，而且還能在諸如邊緣、核心和雲端等網路的不同部分進行資料處理。不足為奇的是大部分數據要麼是視頻，要麼是圖像，並且這些資料正以指數級速度增長，並將在未來幾年内保持持續增長。因此，需要更多的計算資源來應對資料的大量增長（如圖 1 所示）。

由於應用的類型多種多樣，因此在資料中心中存在著各種各樣的視頻或影像處理工作負載。基於專用積體電路 (ASIC) 的解決方案通常可提供更高的性能，但是無法進行升級以支援未來的演算法；基於中央處理器 (CPU) 的解決方案要比其更加靈活，但其時鐘主頻已經固定，而且已不再可能大幅提升處理器性能；圖形處理器 (GPU) 是提供視頻 / 影像處理解決方案的另一種候選方案，但其功耗明顯高於基於現場可程式設計邏輯閘陣列 (FPGA) 的解決

方案。FPGA 在視頻處理和壓縮領域內，是一種具有吸引力的選擇，因為它們提供了實現創新視頻處理演算法所需的、平衡的資源。此外，FPGA 提供了一種靈活的解決方案，可以縮短產品上市時間，並能在解決方案的整個生命週期內實現持續升級和部署新的功能。

## 基於 FPGA 的視頻解決方案的示例

本文將介紹三種典型的視頻應用，以展示基於 FPGA 的解決方案在廣播行業中的優勢。這些優勢包括縮短處理時間、降低功耗，以及為服務提供者和終端使用者節省成本。

基於 FPGA 的解決方案在以下三種應用中的優勢：

- 視頻流

- 使用視頻編輯軟體來創作視頻內容

- 人工智慧 (AI) 和深度學習 — 圖像識別是該應用的主要部分，其需要高性能的計算資源

## 視頻流傳送

為了使媒體流變得快速和高效，對視頻進行轉碼的需求已急劇增加。目前大多數產品都採用了一種基於軟體的方法，但該方法無法滿足高頻寬、廣播級視頻流的處理要求。視頻流和 / 或雲服務提供者面臨著由基於軟體的解決方案所帶來的低輸送量、高功耗、長延遲和佔用空間大等挑戰。根據思科的一份題為《思科可視網路指數：預測與趨勢——2017-2022 年白皮書》的報告，視頻流資料流程量

表 1：互聯網用戶和資料流程的增長

| 年份   | 互聯網用戶 | 設備與連接 | 寬頻速度      | 視頻資料流程量  |

|------|-------|-------|-----------|----------|

| 2017 | 34 億  | 180 億 | 39.0 Mbps | 占總量的 75% |

| 2022 | 48 億  | 285 億 | 75.4 Mbps | 占總量的 83% |

來源：思科 (Cisco) 公司

圖 1：全球互聯網視頻資料流程

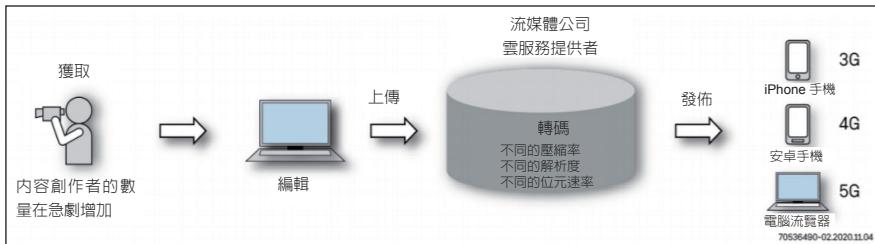

圖 2：視頻轉碼工作流程

正在增加，並且到 2022 年時將佔據整個互聯網資料流程的 82%。在包括視頻點播、流媒體直播和視頻監控等所有應用中，視頻資料流程量將逐年穩步增長。

諸如 Netflix 和 YouTube 等視頻流應用的興起推動了對視頻轉碼的需求。傳統廣播和視頻流媒體之間最顯著的區別在於內容量和頻道數。為了支持從電腦到智慧手機等各種接收設備，內容必須被轉碼成不同的解析度和壓縮格式。因此，視頻流將消耗大量的計算資源。

流媒體和雲服務提供者需要一種解決方案來緩解對計算需求的壓力。Achronix Speedster7t 系列 FPGA 器件中搭載了 IBEX 這種最先進的視頻處理半導體智慧財產權 (IP) 能夠解決這一重大問題。這種基於 FPGA 的解決方案可以提供高輸送量的、低功耗的和佔用空間小的系統，而且無需犧牲靈活性。儘管基於 ASIC 的解決方案功能強大，但只能支持在設計時定義的功能集，而不能支援現場更新。

## 視頻內容創作

在過去，高清解析度 (HD) 格式在視頻內容創作中佔據主導地位。最近，標準解析度已被提升至

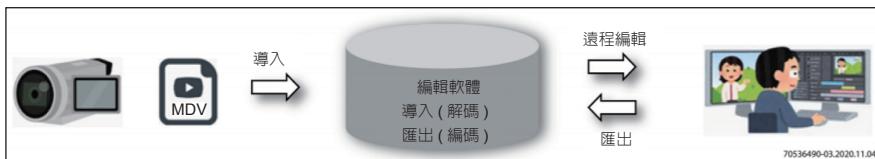

圖 3：視頻編輯工作流程

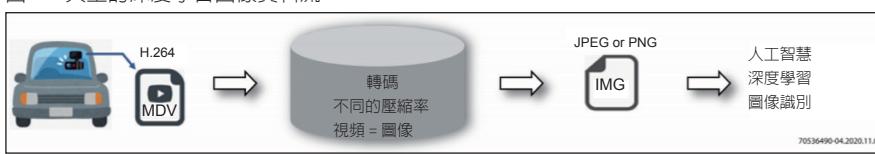

圖 4：典型的深度學習圖像資料流

4K，甚至到 8K，這使得視頻編碼或解碼面臨挑戰。用於這些較高解析度的壓縮格式主要有 Apple ProRes、Avid DNx 和 SONY XAVC。由於這些壓縮格式是專有的，因此 ASIC 或 GPU 並不能原生支援這些格式，而且 CPU 提供的性能也不佳。因此，在較高解析度下創作視頻內容時，FPGA 是最佳的解決方案。

在新的趨勢下，遠端後期製作的概念正變得越來越普遍。然而，現有的電腦並沒有足夠的能力來即時處理高解析度的內容 (例如 8K)。因此，編輯人員開始借助雲基礎設施來獲得更好的計算性能。此外，由於需要保持社交距離，新冠肺炎疫情也加速了這一趨勢。基於雲和 FPGA 的解決方案為編輯人員提供了巨大的好處。Achronix Speedster7t 系列 FPGA 器件進行架構創新，例如二維片上網路 (NoC)，使其特別適合於加速編碼和解碼演算法。

## 人工智慧與深度學習

人工智慧、機器學習和深度學習是衆所周知的領域，它們在過去幾年中得到了迅速的發展。除了這些領域，圖像識別也逐漸成為一個全新的重要領域，這得益於人工智慧 / 機器學習 (AI/ML) 的創新。例如，先進駕駛員輔助系統 (ADAS) 使用深度學習演算法來處理捕獲的圖像。安裝在車上的行車記錄儀使用 H.264 壓縮技術記錄視頻，然後將視頻流轉碼為諸如 JPEG 或 PNG 等合適的圖像格式，以用於深度學習圖像識別。根據應用場景，可以同時完成丟幀、更改解析度或其他影像處理任務。

在零售業的安全攝像頭或物流業的包裹分揀中也有類似的應用案例，其資料流程與上述示例相同 —— 這些應用中的攝像頭使用 H.264 或 H.265 等壓縮比相對較高的壓縮格式記錄視頻，然

後將編碼的視頻流傳輸到雲端或資料中心。在雲端，視頻流由原始格式轉碼為適合深度學習的格式，將視頻檔轉換為圖像資料庫。

從歷史來看，FPGA 一直擅長將電影轉碼為圖像。此外，使用 FPGA 中的深度學習演算法對圖像預先進行預處理，不僅可以提高輸送量，而且還能減少系統級的資料事務量。Achronix Speedster7t 的創新架構及其帶有的專用機器學習處理器 (MLP)，使之成為實現定制的和既定的深度學習演算法的理想選擇。

## FPGA 代表性視頻用例的性能

我們分別使用 FPGA 和 CPU 來實現上述三個典型應用案例，並對一些關鍵指標進行對比，如表 2 所示。

## 視頻流傳輸

在視頻流傳輸應用中，常用的壓縮格式是 H.264 或 H.265，因為終端 (接收端) 設備原生支援這些格式。諸如位深或色度和解析度等參數通常為 8 位、4:2:0 和  $1920 \times 1080$  或  $1280 \times 720$ 。在解碼器方面，基於 FPGA 的實現比基於 CPU 的系統提供更高的輸送量。在資料層面，FPGA 效率更高，因為如果將 CPU 用於純資料處理之外的其他任何與資料相關的任務時，它通常都沒有得到充分的利用。然而在編碼器方面，硬化的 CPU 編碼器內核是專門針對這些典型參數而設計的，並提供了足夠的性能。

表 2：FPGA 與 CPU 的性能比較

| 壓縮格式         |      | 編碼器 | 解碼器 | 備忘錄                                                                                |

|--------------|------|-----|-----|------------------------------------------------------------------------------------|

| H.264, H.265 | 典型參數 | ↓   | ↔   | 典型參數表示 8 位、420、2K。英特爾 QSV、GPU 硬核功能仍然強大，尤其是在編碼器端。                                   |

|              | 次要參數 | ↔   | ↑   | 次要參數表示 10 位、422、3K 或 5K。英特爾 QSV、GPU 硬核不支持它。                                        |

| 幀內           |      | ↑   | ↑   | 專有轉碼器，諸如 Apple ProRes、Avid DNx、SONY XAVC、Panasonic AVC-Intra。圖像格式，諸如 JPEG 和 PNG 等。 |

表注

↑ FPGA 提供更佳的性能。

↔ FPGA 和 CPU 提供同等的性能，但 FPGA 是卸載 CPU 負擔的首選解決方案。

↓ FPGA 和 CPU 提供同等的性能，但 CPU 是首選解決方案。

為了獲得兩全其美的效果，將 FPGA 和 CPU 解決方案相結合，並由 FPGA 來處理繁重的工作負載是理想的解決方案。FPGA 上的高效功能可以被移植到可重新配置的硬體上去運行。例如，運動估計演算法是一種適合 FPGA 的工作負載。另一方面，CPU 更適合處理位元速率控制演算法。

一些服務提供者要求在軟體解決方案中實現與 x264 相同的視頻品質和流媒體格式。FPGA 和 CPU 的組合解決方案可以有效地滿足這些要求。使用這種方法，每種功能都被合理地分配，較繁重的處理負載被轉移到 FPGA，與純軟體解決方案相比，這種方法能提供類似或更好的視頻品質和流媒體格式，而且編碼時間顯著減少。

## 視頻內容創作

用於內容創作的視頻編輯軟體支援多種壓縮格式，其中包括 Apple ProRes、Avid DNx、Sony XAVC 和 Panasonic AVC-Intra，這些格式都帶有基於內幀結構的專有壓縮方案。此外，還有一些支援 RAW 模式的格式，諸如 Apple ProRes RAW、RED RAW、ARRI RAW 和 Blackmagic RAW，這些格式都得到了攝像機製造商的支持。由於這些格式 (以及新型的和不斷出現的格式) 具有不斷變化的特性，因此基於 ASIC 的解決方案並不適用，而需要基於 FPGA 的解決方案。

在過去，主要的解析度為 HD/2K，CPU 具有足夠的速度來處理這些視頻流。但是，隨著 4K 或 8K 解析度變得越來越普遍，僅靠 CPU 加軟體的

解決方案不能夠提供即時處理。另一方面，基於 FPGA 的解決方案可以輕鬆地即時處理 4K 和 8K 解

析度視頻。

內部基準測試表明，即使與中級 FPGA 晶片相

比，基於 FPGA 解決方案的處理速度也比最新的 CPU 加軟體解決方案快五倍。雖然 GPU 可以提供與 FPGA 類似的性能，但其功耗更高、解決方案佔用空間更大。

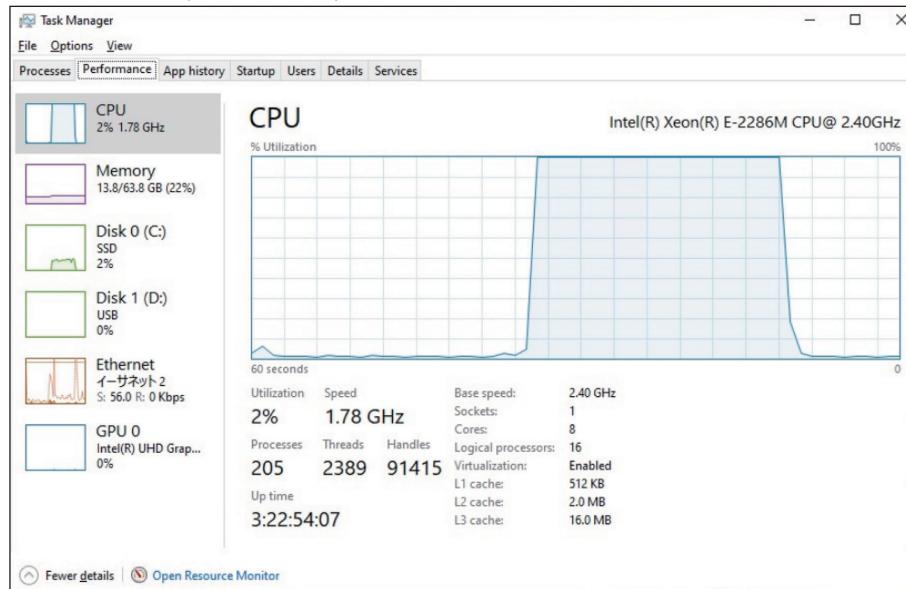

FPGA 解決方案的好處不僅僅在於加速，而且還能降低 CPU 的繁忙程度。在只有 CPU 的解決方案中，所有 CPU 週期都被 4K 或 8K 內容的編碼所消耗，而使用 FPGA 來卸載編碼任務可以釋放 CPU 週期。因此，FPGA 加速器為該應用提供了最佳的解決方案，通過減少 4K 和 8K 視頻製作所需的處理時間，來提高視頻編輯人員的創作效率。

## 人工智慧與深度學習

如前所述，在處理 H.264/H.265 解碼方面，FPGA 提供了與 CPU 相當或更高的性能。如果解碼器和內幀編碼器（例如 JPEG 或 PNG）都位於同一 FPGA 中，那麼基於 FPGA 的解決方案將提供比 CPU 更佳的性能。此外，在深度學習應用

圖 5：僅使用 CPU（無 FPGA 卸載）的處理方案性能

圖 6：使用 FPGA 卸載的 CPU 利用率

圖 7：使用深度學習進行視頻和影像處理的典型資料流程

中，在將圖像資料發送到深度學習處理之前，通常會進行一些圖像預處理。在同一個 FPGA 上可以執行所有的處理，包括解碼、影像處理和編碼等（如圖 7 所示），並且與 CPU 相比，FPGA 可以提供高輸送量、低延遲和更少的資料服務。深度學習技術在現在和未來都將被廣泛應用於各個行業或領域，而基於 FPGA 的解決方案將助力這一發展。

## 針對性能而優化的 Speedster7t 架構

### Speedster7t

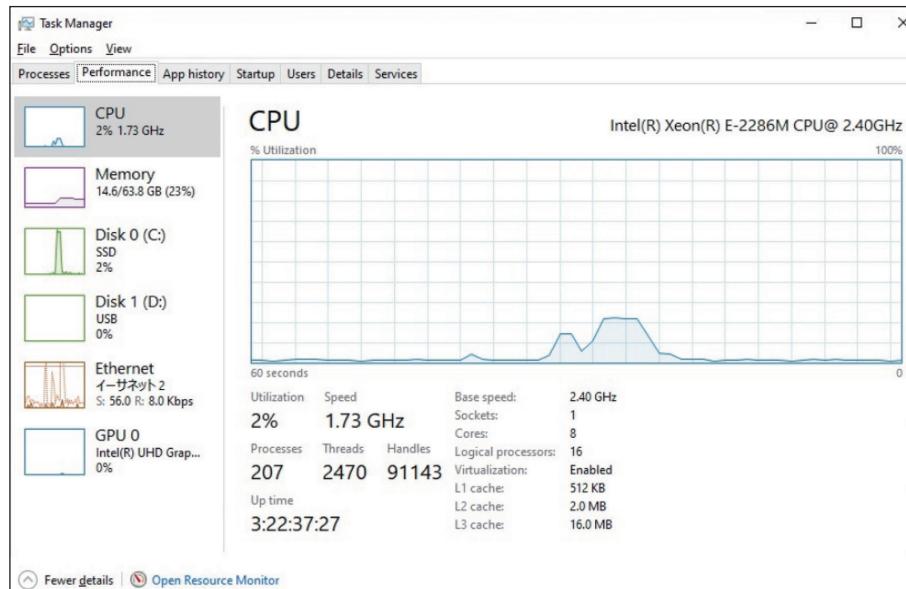

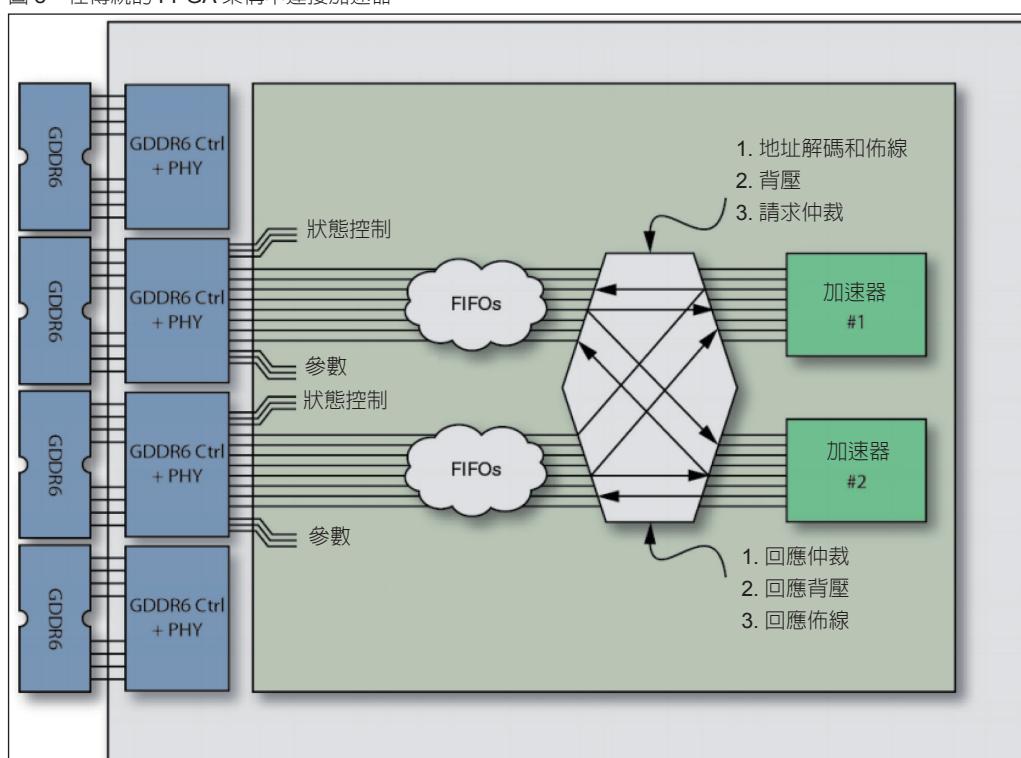

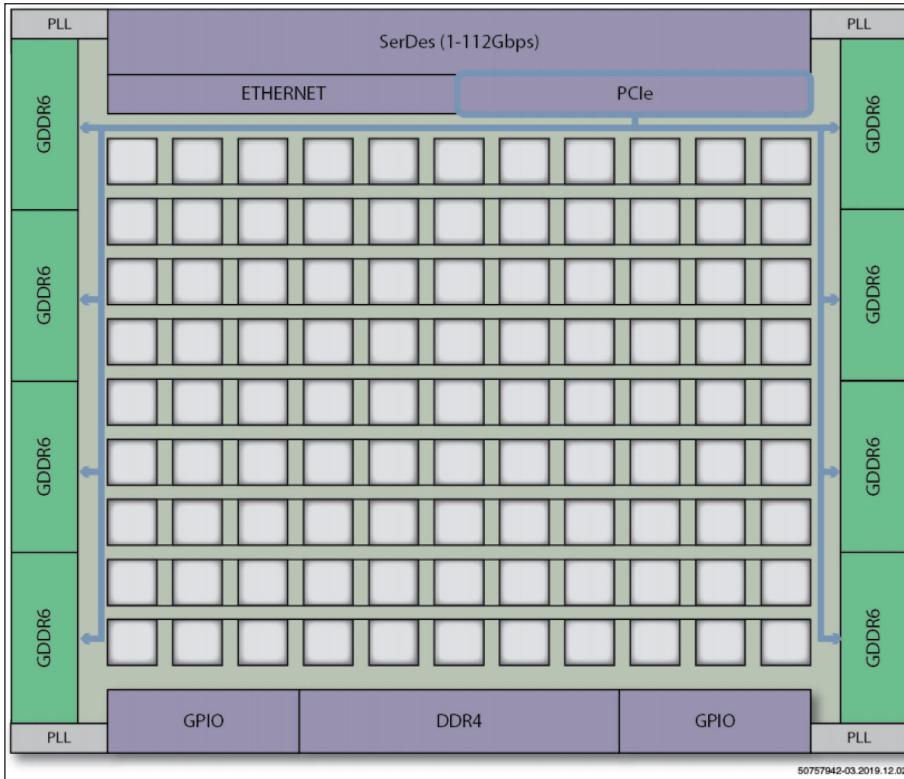

FPGA 是專為滿足最高性能的資料加速應用而設計的，該架構非常適合解決本白皮書中提到的所有應用挑戰。具體而言，Achronix 開發了一種全新的創新型二維片上網路，它力助在 I/O 頻寬、外部存儲頻寬和片上性能之間提供一種平衡架構，以確保總體最高的輸送量。在傳統的 FPGA 架構中，使用者需要設計電路來連接加速器，從而導致並不理想的佈局和佈線。現

在更新的 FPGA 架構使用一種網路，在邏輯陣列內的處理單元與各種片上高速介面和記憶體埠之間傳輸資料流程（如圖 8 所示）。

圖 8：在傳統的 FPGA 架構中連接加速器

圖 9：先進的 FPGA 減少了所需的電路數量

硬連線架構極大地改善了處理的延遲和能效，但是缺乏應對需求變化的靈活性。Speedster7t 系列 FPGA 器件中的第一款晶片 AC7t1500 提供了一系列高速介面，包括可分配的 (fracturable) 乙太網控制器 (支援高達 400G 的速率)、PCI Gen 5 埠和多達 32 個 SerDes 通道，速率高達 112 Gbps。AC7t1500 器件是首款部署多通道 GDDR6 記憶體介面的 FPGA，它滿足了需要快取記憶體海量資料的編碼器的需求。除了在可程式設計邏輯陣列中採用的面向位元的佈線結構外，這些週邊設備還通過一個智慧二維片上網路進行互連。因此，Speedster7t FPGA 是第一款能夠實現上述視頻處理用例的器件，該 FPGA 器件利用一種平衡架構，在計算密度和資料傳輸能力方面帶來重大改進。

Speedster7t 架構通過提供總頻寬超過 20 Tbps 的多級片上網路 (NoC) 層級化結構，消除了由於需要將高速 I/O 通道直接連接到以較低時脈速率運行的可程式設計邏輯所造成的瓶頸。與採用 FPGA 邏輯陣列實現互連方式相比，NoC 不僅在速率上有了大幅的提升，而且 NoC 還能在不消耗任何 FPGA 可程式設計資源的情況下傳輸大量資料。內部 NoC 不僅提供了更高的頻寬，而且 Speedster7t FPGA 中的智慧連接機制也簡化了將資料從 NoC 埠傳輸到邏輯陣列中的任務。

這種架構可支援進一步的設計創新，例如支持上述機器學習用例的面向矩陣的算術單元。通過使用諸如深度學習或較為簡單的統計方法等技術，設備可以分析資料流程的模式，以觀察和增強資料包在網路中的傳輸，並對不斷變化的情況做出快速反應。概括而言，以下三項 Speedster7t 的架構創新為上述用例提供了更好的 FPGA 設計：

## 高速存儲介面

Speedster7t 架構師對存儲介面的選擇反映出了乙太網和 NoC 連接可提供的巨大頻寬。一種可能的方法是在一系列產品設計中採用即將推出的 HBM2 介面。儘管這樣的介面可以提供所需的性能

等級，但 HBM2 是一種價格昂貴的選擇，這將迫使客戶去等待必要的元件和集成技術進入市場。

與此不同，Speedster7t 系列則採用了 GDDR6 標準，該標準為當今片外記憶體提供了最高的性能。Speedster7t FPGA 是市場上首款支援該介面的器件，每個片上 GDDR6 存儲控制器可維持 512 Gbps 的頻寬。在單個 AC7t1500 器件中最多可帶有八個 GDDR6 控制器，因此一個 Speedster7t FPGA 器件可提供高達 4 Tbps 的總存儲頻寬。

## 對 PCIe Gen 5 的支持

除了乙太網和存儲控制器，Speedster7t FPGA 上提供的對 PCIe Gen 5 的支援還能夠與主機處理器緊密集成，以支援高性能加速器應用。PCI Gen 5 控制器使其能夠讀取和寫入存儲在 FPGA 存儲層級結構中的資料，包括許多位於邏輯陣列內的塊 RAM，以及連接到 FPGA 存儲控制器的外部 GDDR6 和 DDR4 SRAM。在 FPGA 邏輯陣列中產生實體的資料傳輸控制器 (例如 DMA 引擎)，可以類似地通過 PCIe Gen 5 匯流排訪問與主機處理器共用的記憶體。無需消耗 FPGA 邏輯陣列內的任何資源即可實現這種高頻寬連接，並且設計階段幾乎為零。

使用者只需啓用 PCIe 和 GDDR6 介面，即可通過 NoC 發送交易資料。

PCIe 子系統與任何 GDDR6 或 DDR4 存儲介面之間的直接連接如圖 10 所示。

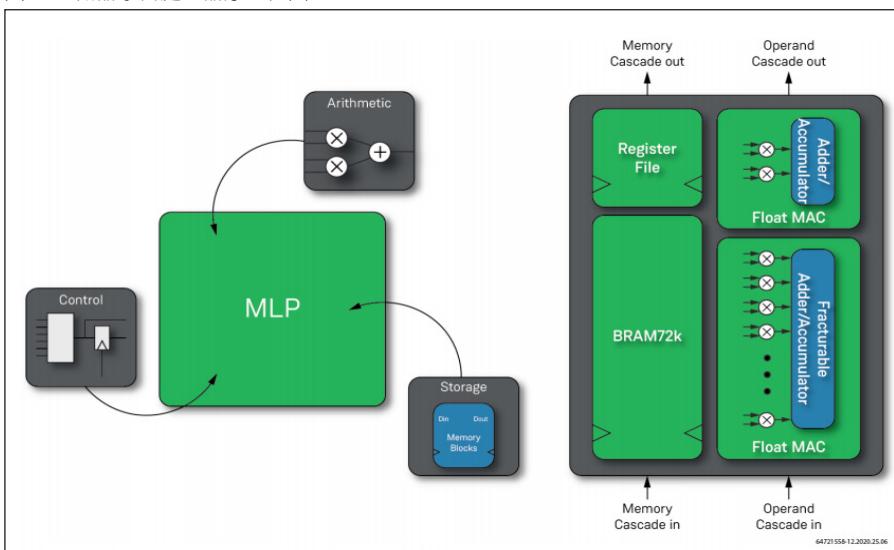

## 機器學習處理器 (MLP)

對於計算密集型任務，在 Speedster7t FPGA 上部署的 Speedster7t 機器學習處理器 (MLP) 是靈活的且可分配的算術單元。機器學習處理器是高密度乘法器陣列，帶有支援多種數位格式的浮點和整數 MAC 模組。機器學習處理器帶有集成的存儲模組，可以在不使用任何 FPGA 資源的情況下執行運算元和存儲級聯功能。機器學習處理器適用於一系列矩陣數學運算，從 5G 無線電控制器的波束成形

圖 10：無需消耗 FPGA 邏輯陣列即可實現 PCIe 和 GDDR6 之間的資料傳輸

圖 11：機器學習處理器原理框圖

計算到加速深度學習應用，如視頻處理系統所需的資料流程模式和資料包內容分析。

## 結論

雖然 ASIC 的性能通常很高，但它只支持設計時設想的功能集，不能進行現場升級；CPU 是最靈活且

最易於設計的，但是其時鐘頻率已經難以提升，其性能大幅提升的時代已經結束；隨著工作負載逐年增加，CPU 已無法滿足需求。FPGA 在性能和靈活性之間提供了良好的平衡。由於需要大量的並行處理，因此視頻編碼、解碼和影像處理演算法都更適合於用 FPGA 來實現。總之，基於 FPGA 的解決方案可以縮短上市時間，具有高度的可定制性，並且可以有效地用於實現不斷發展的演算法。

## IBEX Technology 公司簡介

IBEX Technology 公司總部位於日本，可提供視頻編解碼 IP、IC 設計服務和諮詢，諸如 ASIC 和大規模 FPGA 設計、PCB 等。IBEX 開發了多種視頻轉碼器，諸如 MPEG-2、H.264 / AVC、Apple ProRes、Avid DNxHD、SONY XAVC、Panasonic AVC-Intra 和 H.265 / HEVC。IBEX Technology 公司主要在廣播設備行業有著良好的業績記錄，這得益於其產品的高品質、穩定性和可靠性。

IBEX 於 1985 年在日本神奈川縣 (Kanagawa) 厚木市 (Atsugi) 成立，是公認的大型

積體電路 (LSI) 和視頻系統設計領域的領導者。過去，IBEX 的主要用戶包括日本電視機製造商和廣播公司，並為 ASIC 廠商提供了視頻轉碼器 IP。在過去的十年中，由於 FPGA 的性能和成本競爭力，該公司的重點已轉向提供基於 FPGA 的解決方案。IBEX 面向全球用戶提供 FPGA IP。 [CTA](#)