# 即時 Linux 作業系統

## RISC-V PolarFire SoC FPGA 架構介紹

■作者：Tim Morin

Microchip Technology Inc. 策略行銷總監

這是一個十分吸引人的標題，但它代表的是什麼樣的意思呢？一即時系統的定義，就是以最簡單的方式，在一個確定的週期性來執行。所以確定性是即時系統的首要要求，因為即時系統通常控制著機器。您應該不希望會出現此種狀況：數位控制鑽床在星期二從 A 點移動到 B 點用了 10 毫秒，然而卻在星期三執行同樣的操作時用了 20 毫秒，系統的即時周期產生了差異性。同樣，飛行員的飛行控制系統在所有條件下都應該保證每次都以完全相同的

方式控制飛行曲面。

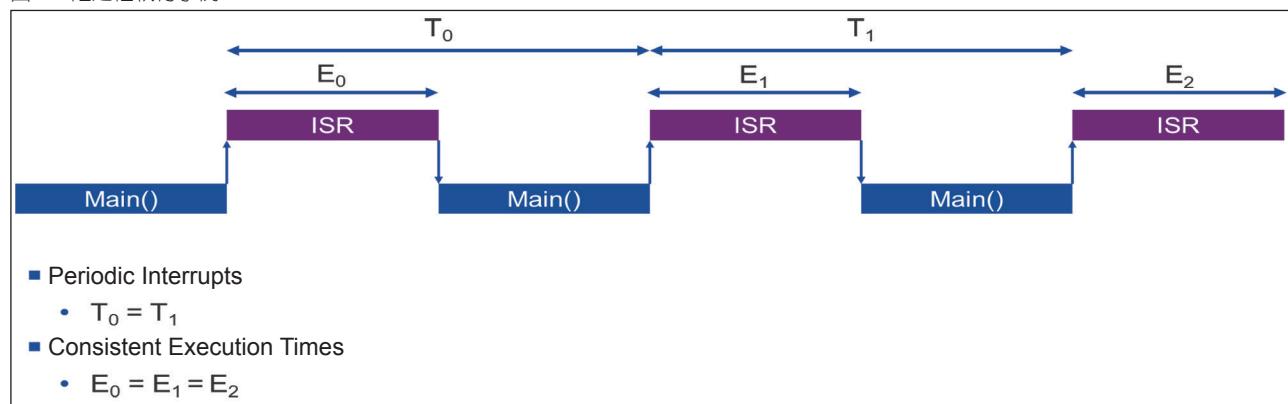

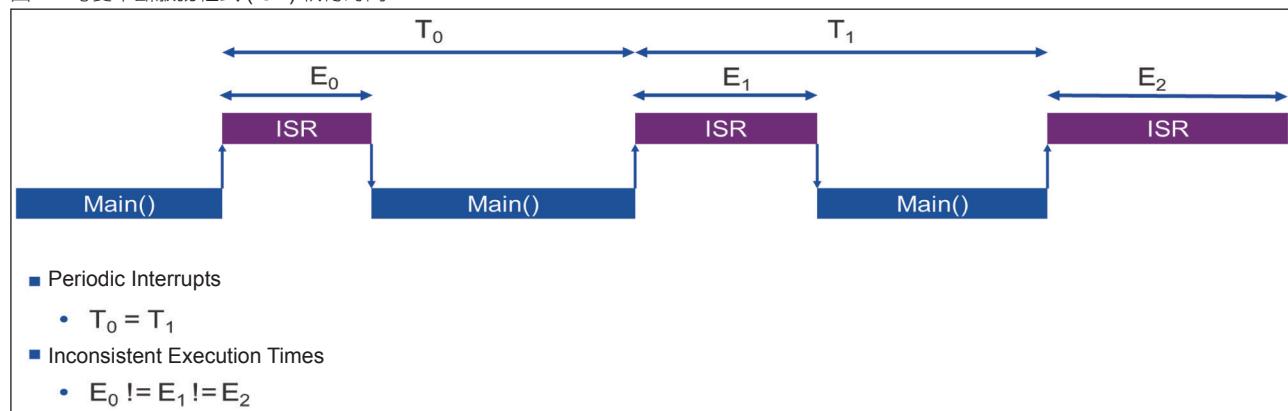

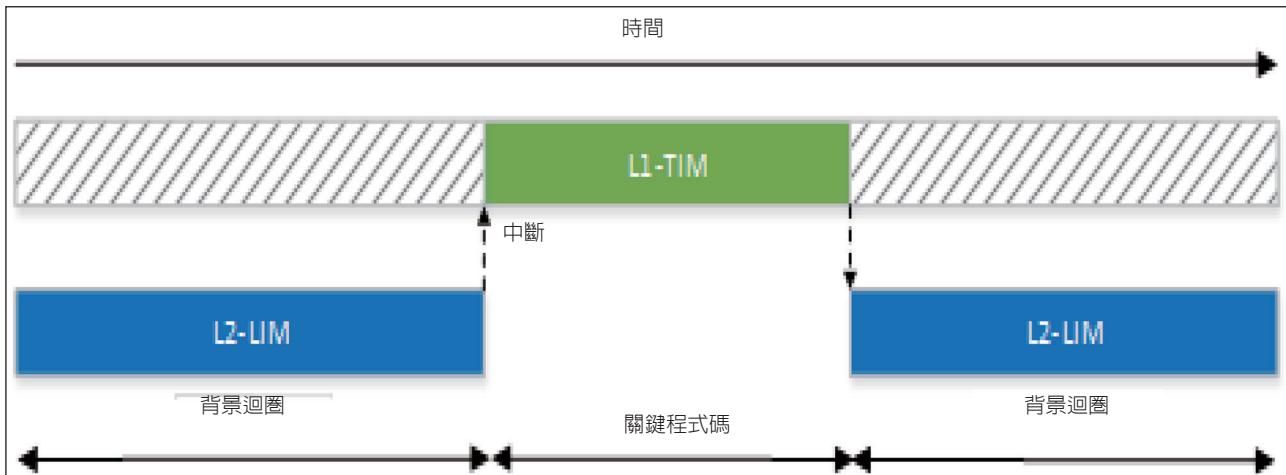

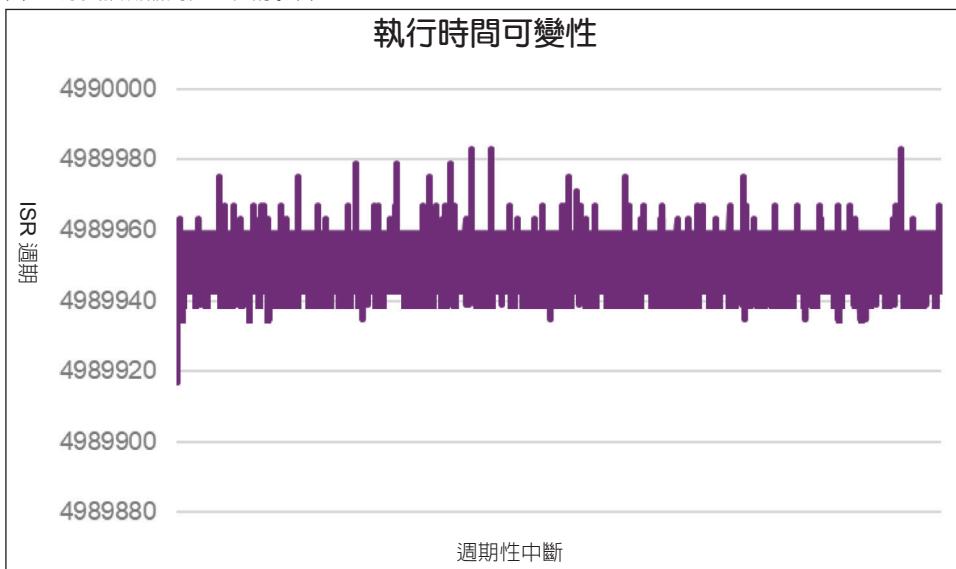

圖 1 細出了確定性系統。週期性中斷觸發，中斷服務程式處理時間關鍵型程式碼。該程式碼的執行時間必須是確定的，以免最終得到如圖 2 所示的系統，其中硬體的更新是隨機發生的。

此外，還需要將 Linux 的豐富功能和所有相關的中介軟體引入硬體控制的系統。Linux 需要記憶體管理單元 (MMU) 來為應用程式開發人員虛擬化實體記憶體。嵌入式 MMU 的處理器還包括至少一個 L1

圖 1：確定性執行示例

圖 2：可變中斷服務程式 (ISR) 執行時間

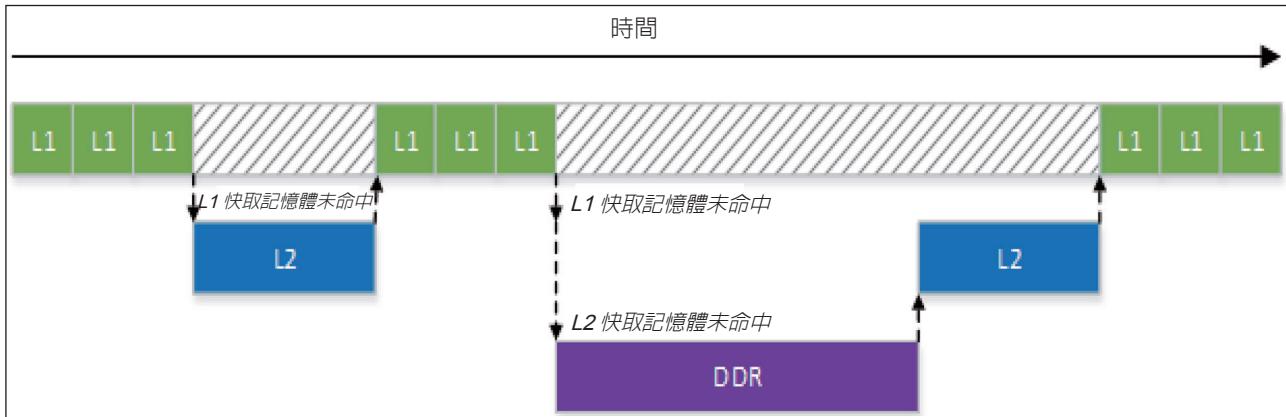

圖 3：L1 和 L2 快取記憶體未命中影響確定性

快取記憶體，且在大多數情況下還會有 L2 快取記憶體。快取記憶體和確定性彼此相關，如圖 3 所示。在此，我們可以看到 L1 或 L2 預提取如未命中將透過在填充快取記憶體時暫停執行流水線來引入執行的抖動。當然增大快取記憶體可以降低快取記憶體未命中的頻率，但還是不能完全消除執行的抖動。

在可運行 Linux 的處理器中，執行的抖動的另一個來源是分支預測器 (Branch Predictor)。處理器核心包括用於提高應用層效的分支預測器。無論採用何種實現方式，分支都是可以預測的，但有時會發生未命中現象。發生未命中時，將刷新流水線。未命中會導致不確定的執行行為。在中斷服務程式 (ISR) 期間，預測器中使用的分支歷史記錄表的分支歷史記錄與主應用程式碼的執行歷史記錄密切相關，而不是與 ISR 本身的執行歷史記錄密切相關。這將刷新 ISR 內的流水線，進而執行時間因 ISR 而異。使用允許使用者禁止分支預測器的處理器時，應用程式開發人員可以控制在系統中的何處以何種方式應用確定性。對於應用程式範圍的確定性，可以完全禁止分支預測器。當然，可以使用分支預測器來提高效能，因此將其關閉會降低效能。

## RISC-V PolarFire SoC FPGA 架構介紹

一些處理器能夠運行 Linux 但不能以確定方式執行程式碼，而另一些處理器能夠以確定方式執

行程式碼但不能運行 Linux。如果您的嵌入式工具包中有一種同時支持兩者的架構，豈不是很完美？Microchip 最近宣佈推出的 SoC FPGA 架構就是這樣一款產品，它基於 RISC-V，專為 PolarFire SoC 而設計。

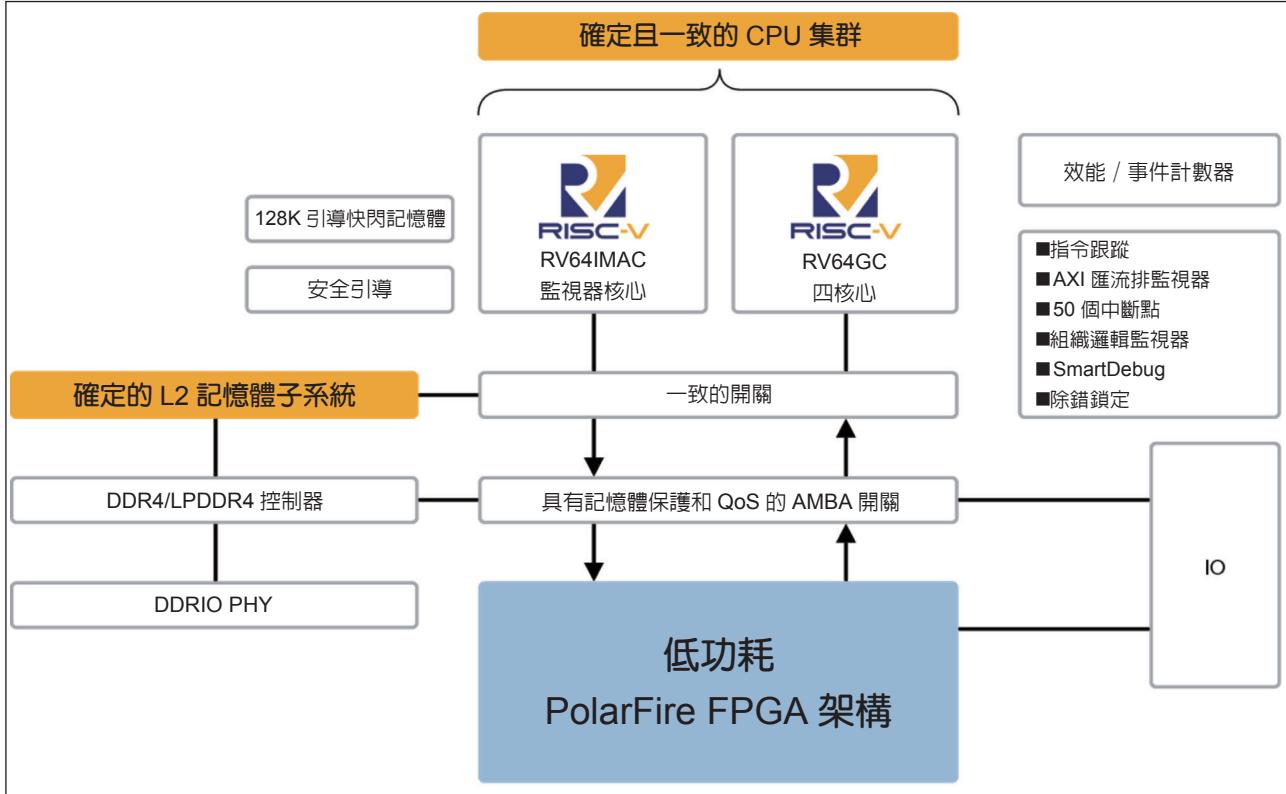

圖 4 包含四個能夠運行 Linux 的 64 位元 RV64GC RISC-V 核心，以及一個不能運行 Linux 的核心 (RV64IMAC)。換句話說，RV64IMAC 不包含 MMU，而四核 RV64GC 則包含 MMU。RV64IMAC 和 RV64GC 之間的指令集差異很簡單；RV64GC 包含一個雙精度浮點單元。為了提高架構中的確定性，用戶可以在上電後或在 ISR 期間關閉任何核心中的分支預測器。此外，全部五個核心均選擇了順序流水線，以提高確定性並避免對無序電腦發起的 Spectre 和 Meltdown 攻擊。

到目前為止，我們僅討論了與 CPU 核心相關的確定性。程式碼需要從記憶體執行，因此我們將討論 PolarFire SoC 中的記憶體子系統。首先，PolarFire SoC 中的整個儲存空間是一致的。一致性定義如下：具有多個資料副本的任何記憶體均由一致性管理器管理，僅包含一個資料副本的任何記憶體就其本質而言都是一致的，因為記憶體層級中不存在任何其他副本。PolarFire SoC 具有三個記憶體子系統：L1、L2 和 L3。L3 記憶體子系統整合了一個增強型 LPDDR3/LPDDR4 和 DDR3/DDR4 36 位元控制器。額外的 4 位元用於將 SECDED 添加到外部 L3 記憶體子系統。

圖 4：PolarFire SoC 架構

## L1 記憶體子系統

四個 RV64GC 應用核心各有一個 8 路組關聯 32 KB I\$TIM 和一個 8 路組關聯 32 KB D\$TIM。I\$ 等於指令快取記憶體，TIM 表示緊密整合的記憶體 (TIM)。使用者可以根據 I\$TIM 和 D\$TIM 必須始終有一個快取記憶體通道的要求配置 I\$TIM 和 D\$TIM。RV64IMAC 監視器核心具有一個 2 路組關聯 16 KB I\$TIM 和一個 8 KB DTIM。DTIM 是可從中執行程式碼的資料暫時記憶體。所有 L1 TIM 功能均提供低延時確定性訪問，並且支援單錯糾正雙錯檢測 (SECDED) 功能。

## L2 記憶體子系統

L2 記憶體子系統的大小為 2 MB，具有 SECDED 功能，可以配置為三種不同的模式。16 路組關聯快取記憶體、鬆散整合的記憶體 (LIM) 和暫時記憶體。LIM 記憶體可以固定到處理器上，並且可以用快取記憶體通道表示大小——換句話說，

LIM 可以用 128 KB 區塊 (通道) 構造，並且可以分配為對處理器進行獨佔訪問。配置為 LIM 的 L2 記憶體子系統可對其固定到的核心進行確定性訪問且保持一致，因為沒有其他副本與 L1 和 L3 記憶體子系統共用。LIM 是主應用程式和 ISR 中確定性程式碼執行的理想選擇。圖 5 紿出了 L2 記憶體子系統配置為 LIM 且 L1 配置為 TIM 時的確定性系統。

遺憾的是，由於分支預測器的未命中預測，即使 L2 被配置為 LIM，ISR 執行時間仍然存在可變性。圖 6 紿出了 L1 配置為 TIM 且 L2 配置為 LIM 時的應用程式執行。水準軸表示中斷，垂直軸表示 ISR 內的迴圈時間。如您所見，ISR 的執行隨時間變化。

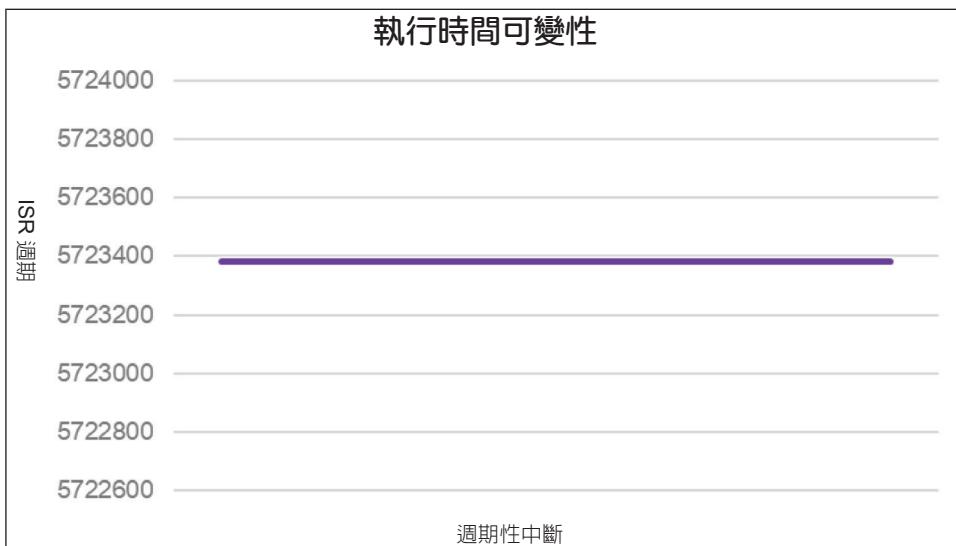

圖 7 紿出了關閉分支預測器後的確定性。

與 LIM 一樣，暫時記憶體可配置為 128 KB 區塊 (通道) 並分配給 CPU 核心。暫時記憶體非常適合用作從 LIM 執行程式碼的處理器與從 L1/L2 和 L3 記憶體子系統 (通常是 Linux) 執行程式碼的處理器之間的共用記憶體資源。如果 RV64IMAC 應用程式

圖 5:LIM 和 TIM 的確定性執行

圖 6: 分支預測器對確定性的影響

圖 7: 確定性行為

將資料寫入暫時記憶體，並且該儲存單元的副本位於 L1/L2/L3 記憶體子系統中的其他位置，則一致性管理器將保證一致性。這樣，即時應用程式便可與 Linux 上用戶空間中運行的應用程式一致地共用資料。

圖 8 是 PolarFire SoC 微處理器子系統的一種可能配置。在此配置中，RV64IMAC 提供即時功能，而 RV64GC 運行 Linux。如果您的即時功能需要浮點性能，則 RV64GC 可以達到此目的，因為可以關閉分支預測器，並且可以將 L1 記憶體子系統配置為 TIM。

## 總結

確定性是即時系統的關鍵要求。但是，市場上有許多處理器能夠運行

圖 8: 一致的消息傳送

Linux 但不能以確定方式執行程式碼，而另一些處理器能夠以確定方式執行程式碼但不能運行 Linux。PolarFire SoC 具有獨特、靈活的記憶體子系統，支援硬實時應用程式和 Linux 應用程式以靈活、一

致的方式共存。點擊此處開始使用 PolarFire SoC (<https://www.microsemi.com/product-directory/soc-fpgas/5498-polarfire-soc-fpga#getting-started>)。

## 台灣 IC 設計產學專家群聚 2020 RISC-V Taipei Day

由於 RISC-V 的彈性架構可滿足邊緣 AI 晶片設計需求，為協助台灣產業切入邊緣 AI 應用商機，台灣 RISC-V 聯盟 (RVTA) 日前舉辦 2020 RISC-V Taipei Day，邀請 RISC-V International 執行長 Ms. Calista Redmond、台灣 RISC-V 聯盟副會長暨晶心科技總經理林志明、芯原台灣副總經理徐國程、Mentor 嵌入式平台亞洲區經理徐志亮發表專題演講。

研發人才來源是 RISC-V 推廣上的重點工作之一，因此台灣 RISC-V 聯盟特別邀請包括中山大學黃英哲教授、清華大學李政崑教授、交通大學陳添福教授、成功大學陳中和教授等多位學界專家，與 Rambus 資深技術支援工程師伍志彬、IAR System 台灣區應用工程師蔡本中等產業專家進行對談，進而找出產學如何合作，才能進行人力培育，增加 IC 設計與產業所需人才。

台灣 RISC-V 聯盟會長王其國在開場致詞表示，RISC-V 是顛覆式創新開放架構，廠商可透過增加領域專用架構指令集來增加功能，這對於開發邊緣運算晶片或 AI 晶片的業者來說，不僅可以客製化設計，並且能共享開發成果，非常適合作為開源硬體的參考架構。台灣作為全球半導體的重鎮之一，不能在 RISC-V 開放架構上缺席。

針對如何培養 RISC-V 晶片架構開發人員與系統開發技術，學界均表示開發套件會是相當重要工具，因為現階段學校是使用 FPGA 模擬 RISC-V 晶片的運作進行教學與開發，不易開發成應用系統產品，若業界能夠提供使用真實量產晶片的開發套件，不僅能夠進行 IC 設計驗證，對於開發 RISC-V 架構的系統產品來說，更實用且更有效率，也能擴大 RISC-V 應用與推廣普及。