# 交錯式 ADC 的基本原理

■作者：Jonathan Harris/ADI 公司應用工程師

## 簡介

在今日的許多細分市場上，交錯式類比數位轉換器 (ADC) 在許多應用中都具有多項優勢。在通訊基礎設施中存在著一種推動因素，使 ADC 的採樣速率不斷提高，以便在諸如 DPD( 數位預失真 ) 等線性化技術中支援多頻段、多載波無線電，同時滿足更寬的頻寬要求。在軍事和航空航天領域，採樣速率更高的 ADC 可讓多功能系統用於通訊、電子監控和雷達等多種應用中——此處僅舉數例。工業儀器儀錶應用中始終需要採樣速率更高的 ADC，以便充分精準地測量速度更高的訊號。

首先，一定要準確地瞭解交錯式 ADC 是什麼。要瞭解交錯，最好先瞭解一下實際發生的情況以及如何建置。有了基本的瞭解後再討論交錯的優點。當然，我們都知道，天下沒有免費的午餐，因此也需要評估交錯挑戰。

## 關於交錯

若 ADC 為交錯式，則兩個或兩個以上具有定義時脈關係的 ADC 用來同步採樣輸入訊號，並產生組合輸出訊號，使得採樣頻寬為單個 ADC 頻寬的數倍。利用  $m$  個 ADC 可讓有效採樣速率增加  $m$  倍。為簡便起見並易於理解，我們重點考察兩個 ADC 的情況。這種情況下，如果兩個 ADC 的每一個採樣速率均為  $f_S$  且呈交錯式，則最終採樣速率為  $2 \times f_S$ 。這兩個 ADC 必須具有時脈相位關係，才能正確交錯。時脈相位關係由等式 1 紿出，其中： $n$  是某個特定的 ADC， $m$  是 ADC 總數。

$$\phi_n = 2\pi \left( \frac{n-1}{m} \right) \quad (1)$$

舉例而言，兩個 ADC 採樣速率均為 100

MSPS 且呈交錯式，因此採樣速率為 200 MSPS。此時，等式 1 可用來推導出兩個 ADC 的時脈相位關係，如等式 2 和等式 3。

$$\phi_1 = 2\pi \left( \frac{1-1}{2} \right) = 0 \text{ radians} = 0^\circ \quad (2)$$

$$\phi_2 = 2\pi \left( \frac{2-1}{2} \right) = \pi \text{ radians} = 180^\circ \quad (3)$$

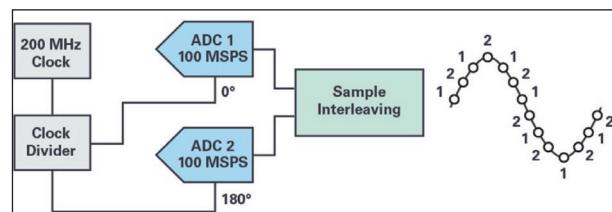

注意，如果已知時脈相位關係，便可檢查樣本結構。圖 1 以圖形說明時脈相位關係，以及兩個 100 MSPS 交錯式 ADC 的樣本結構。注意  $180^\circ$  時脈相位關係，以及樣本是如何交錯的。輸入波形也可由兩個 ADC 進行採樣。在這種情況下，採用經過 2 分頻的 200 MHz 時脈輸入，並所需的時脈相位發送至每個 ADC，便可實現交錯。

圖 1：兩個交錯式 100 MSPS ADC—基本原理圖。

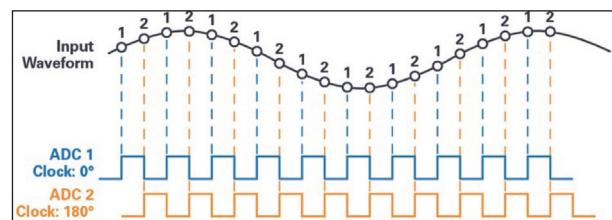

此概念還可以另一種方式表達，如圖 2 所示。透過將這兩個 100 MSPS ADC 以交錯方式組合，採樣速率便能增加至 200 MSPS。這樣每個奈奎斯特區可以從 50 MHz 擴展到 100 MHz，使工作時的可

圖 2：兩個交錯式 100 MSPS ADC—時脈和樣本。

用頻寬翻倍。增加的操作頻寬可為多個市場領域的應用帶來諸多優勢。無線電系統可以增加其支援的頻段數；雷達系統可以增加空間解析度；而測量設備可以實現更高的類比輸入頻寬。

## 交錯的優勢

交錯結構的優勢可惠及多個細分市場。交錯結構最有用的優勢是透過交錯式 ADC 的更寬奈奎斯特區增加頻寬。同樣的，我們在此舉出兩個 100 MSPS ADC 交錯以實現 200 MSPS 採樣速率的例子。圖 3 顯示透過交錯兩個 ADC，可以大幅增加頻寬。它可以為各種不同應用提供優勢。就像蜂巢標準增加了通道頻寬和操作頻段數一樣，對 ADC 可用頻寬的要求也越來越高。此外，在軍事應用中，需要更好的空間識別能力以及增加後端通訊的通道頻寬，這些都要求 ADC 提供更高的頻寬。由於這些領域對頻寬的要求越來越高，因此需要準確地測量這些訊號。因此，為了正確地獲取和測量這些高頻寬訊號，測量設備也需要更高的頻寬。很多設計中的系統要求其實領先於商用 ADC 技術。交錯結構可以彌補這一技術差距。

增加採樣速率能夠為這些應用提供更多的頻寬，而且頻率規劃更輕鬆，還能降低通常在 ADC 輸入端使用抗混疊濾波器時帶來的複雜性和成本。面

圖 3: 兩個交錯式 ADC——奈奎斯特區。

對這些優勢，大家一定想知道需要為此付出什麼代價。就像大多數事情一樣，天下沒有免費的午餐。交錯式 ADC 具有更高的頻寬和其他有用的優勢，但在處理交錯式 ADC 時也會帶來一些挑戰。

## 交錯挑戰

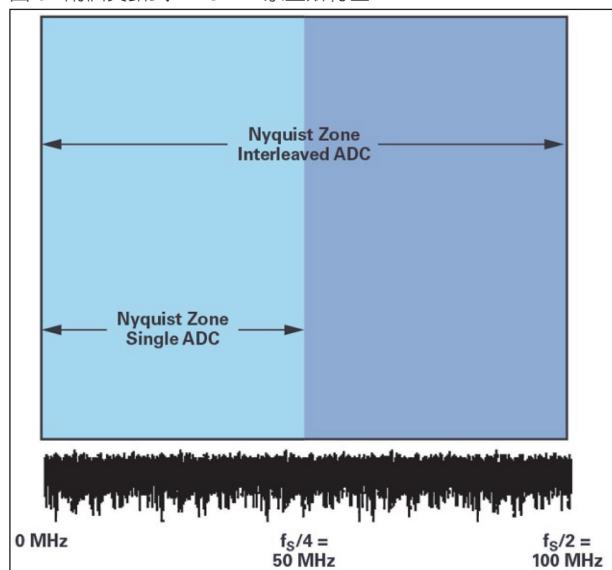

在交錯組合 ADC 時存在一些挑戰，還有一些注意事項。由於與交錯 ADC 相關的缺陷，輸出頻譜中會出現雜散。這些缺陷基本上是兩個正在交錯的 ADC 之間不匹配。輸出頻譜中的雜散導致的基本不匹配有四種。包括失調不匹配、增益不匹配、時序不匹配和頻寬不匹配。

其中最容易理解的可能是兩個 ADC 之間的失調不匹配。每個 ADC 都會有一個相關的直流失調值。當兩個 ADC 交錯並在兩個 ADC 之間來回交替採樣時，每個連續採樣的直流失調會發生變化。圖 4 舉例說明了每個 ADC 如何具有自己的直流失調，以及交錯輸出如何有效地在這兩個直流失調值之間來回切換。輸出以  $f_{S/2}$  的速率在這些失調值之間切換，將導致位於  $f_{S/2}$  的輸出頻譜中產生雜散。由於不匹配本身沒有頻率分量，並且僅為直流，因此出現在輸出頻譜中的雜散頻率僅取決於採樣頻率，並將始終出現在  $f_{S/2}$  頻率下。雜散的幅度取決於 ADC 之間失調不匹配的幅度。不匹配值越大，雜散值就越大。為了盡可能減少失調不匹配導致的雜散，不需要完全消除每個 ADC 中的直流失調。這樣做會濾除訊號中的所有直流成分，不適合使用零中頻 (ZIF) 架構的系統，該架構中的訊號內容真實複雜，而且包括直流資料。相反，更合適的技術是讓其中一個 ADC 的失調與另一個 ADC 匹配。選擇一個 ADC 的失調作為基準，另一個 ADC 的失調設定為盡可能接近的值。失調值的匹配度越高，在  $f_{S/2}$  產生的雜散就越低。

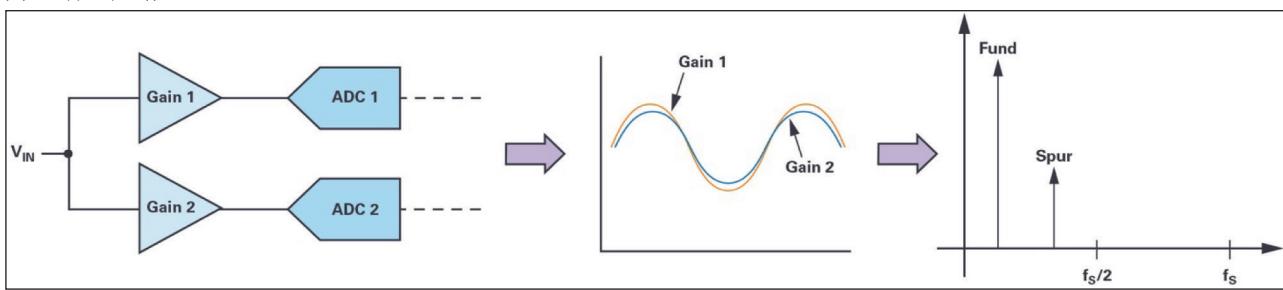

交錯時要注意的第二個不匹配是 ADC 之間的增益不匹配。圖 5 顯示了兩個交錯式轉換器之間的增益不匹配。在這種情況下，有一個不匹配頻率分量。為了觀察這種不匹配，必須向 ADC 施加訊號。

對於失調不匹配，無需訊號即可查看兩個 ADC 的固有直流失調。對於增益不匹配，如果不存在訊號，就無法測量增益不匹配，因而無法瞭解增益不匹配。增益不匹配將會產生與輸入頻率和採樣速率相關的輸出頻譜雜散，出現在  $f_s/2 \pm f_{IN}$  處。為了最大程度地降低增益不匹配引起的雜散，採用了與失調不匹配類似的策略。選擇其中一個 ADC 的增益作為基準，另一個 ADC 的增益設定為盡可能接近的值。每個 ADC 增益值的匹配度越高，輸出頻譜中產生的雜散就越小。

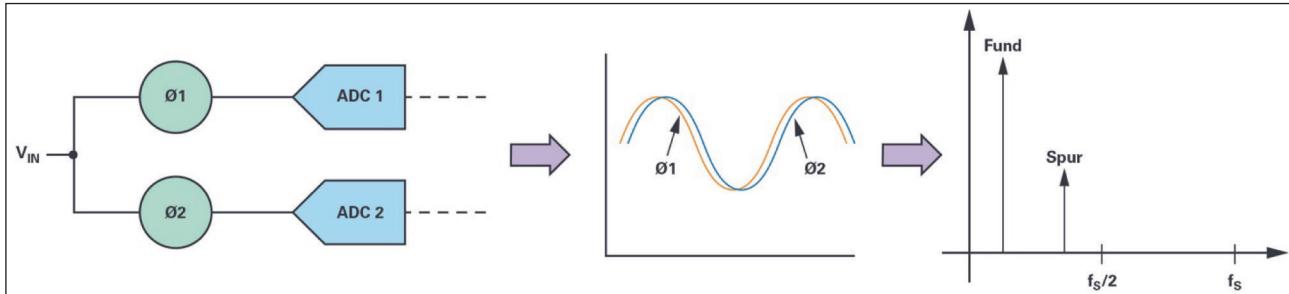

接下來，我們必須探討兩個 ADC 之間的時序不匹配。時序不匹配有兩個分量：ADC 類比部分的群延遲和時脈偏斜。ADC 中的類比電路具有相關的群延遲，兩個 ADC 的群延遲值可能不同。此外還有時脈偏斜，它也包括兩個分量：各 ADC 的孔徑不確定性和一個與輸入各轉換器的時脈相位精度相關的分量。圖 6 以圖形說明 ADC 時序不匹配的機制和影響。與增益不匹配雜散相似，時序不匹配雜散也與輸入頻率和採樣速率呈函數關係，出現在  $f_s/2 \pm f_{IN}$  處。

為了盡可能降低時序不匹配引起的雜散，需要利用合適的電路設計技術使各轉換器類比部分的群延遲恰當匹配。此外，時脈路徑設計必須儘量一

致以使孔徑不確定性差異最小。最後，必須精準控制時脈相位關係，使得兩個輸入時脈盡可能相差  $180^\circ$ 。與其他不匹配一樣，目標是儘量消除引起時序不匹配的機制。

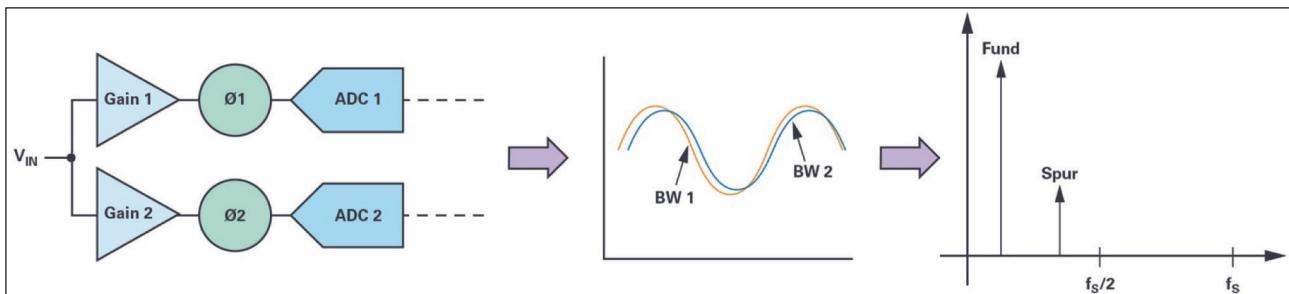

最後一個不匹配可能最難理解和處理：亦即，頻寬不匹配。如圖 7 所示，頻寬不匹配具有增益和相位 / 頻率分量。這使得解決頻寬不匹配問題變得更為困難，因為它含有另外兩個不匹配參數的分量。然而，在頻寬不匹配中，我們可在不同的頻率下看到不同增益值。此外，頻寬具有時序分量，使不同頻率下的訊號透過每個轉換器時具有不同的延遲。最大程度降低頻寬不匹配的最好辦法，是透過傑出的電路設計和佈局佈線，盡可能減少 ADC 之間的頻寬不匹配。ADC 之間的匹配越好，則產生的雜散就越少。正如增益和時序不匹配會導致在輸出頻譜的  $f_s/2 \pm f_{IN}$  處產生雜散一樣，頻寬不匹配也會在相同頻率處產生雜散。

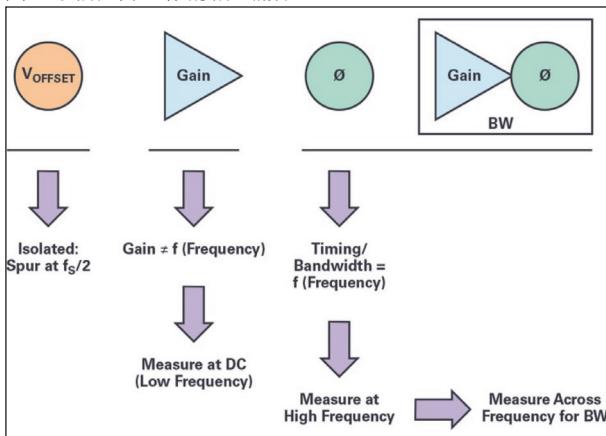

現在我們已經討論了交錯 ADC 時引起問題的四種不同的不匹配，我們可以發現其中有一個共通性。四個不匹配中有三個會在輸出頻譜的  $f_s/2 \pm f_{IN}$  處產生雜散。失調不匹配雜散很容易識別，因為只有它位於  $f_s/2$  處，並可輕鬆地進行補償。增益、時序和頻寬不匹配都會在輸出頻譜的  $f_s/2 \pm f_{IN}$  處

圖 4: 失調不匹配。

圖 5: 增益不匹配。

圖 6: 時序不匹配

圖 7: 頻寬不匹配。

圖 8: 交錯式不匹配的相互關係。

產生雜散；因此，隨之而來的問題是：如何確定它們各自的影響。圖 8 以簡單的圖形方式指導如何從交錯式 ADC 的不同不匹配中識別雜散來源。

如果只是考察增益不匹配，那麼它就是一個低頻（或直流）類型的不匹配。透過在直流附近執行低頻增益測量，然後在較高的頻率處執行增益測量，可將頻寬不匹配的增益分量與增益不匹配分離。增益不匹配與頻率無函數關係，而頻寬不匹配的增益分量與頻率呈函數關係。對於時序不匹配，可以採用類似的方法。在直流附近執行低頻測量，然後在較高的頻率下執行後續測量，以便將頻寬不匹配的

時序分量與時序不匹配分離。

## 結論

最新通訊系統設計、尖端雷達技術和超高頻寬測量設備似乎始終領先於現有的 ADC 技術。在這些要求的推動下，ADC 的用戶和製造商都想方設法，試圖跟上這些需求的步伐。與提高典型 ADC 轉換速率的傳統方式相比，交錯 ADC 可以更快的速度實現更寬的頻寬。將兩個或更多 ADC 交錯起來，可以增加可用頻寬，並以更快的速度滿足系統設計不斷成長的要求。然而，交錯 ADC 並非沒有代價，ADC 之間的不匹配不容忽視。雖然不匹配確實存在，但瞭解其本質及如何正確處理它們，設計人員就能更加明智地妥善運用這些交錯式 ADC，並滿足最新系統設計不斷成長的要求。

## 參考文獻

Had、Jim、Mark Looney 和 Rob Reeder。“推動多通道類比數位轉換器技術發展。”《類比對話》，第 39 卷第 5 期，2005 年 5 月。 [CTA](#)