# 高速放大器測試需要足夠多的數學知識來正確使用巴倫

■作者：David Brandon/ADI 高速放大器部門產品工程師

Rob Reeder/ 高速轉換器和射頻應用資深系統應用工程師

## 摘要

在大多數實驗室環境中，訊號產生器、頻譜分析儀等設備是單端儀器，用於測量高速差分放大器驅動器和轉換器的失真。因此，測量放大器驅動器的偶數階失真（例如二次諧波失真 HD2，甚至階偶數階交調失真或 IMD2）需要額外的元件，如巴倫（balun）和衰減器等來作為整體測試設置的一部分，以將單端測試儀器連接到放大器驅動器的差分輸入和輸出。本文透過不匹配訊號的數學知識揭示了相位不平衡的重要性，並說明了相位不平衡如何導致偶數階產物的增加（即變得更糟糕！）。本文還將展示了幾種不同高性能巴倫和衰減器的權衡如何影響被測放大器的性能指標（即 HD2 和 IMD2）。

## 數學背景 = Yay !

測試具有差分輸入的高速元件（如類比數位轉換器、放大器、混頻器、巴倫等）時，幅度和相位不平衡是需要理解的重要指標。

當類比訊號鏈設計使用 500 MHz 及以上的頻率時，必須非常小心，因為所有元件（無論主動還是被動）在頻率範圍內均具有某種固有不平衡。500 MHz 並不是一個奇妙的頻率點，只是基於經驗，這是大多數元件開始偏離相位平衡的地方。根據元件的不同，此頻率可能比這低得多、或高得多。

我們來仔細看看下面的簡單數學模型：

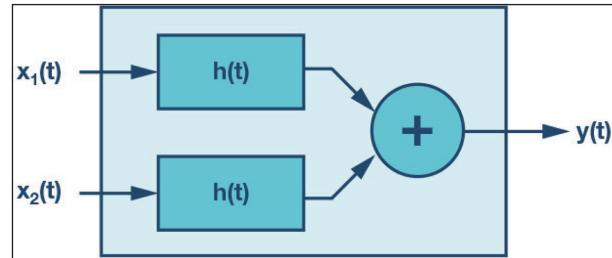

考慮 ADC、放大器、巴倫等或任何將訊號從單端轉換為差分（或反之）的元件的輸入  $x(t)$ 。訊號對

圖 1：具有兩個訊號輸入的數學模型。

$x_1(t)$  和  $x_2(t)$  是正弦訊號，因此差分輸入訊號具有如下形式：

$$\begin{aligned}x_1(t) &= k_1 \sin(\omega t) \\x_2(t) &= k_2 \sin(\omega t - 180^\circ + p) = -k_2 \sin(\omega t + p)\end{aligned}\quad (1)$$

如果不是這樣，就因為這些元件的不平衡，ADC 的偶數階失真測試結果在工作頻率範圍內可能會發生顯著變化。

ADC 或任何主動元件可以簡單地建模為對稱三階傳遞函數：

$$h(x(t)) = a_0 + a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) \quad (2)$$

那麼：

$$\begin{aligned}y(t) &= h(x_1(t)) - h(x_2(t)) \\y(t) &= a_1[x_1(t) - x_2(t)] + a_2[x_1^2(t) - x_2^2(t)] + \\&\quad a_3[x_1^3(t) - x_2^3(t)]\end{aligned}\quad (3)$$

理想情況下沒有不平衡，上述簡單系統的傳遞函數可以建模如下：

$x_1(t)$  和  $x_2(t)$  完全平衡時，這些訊號具有相同幅度 ( $k_1 = k_2 = k$ )，並且恰好  $180^\circ$  相差 ( $\phi = 0^\circ$ )。

$$\begin{aligned}x_1(t) &= (k) \sin(\omega t) \\x_2(t) &= (-k) \sin(\omega t)\end{aligned}\quad (4)$$

$$y(t) = (2a_1 k) \sin(\omega t) + (2a_3 k^3) \sin^3(\omega t) \quad (5)$$

對著運用三角恒等式並收集頻率等資訊，我們得到：

$$y(t) = 2\left(a_1 k + \frac{3a_3 k^3}{4}\right) \sin(wt) - \left(\frac{a_3 k^3}{2}\right) \sin(3wt) \quad (6)$$

這是差分電路的常見結果：理想訊號的偶次諧波抵消，而奇次諧波沒有抵消。

現在假設兩個輸入訊號的幅度不平衡，但沒有相位不平衡。這種情況下， $k_1 \neq k_2$ ,  $\phi = 0$ 。

$$\begin{aligned} x_1(t) &= (k_1) \sin(wt) \\ x_2(t) &= (-k_2) \sin(wt) \end{aligned} \quad (7)$$

把公式 7 代入公式 3，並再次運用著的三角恒等式。

$$\begin{aligned} y(t) &= \frac{a_2}{2} \times (k_1^2 - k_2^2) + (a_1(k_1 + k_2) + \left(\frac{3a_3}{4}\right) \times \\ &(k_1^3 + k_2^3)) \sin(wt) - \left(\frac{a_2}{2}\right) \times (k_1^2 - k_2^2) \cos(2wt) - \\ &\left(\frac{a_3}{4}\right) \times (k_1^3 + k_2^3) \sin(3wt) \end{aligned} \quad (8)$$

我們看到公式 8 中，二次諧波與幅度  $k_1$  和  $k_2$  的平方之差成正比，簡單來說即：

$$\text{second harmonic } \propto k_1^2 - k_2^2 \quad (9)$$

現在，假設兩個輸入訊號之間相位不平衡，沒有幅度不平衡。那麼， $k_1 = k_2$ ,  $\phi \neq 0$ 。

$$\begin{aligned} x_1(t) &= (k_1) \sin(wt) \\ x_2(t) &= (-k_1) \sin(wt + \phi) \end{aligned} \quad (10)$$

把公式 10 代入公式 3 並簡化——試試看，您也可以辦得到的！

$$\begin{aligned} y(t) &= \left(a_1 k_1 + \frac{3a_3 k_1^3}{4}\right) \times \\ &(\sin wt + \sin wt \times \cos \phi + \cos wt \times \sin \phi) - \\ &\left(\frac{a_2 k_1^2}{2}\right) \times (\cos 2wt - \cos 2wt \times \cos 2\phi + \sin 2wt \times \sin 2\phi) - \\ &\left(\frac{a_3 k_1^3}{4}\right) \times (\sin 3wt + \sin 3wt \times \cos 3\phi + \cos 3wt \times \sin 3\phi) \end{aligned} \quad (11)$$

從公式 11 可知，二次諧波幅值與幅度  $k$  的平方成正比。

$$\text{second harmonic } \propto k^2 \quad (12)$$

如果回過頭比較公式 9 和公式 12，並且假設

三角恒等式運用正確，那麼可以得出如下結論：二次諧波受相位不平衡影響比受幅度不平衡影響更嚴重。原因如下：對於相位不平衡，二次諧波與  $k_1$  的平方成正比；再看公式 12，對於幅度不平衡，二次諧波與  $k_1$  和  $k_2$  的平方差成正比，或看公式 9。由於  $k_1$  和  $k_2$  大致相等，因此這種差異通常很小，特別是如果將其與平方數進行比較！

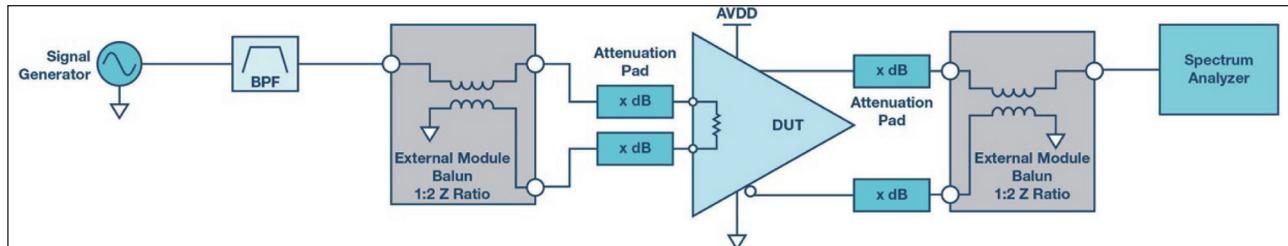

## 測試高速放大器

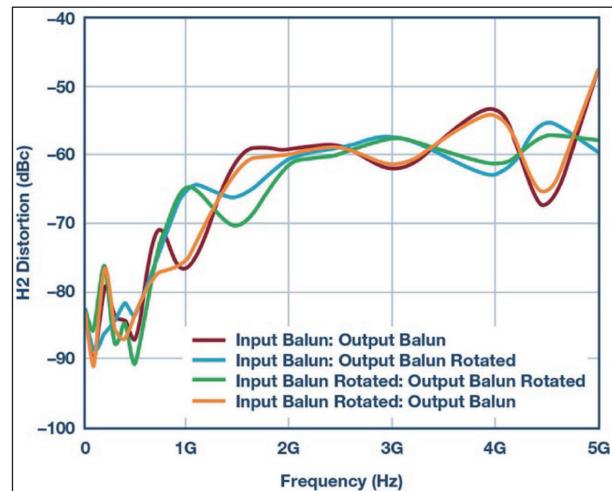

既然我們清除了障礙，接下來看一個使用案例，如圖 2 所示。這是一幅框圖，顯示了差分放大器實驗中常用的 HD2 矢真測試設置。

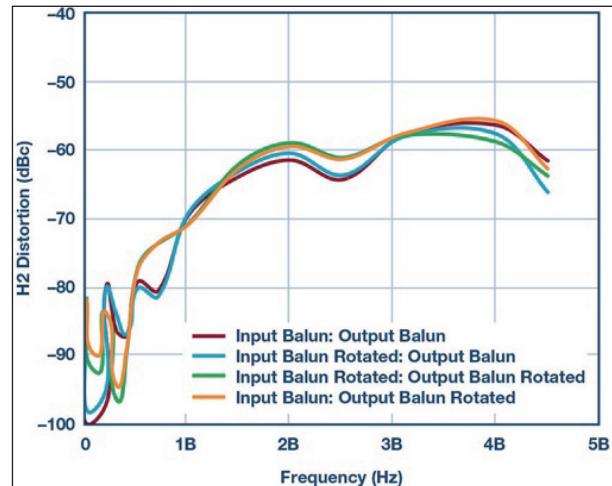

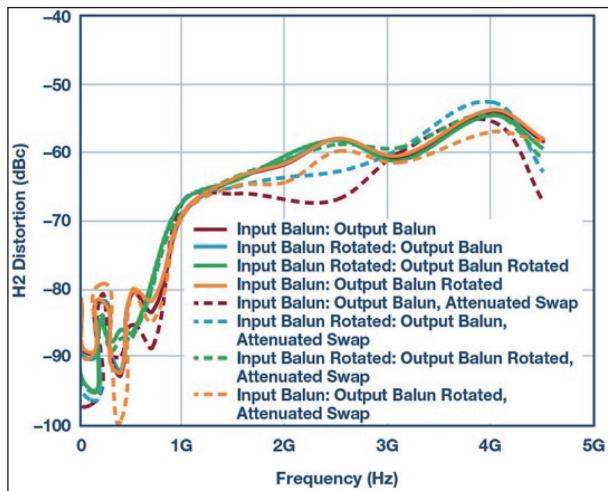

乍看相當簡單，但魔鬼隱藏在細節中。圖 3 顯示了一組 HD2 測試結果，其系使用本框圖中的所有元件、差分放大器、巴倫、衰減器等得到的。這些測試證明：僅僅用不同方式翻轉巴倫方向所導致的細微相位不匹配，便能在 HD2 掃頻中產生不同結果。此設置中有兩個巴倫，因此透過顛倒設置一側或兩側的連接可以創建四種可能的場景。結果如圖

圖 3：使用供應商 1A 巴倫和不同巴倫方向測試 HD2 性能。

圖 2：高速放大器 HD2 測試設置

3 所示。

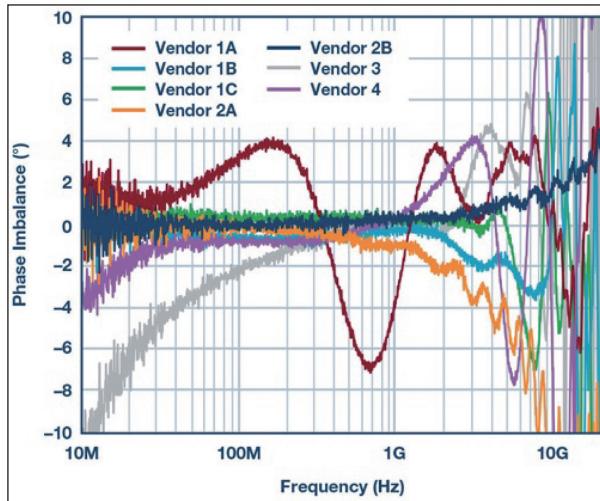

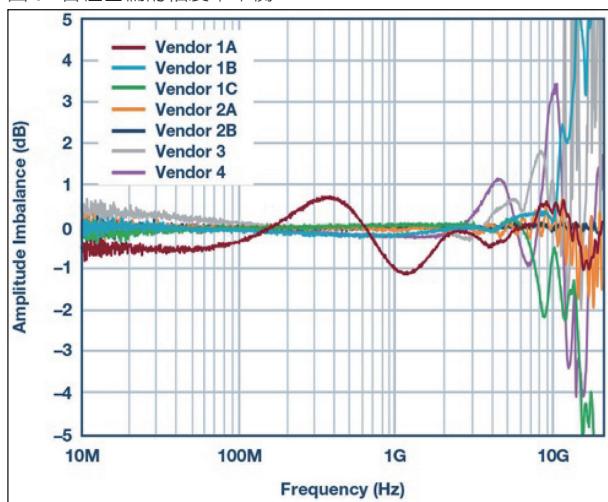

圖 3 揭示的 HD2 失真曲線方差量證明，需要進一步考察巴倫的性能，特別是相位和幅度不平衡。以下兩幅圖顯示了不同製造商的幾款巴倫的相位和幅度不平衡。使用網路分析儀來測量不平衡。

圖 4 和圖 5 中的紅色曲線對應於圖 3 中用於採集 HD2 失真資料的實際巴倫。供應商 1A 的這款巴倫具有最高頻寬和良好的通帶平坦度，但在同樣的 10 GHz 頻率測試帶上，相位不平衡比其他巴倫要差。

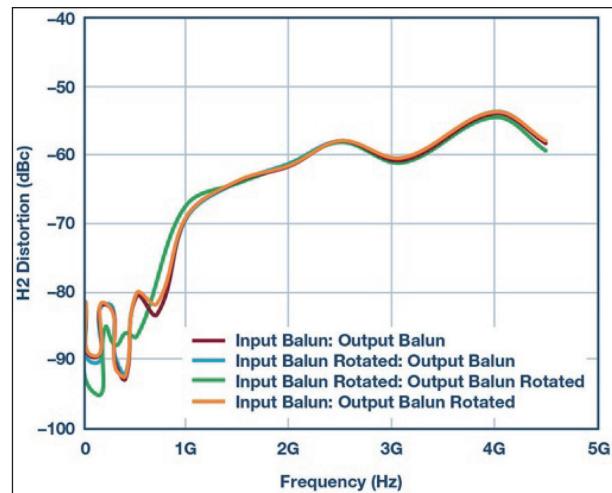

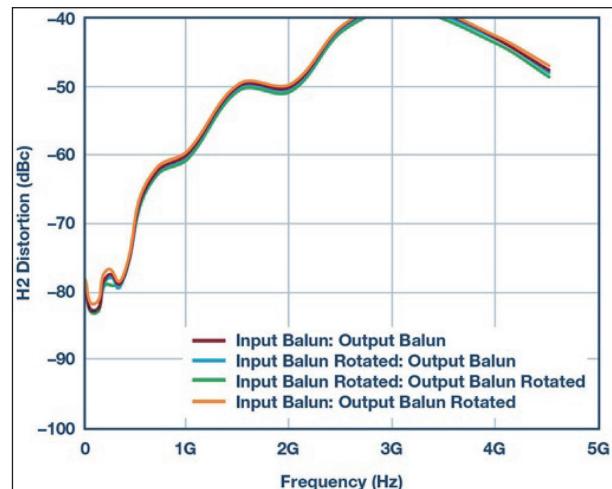

接下來的兩幅圖代表使用最佳巴倫對 HD2 失真重新測試的結果，這些巴倫分別來自供應商 1B 和供應商 2B，具有最低的相位不平衡，如圖 6 和圖 7 所示。注意，如果有更好的不平衡性能，則 HD2 失真方差會相應降低，如圖 7 所示。

圖 4: 各種巴倫的相位不平衡

圖 5: 各種巴倫的幅度不平衡

圖 6: 使用供應商 1B 巴倫和不同巴倫方向重新測試 HD2 性能。

圖 7: 使用供應商 2B 巴倫和不同巴倫方向重新測試 HD2 性能。

圖 8: 使用供應商 2B 巴倫和不同巴倫方向測試 HD3 性能。

為了進一步說明相位不平衡如何直接影響偶數階失真性能，圖 8 顯示了與前一 HD2 圖相同條件下

圖 9：僅使用供應商 2B 巴倫以及不同巴倫方向和衰減焊墊交換測試 HD2 性能。

的 HD3 失真。請注意，所有四條曲線大致相同，符合預期。因此，如前面的數學推導示例所證明的，HD3 失真對訊號鏈中的不平衡不太敏感。

到目前為止，應假定輸入和輸出連接的衰減器焊墊（如圖 2 所示）是固定一致的，且在巴倫方向測量期間無變化。圖 7 所示的相同曲線，僅測試供應商 2B 的巴倫性能，輸入和輸出之間交換衰減器。這就產生另一組（四條）曲線，如圖 9 中的虛線所示。結果是我們回到了開始的地方，因為這在測試測量中表現出更多的變化。這進一步強調了差分訊號對任一側的少量不匹配在高頻率下影響很大。請務必詳細記錄測試條件。

## 全部抵消

總之，在 GHz 區域開發全差分訊號鏈時，所有東西都很重要，包括衰減器焊墊、巴倫、電纜、印刷電路板上的佈線等。我們已經在數學上和實驗室中使用高速差分放大器作為測試平台證明了這一點。因此，在開始責備元件或供應商之前，請在 PCB 佈局和實驗室測試期間特別小心。

最後，您可能會問自己，多大相位不平衡是可以容忍的？例如，一個巴倫在 x GHz 時相位不平衡為 x 度，它對具體元件或系統有何影響？線性度性能是否會有一定程度的損失或多少 dB 悪化？

這是一個很難回答的問題。在理想世界裡，如果訊號鏈中的每件東西都完美匹配，那麼就不會有偶數階失真需要擔心。其次，如果有一個經驗法則或公式來告訴我們每 x° 的相位不平衡會帶來 x dB 的線性度損失（HD2 性能降低），豈不美哉。但是，這不可能。為什麼？因為每個元件，無論主動、被動還是差分式，都會有某種固有的相位不匹配。根本沒有辦法在內部使 IC 設計實現完美的平衡，或者切割出長度絕對一致的電纜。因此，不論這些不匹配有多小，隨著系統使用的頻率越來越高，它們都會變得更加突出。

總之，當使用全差分輸入和輸出時，我們會盡我們所能做好我們的工作，讓 IC 佈局不匹配保持最小。當您在實驗室測試我們的產品時，希望您也這樣做。 CTA

## ADI 以員工福利、企業文化和業務成長屢獲殊榮

Analog Devices, Inc. (ADI) 近期憑藉業界領先的員工福利及使員工感到極滿意和驕傲的企業文化獲得《富比世雜誌》(Forbes) 和《矽谷商業雜誌》(Silicon Valley Business Journal) 兩項殊榮。作為一家全球員工超過 1.5 萬名的半導體供應商，ADI 致力於解決世界上最艱鉅的技術挑戰，範圍涵蓋電力、自動駕駛、5G 無線通訊、工業 4.0 到數位醫療等。ADI 於 2018 會計年度實現了 62 億美元的年營收，近期並躋身 2019 年《財星 500 大》(Fortune 500) 企業，相較 2018 年《財星 1000 大》(Fortune 1,000) 排名上升了 45 名。

《富比世雜誌》將 ADI 列入 2019 年美國最佳雇主榜單，排名第 49。該榜單針對 5 萬名任職於員工數超過 1,000 位的公司員工進行匿名問卷調查。受訪者按照向他人以及在自身所在行業外推薦自己雇主的可能性進行評分。去年，ADI 在《富比世雜誌》全球最佳雇主排行榜上排名第 284 名。

在《矽谷商業雜誌》舉辦的灣區最佳工作場所評選中，ADI 名列前 15 大雇主之列。此年度排名凸顯了員工對公司領導力、協作文化、個人參與度以及個人福利和津貼十分滿意並表示高度肯定的優秀企業。

ADI 人資長 Marnie Seif 表示：「我們的目標是讓 ADI 成為想實現長期職業生涯發展、對現實世界產生持久影響的人才之首選雇主。能夠再次獲得最佳雇主殊榮使我們感到非常榮幸，特別值得一提的是，這項殊榮源自我們的員工在 ADI 的親身工作和生活體驗。」

# 類比數位轉換器的誤碼率： 減少閃光碼

■作者：Matt Guibord

德州儀器高速轉換器系統工程師

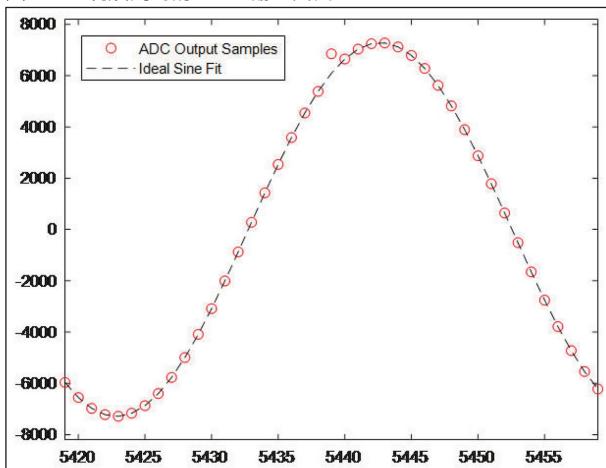

高速類比數位轉換器(ADC)因為採樣率增加，所以在ADC輸出資料方面會產生誤碼(code error)問題，又稱為閃光碼(sparkle code)。誤碼的定義，指ADC輸出碼出現超過定義閾值的錯誤。而構成錯誤的閾值，最常定義成在這個數值之下，錯誤會超過預期的ADC噪訊振幅，因此只要出現噪訊即可輕易判別錯誤。錯誤閾值的定義，另一種解釋就是錯誤振幅發生的機率，超過ADC假定之高斯(Gaussian)分散式噪訊振幅的預期機率。圖1即為ADC輸出採樣中發現的一個誤碼範例。相較於理想的正弦波擬合，很明顯可以看出錯誤採樣，而且遠超過圖中其他採樣的噪訊。

圖1：出現誤碼時的ADC輸出實例

ADC的誤碼率(code error rate; CER)，有時也稱為詞錯率(word error rate; WER)或亞穩態錯誤率(metastability error rate)，定義為每個採樣的平均錯誤數量，測量方式則是計算連續錯誤之間採

樣平均數量。它通常定義為一種數量序(order of magnitude)，例如 $10^{-12}$ 錯誤／採樣。因此，錯誤之間的平均時間就取決於轉換器的採樣率。只有當ADC以測量CER時的採樣率運轉，測得的CER才是正確的。一般來說，降低採樣率就能提升CER的數量序。

接下來要討論誤碼的來源，了解為什麼採樣是一個相當重要的因素。

## 為何會導致ADC閃光碼？

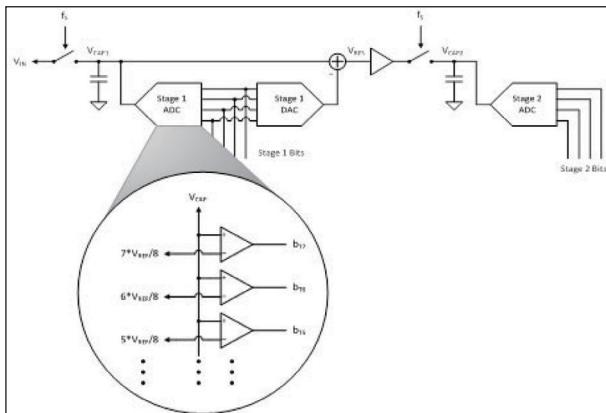

多步式的ADC架構，例如管線式快閃(pipelined flash)ADC或逐漸近似暫存器(SAR)ADC，會分階段將採樣的電壓轉換為數位位元，而每個連續階段都必須仰賴前一個階段的結果。如圖2所示的基本型管線式快閃高速ADC，這種簡化的ADC會顯現兩個轉換階段，每個連續階段都會產生一個數位碼，能更精密地估計輸入訊號。

圖中ADC的運作方式如下：

- 第一個階段會採樣輸入電壓，利用第一階段的ADC，概略地將類比輸入訊號轉換成數位碼。這個階段的快閃ADC，它的功用是利用高速比較器，將被採樣的電壓，跟ADC主要參考電壓( $V_{REF}$ )所產生的靜態電壓參考基準進行比較。快閃比較器的輸出則為溫度編碼的數位採樣，代表輸入電壓。

- 接著轉換出來的溫度編碼被直接送到第一階段DAC。這個DAC會根據概略轉換的採樣，輸出相應的類比電壓。

圖 2：管線化快閃 ADC 架構實例方塊圖

- 原始輸入電壓減去第一階段 DAC 的輸出，就會得出量化錯誤電壓或稱殘餘電壓 ( $V_{RES}$ )。接著殘餘電壓會被放大和重新採樣（管線化），為第二階段做準備。

- 第二階段 ADC 會量化  $V_{RES}$ ，以便更正確（解析度更高）地估計原始類比輸入電壓。

產生  $V_{RES}$  的過程中會引進一個高速的決策迴路。在一個採樣的時鐘周期之內，被採樣的電壓必須由第一階段 ADC 轉換成數位碼，數位碼必須從第一階段 DAC 輸出，再從原始的輸入電壓當中減去，由第二階段重新採樣。這個高速決策迴路會引進誤碼，是因為快閃 ADC 裡的比較器需要一段穩定時間，而這也是被採樣電壓和  $V_{REF}$  之間差異的一項功能。

更簡單地說，當輸入電壓 ( $V_{CAP1}$ ) 接近比較器的參考電壓（例如  $7*V_{REF}/8$ ），比較器會需要比較長的時間才能穩定。理論上，如果  $V_{CAP1}$  無窮接近比較器的參考電壓，因為比較器會在它的線性區域裡面運轉，比較器將永遠無法穩定。噪訊將阻止這個現象真的發生，但如果比較器真的耗時較長才能穩定，那麼第一階段 DAC 就可能使用不正確的數位碼來輸出量化的類比電壓。結果就是  $V_{RES}$  並不符合第一階段 ADC 實際的數位輸出碼。如此一來第二階段 ADC 就會轉換錯誤的  $V_{RES}$ ，造成誤碼。

## 什麼因素會影響 CER？

行文至此讀者應該已得知足夠細節，可總結出有哪些因素會影響 CER。很明顯 CER 取決於採樣

率。採樣率較快，就會縮短決策迴路做決策所需時間。決策時間縮短，會導致比較器無法及時穩定的機率巨幅增加。要注意的還有比較器的速度會直接影響 CER，而這正是 ADC 製程技術一大功能。第三個因素則是 ADC 的架構。

具有高速決策迴路的多步 (multistep) 架構，很容易因為 CER 不良而受影響。有些技巧可以用來降低這類架構的 CER，例如使用速度較快的製程技術、採取時序交錯法 (time interleaving) 或部署非同步時脈。另一方面，像摺疊內插式 (folding-interpolating) 架構這種並未使用高速決策迴路的架構，可使用多重比較器重新鎖存 (relatch) 階段，不必影響接下來任何一個階段就可大幅降低亞穩態機率。因此，單步 (single-step) 架構的 CER 原本就優於同等級管線式快閃或逐漸近似暫存器 ADC 架構。具備決策迴路的多步式架構，只要使用比較器重新鎖存，速度就一定會相應下降。

## 誤碼造成影響的實例

以下這個例子便可說明誤碼如何影響示波器的測量結果。假設有一個 RS-485 傳輸器正在間歇地輸出雜訊脈衝 (glitch)，工程團隊嘗試利用示波器測量這個雜訊脈衝，以便找出根本原因。假設這個雜訊脈衝很微弱，每隔幾天只會出現一次，而示波器是使用簡單的電壓門檻偵測法。另假設示波器是以 10 GSPS (每秒千兆次採樣) 的速度採樣，誤碼率為 10-12 錯誤／採樣。比較可能會從傳輸器抓到這個雜訊脈衝，還是從 ADC 找到誤碼？接下來讓我們看看。

$T_e$  為以秒為單位的錯誤間隔平均時間，可根據方程式 1，用 CER 和 ADC 採樣率 ( $f_s$ ) 計算出來：

$$T_e = \frac{1}{f_s * CER} \quad (1)$$

以上面這個 RS-485 雜訊脈衝為例，示波器錯誤間隔平均時間算出來是 100 秒。如果 RS-485 每隔幾天會出現雜訊脈衝，那麼就很難從測試的裝置中擷取期望雜訊脈衝，因為誤碼會同時觸發示波器。那麼什麼樣的 CER 是可以接受的？表 1 列出了不同

表 1 :  $T_e$  vs. CER 和取樣率

| CER (錯誤／取樣)<br>(errors/sample) | $f_s = 2.5$ GSPS | $f_s = 5$ GSPS | $f_s = 10$ GSPS |

|--------------------------------|------------------|----------------|-----------------|

| $10^{-9}$                      | 0.4 秒            | 0.2 秒          | 0.1 秒           |

| $10^{-12}$                     | 400 秒            | 200 秒          | 100 秒           |

| $10^{-15}$                     | 4.6 天            | 2.3 天          | 1.2 天           |

| $10^{-18}$                     | 12.68 年          | 6.34 年         | 3.17 年          |

誤碼率和採樣率的錯誤間隔平均時間。在 10 GSFS 的採樣頻率下，誤碼率一定要遠低於  $10^{-15}$  才能擷取到每隔幾天發生的雜訊脈衝。像 ADC12DJ5200RF 這類使用摺疊內插式 ADC 打造的示波器，因為 CER 為業界最低僅  $10^{-18}$ ，因此非常可能在沒有間歇誤碼造成錯誤觸發的狀況下，擷取到雜訊脈衝。

誤碼對於高速 ADC 應用有著不同程度的影響。示波器和以脈衝為基礎的飛行時間 (ToF) 系統，例如光達 (LIDAR) 或雷射距離測量，在使用簡單的閾值偵測時可能會對誤碼更為敏感，而通訊或雷達系統卻可能比較不敏感。舉例來說，通訊系統常利用前向偵錯 (FEC) 來克服單一誤碼對 ADC 採樣率所造成的效應。雷達則會使用一種以匹配濾波器 (相關) 為基礎的偵測運算法，利用長波形來提升偵測正確度，而這種方法原本就會減輕單一誤碼所帶來的影響。

## 頻域下的誤碼

誤碼的頻譜是以離散傅立葉變換 (DFT) 輸出的形式呈現，是將所有頻率窗口的雜訊基底都上升到相同數值。以下算式從正規化 DFT 的定義開始， $X_k$  代表輸出， $Y_k$  則為誤碼出現時的輸出頻譜。 $Y_k$  裡面這一項，

$$\frac{\alpha}{N} e^{-j\frac{2\pi}{N}kl}$$

就是用時域訊號的脈衝來呈現單一誤碼的頻率貢獻。真正 DFT 的雜訊基底功率上升了，

$$\frac{\alpha}{N} e^{-j\frac{2\pi}{N}kl}$$

和誤碼振幅的平方成正比，和 DFT 平方的長度成反比。因此訊信號長度較長或使

用分析視窗的系統，受誤碼的影響會比較少。

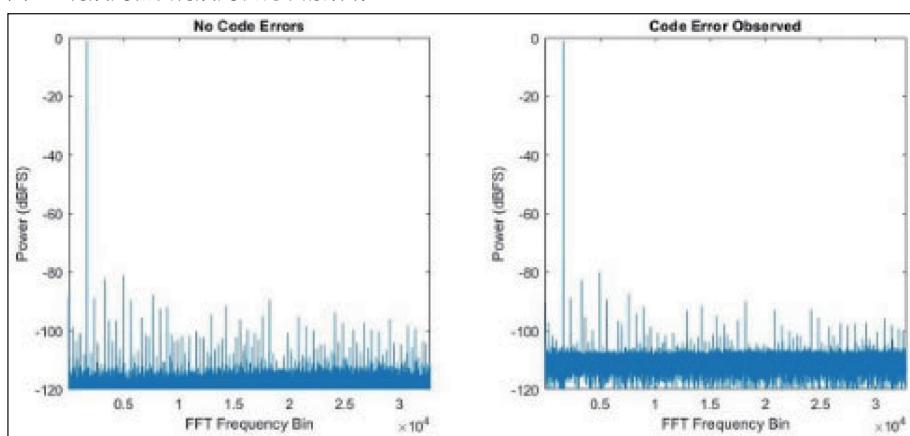

圖 3 顯示圖 1 裡因為誤碼而上升的雜訊基底，振幅為 758 碼。將這個結果比對一個 14 位元轉換器的全規模功率並予以正規化之後，

$$\left(\frac{2^{14}}{2\sqrt{2}}\right)^2.$$

就可算出長度 65536 的真實 DFT，每個窗口的噪訊功率為 -110.98 dBFS/bin。這個結果，正好符合圖 3 所測得因誤碼而受影響的上升雜訊基底。

## 結論

誤碼顯而易見是高速 ADC 時域輸出裡多餘的脈衝。在使用 DFT 測量出來的頻域裡，誤碼會造成雜訊基底上升。雖然有些應用可以容許這類誤碼，但像示波器或以脈衝為基礎的 ToF 等其他應用，必須要有誤碼率才能成功運作。

誤碼是多步式 ADC 架構中比較器出現亞穩態所造成的結果，因為在這樣的架構之下，前一個階段必須快速產生高速決策，下一個階段才有結果可用。採樣率、比較器速度和 ADC 架構會影響 ADC 設計的 CER。像摺疊內插式架構這種不需要高速決策迴路的 ADC 架構，其 CER 原本就比較優越，因為它能夠重新鎖存比較器輸出，降低亞穩態機率卻不必減速。

ADC12DJ5200RF 是一款超高速 ADC，能提供業界最低 CER，讓工程師對測試和測量應用的測量結果具有高度信心。 [CTA](#)

圖 3：有誤碼和沒有誤碼狀況下的頻域

# 用有源鉗位正激轉換器閉環 I

■作者 : Christophe Basso

法國 Toulouse 安森美半導體

有源鉗位正激(ACF)控制器在高頻DC-DC模組中很受歡迎：近零電壓開關、減小尺寸的磁性器件和高能效的設計是ACF的特點之一。如果設計功率級需要注意任何高功率設計，則從轉換器的控制-輸出傳遞函數可很好地瞭解補償策略，以滿足交越和相位裕度等設計目標。本文將先談談ACF傳遞函數，然後給出一個典型的補償示例。

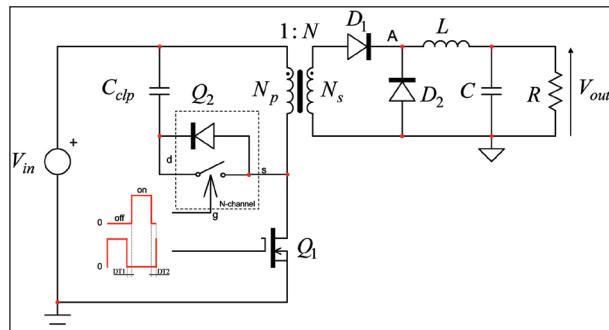

## 功率級運行

圖1顯示一個ACF的簡化電路圖，<sup>[1]</sup>中描述了其運行細節。基本上，電晶體 $Q_1$ 如在經典的正激轉換器中工作，但當它關斷時，退磁過程涉及鉗位電容 $C_{clp}$ 和初級電感 $L_{mag}$ 之間的諧振週期。存儲在磁化電感中的部分能量將漏極連接處的集總電容轉移， $v_{DS}(t)$ 上升，直到它流過 $Q_2$ 體二極體的路徑。然後，通過在零電壓開關(ZVS)條件下導通 $Q_2$ ，使後者短路： $Q_1$ 的漏極現在鉗位到 $V_{in}$ 加 $C_{clp}$ 的電壓 $V_{clp}$ 。由於到 $L_{mag}$ 和 $C_{clp}$ 之間的諧振週期，迴圈電流最終反轉，並流過 $Q_2$ (仍導通)和磁化電感 $L_{mag}$ 。

在某個點，控制器將指示 $Q_2$ 開通，迫使電流離開包括 $C_{clp}$ 在內的網格，自然地流過輸入源 $V_{in}$ 和漏極集總電容：漏極節點開始下降，直到一個新的

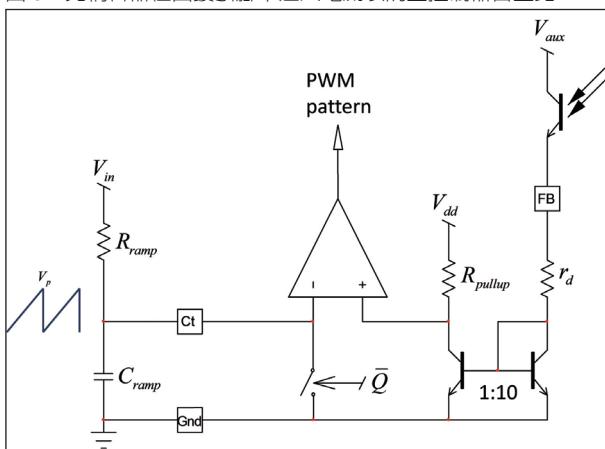

圖1：有源鉗位元正激轉換器可以高開關頻率運行

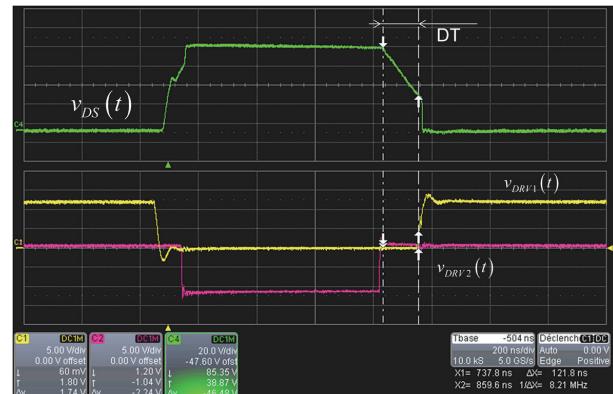

圖2：當死區時間調整得很好時，就可實現近ZVS的運行

開關週期發生，從而降低了導通損耗。

如圖2所示，在MOSFET轉換之間插入了一個死區時間，從而提供產生諧振漏源週期的時間，該週期現在涉及 $C_{lump}$ 的 $L_{mag}$ ，以達到一個穀點。在某些工作條件下(較小的輸出電流)，漏波觸地，導致零導通損耗。

## 傳遞函數

在補償轉換器或任何系統之前，您需要功率級的控制-輸出傳輸函數。換句話說，如果您激勵控制輸入-在這裡是脈寬調製器(PWM)-產生正弦波，那如何通過功率級傳輸資訊並在輸出中產生回應？將響應與激勵聯繫起來的數學關係是我們需要的傳遞函數 $H$ 。

在<sup>[1]</sup>中匯出了電壓模式下ACF的控制-輸出傳遞函數，並通過四階多項式描述了該轉換器：

$$H(s) = \frac{V_{out}(s)}{D(s)} = H_0 \frac{\frac{1 + \frac{s}{\omega_B}}{1 + \frac{s}{\omega_B Q_M}}^2 \cdot N \left( V_{in} - D_0 r_{on1} M_0 - \frac{s C_{clp}}{1 + \frac{s}{\omega_B Q_M} + \left(\frac{s}{\omega_B M}\right)^2} \right)}{(1 + \frac{s}{\omega_B Q_F})^2} \quad (1)$$

方程由兩個部分組成：左邊是經典正激轉換器項，其中

$$\begin{aligned}

H_0 &= \frac{R_{load}}{R_{load} + r_L} \\

\omega_{0F} &= \frac{1}{r_C C_{out}} \\

\omega_{0F} &= \frac{1}{\sqrt{L_{out} C_{out}}} \sqrt{\frac{r_L + R_{load}}{r_C + R_{load}}} \\

Q_F &= \frac{L_{out} C_{out} \omega_{0F} (r_C + R_{load})}{L_{out} + C_{out} [r_L r_C + R_{load} (r_L + r_C)]}

\end{aligned} \tag{2}$$

(1) 中的第二項表示有源鉗位元電路的增加以及圍繞  $C_{clp}$  和  $L_{mag}$  建立的諧振網路的影響：

$$\begin{aligned}

\omega_{0M} &= \frac{1 - D_0}{\sqrt{L_{mag} C_{clp}}} \\

Q_M &= \sqrt{\frac{L_{mag}}{C_{clp}}} \frac{1 - D_0}{r_{on2} (1 - D_0) + D_0 r_{on1}} \\

M_0 &= \frac{V_{clamp}}{(1 - D_0)^2}

\end{aligned} \tag{3}$$

在這些運算式中， $r_L$  和  $r_C$  分別表示輸出電感 ( $L_{out}$ ) 和電容 ( $C_{out}$ ) 等效串聯電阻 (ESR)， $r_{on1}$  表示主開關電晶體  $r_{DS(on)}$ ， $r_{on2}$  表示有源鉗位電晶體  $r_{DS(on)}$ ， $N$  表示變壓器匝比， $D_0$  表示靜態占空比。

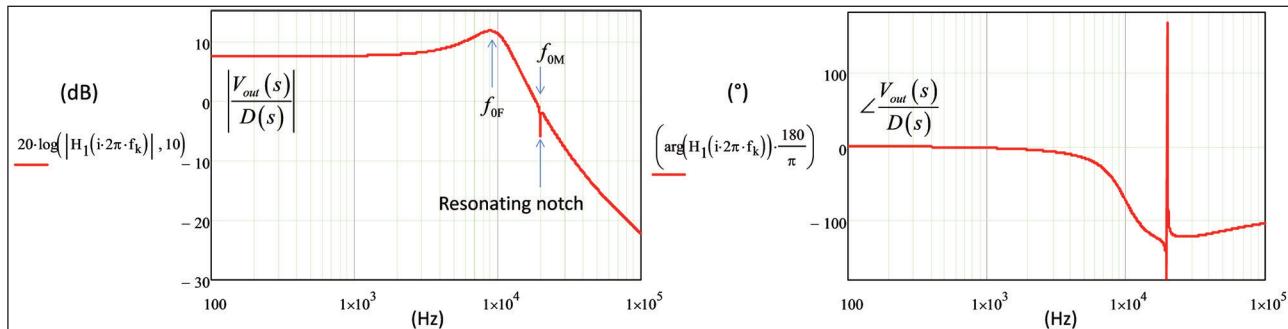

根據該運算式，我們可獲得 10-Hz 至 100-kHz 頻率範圍的幅值和相位響應的波特圖 (圖 3)。各器件的值為 3.3V/30 A DC-DC 塊的值，由安森美半導體的 NCP1566 供電<sup>[2]</sup>。有源鉗位元部分是特意非阻尼的，並假定  $Q_2$  是低  $r_{DS(on)}$  的 MOSFET。

圖 3：控制 – 輸出傳遞函數顯示一個諧振陷波，強調出現雙零點的相位

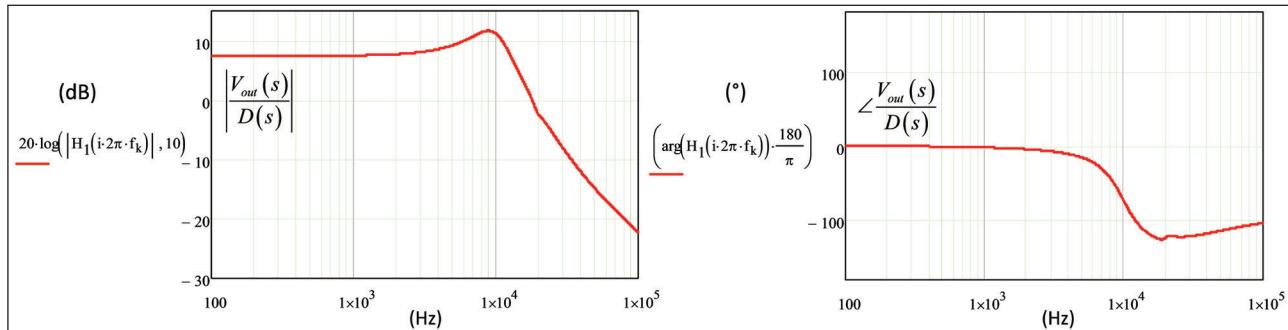

圖 4：當阻尼時，諧振的毛刺效應會減弱，您可將交越推到諧振之外。

當頻率達到 (3) 所描述的諧振時，您可觀察到與相位嚴重失真相關的幅值毛刺。幅值下降歸因於一次側諧振電流的突增，這導致了一次側功率 MOSFET Q1 的壓降。此壓降從輸入電壓  $V_{in}$  中減去 (1) 中右側項，並創建觀察到的回應陷波。根據<sup>[3]</sup> 和<sup>[4]</sup> 的建議，選擇一個在  $L_{mag}-C_{clp}$  的最小諧振頻率之前的交越點是明智的，因為此時存在嚴重的相位滯後。但是，如果在有源鉗位元電路中施加適當的阻尼，則可以擴展交越。如<sup>[5]</sup> 所示，在瞬態條件下，必須仔細研究這種決策對主 MOSFET 漏源峰值電壓的影響。圖 4 顯示同樣的傳遞函數，現在被  $Q_2$  的  $2.5-\Omega r_{DS(on)}$  所抑制：幅值和相位回應非常接近經典正激轉換器，且  $f_c$  可選擇在諧振陷波之外。

## 脈寬調製器

(1) 中給出的運算式不包括 PWM 塊的影響。在隔離 DC-DC 轉換器中，光耦合器會偏置控制器回饋引腳來控制占空比，因為調節回路位於二次側。在大功率轉換器中常見的一種方案是並聯調節器：光耦合器不是通過公共發射極配置將引腳拉低至接地，而是通過發射極連接控制器並注入電流。此電

流在內部鏡像，以拉低一個由  $50\text{k}\Omega$  電阻載入的內部節點。這種電壓偏置 PWM 比較器，並確保穩壓。當輸入動態電阻壓降較小時，由於準恒定  $V_{CE}$  電壓，該技術最小化米勒效應：光耦合器極被推到更高的頻率，而不太關注閉環（閉合環路）。動態電阻  $r_d = 400\Omega$ ，但對頻率分析不產生影響。如果將電容回饋引腳接地，就會產生影響。但這配置的阻抗是 ac，顯而易見，因為單獨的光耦合器調節注入電流。此電流被 10 除（注意  $d_{iv}$ ），並通過拉高阻抗，調節內部操作點。

在倒相引腳上，定時電容  $C_{ramp}$  由取決於輸入電壓的電流充電。因此，類比鋸齒波的斜率將與輸入電壓有關，隨著  $V_{in}$  變化而動態地改變增益。此配置實現我們所謂的前饋操作。可能顯示<sup>[6]</sup>，該調製單元的小信號增益等於：

$$G_{PWM} = \frac{1}{k_{FF} V_{in}} \quad (4)$$

及

$$k_{FF} = \frac{1}{F_{sw} R_{ramp} C_{ramp}} \quad (5)$$

圖 5：光耦合器在回饋引腳中注入電流以調整控制器占空比

在(1)中，您可看到在方程的右邊出現了  $V_{in}$ 。它令您瞭解傳輸函數的直流增益 ( $s=0$ ) 將隨輸入電壓的變化而變化。因此，交越頻率和可能的穩定性都會受到影響。通過包含(4)描述的 PWM 傳遞函數，分母中的  $V_{in}$  抵消了輸入電壓的影響，在輸入範圍內穩定了環路增益和交越頻率。

### Type 3 補償器

為設計 ACF 轉換器的環路增益，我們需要將 PWM 模式激勵因數  $D(s)$  與觀察到的變數  $V_{out}(s)$  回應聯繫起來的傳遞函數。我們將通過極點 - 零點位置應用選定的設計策略，以確保轉換器的強固性和良好的瞬態回應。

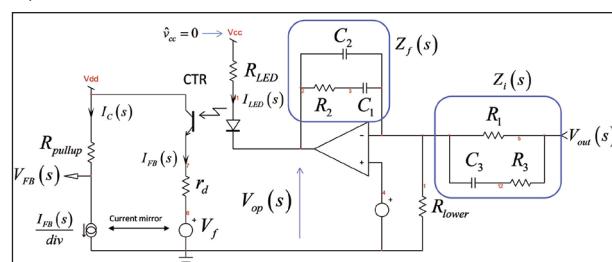

圖 6 表示含一個 3 型補償器的典型架構，採用光耦合器隔離。該光耦合器本身受電流傳輸比 (CTR) 和極點的影響，極點的位置取決於負載電阻。在本應用中，分流調節回饋輸入讀取光耦合器電流。負載電阻是  $r_d$  且相當小，這意味著我們必須描述一個相當高頻率的光耦合器極點，以便以後中和它<sup>[7]</sup>。請注意，LED 連接到二次側的一個安靜的  $V_{cc}$  點（或輔助電壓  $V_{aux}$ ），與  $V_{out}$  完全交流耦合。需要強調這一點，否則會產生快速的通道，使補償器<sup>[7]</sup>的頻率回應失真。LED 中的交流電流（忽略其動態電阻）由下式給出：

$$I_{LED}(s) = -\frac{V_{op}(s)}{R_{LED}} \quad (6)$$

其中  $V_{op}$  是運算放大器的交流輸出電壓。考慮一個完美的運算放大器，這電壓被定義為

$$V_{op}(s) = -\frac{Z_f(s)}{Z_i(s)} V_{out}(s) \quad (7)$$

$Z_f$  和  $Z_i$  是圖 6 中所圈部分的阻抗。從這兩個網路中，我們可用快速分析電路技術 (8) 來推斷我們想要的傳遞函數零點的位置。 $Z_f$  和  $Z_i$  怎樣的的阻抗組合將使輸出  $V_{FB}$  為零，儘管  $V_{out}$  有激勵？

圖 6：使用電壓模式有源鉗位元正向轉換器閉合環路需要 type-3 補償器。在本例中， $R_{pullup}$  為  $50\text{k}\Omega$ ， $R_{LED}$  隨意固定為  $1\text{k}\Omega$ ，而  $R_1$  為  $1662\Omega$ 。

有兩個條件：

1. 當  $V_{out}$  在  $s_z$  處調諧時， $Z$  幅值無窮大，則  $V_{FB}(s_z)=0$

$V_z$  由分子和分母  $D(s)$  組成。當  $D(s_z)=0$  時，這個阻抗無窮大。因此，這個一階網路的極點是我們感興趣的零點。影響  $Z_i$  的時間常數是通過暫時斷開  $C_3$  和“觀察”通過其連接端子提供的電阻來獲得的。在我們的思維中，時間常數是，網路極點或傳遞函數零點是簡單的。

2. 當  $R_2$  和  $C_1$  串聯構成變換短路時，輸出也為零。

這個阻抗被定義為  $Z_f(s)=R_2+1/sC_1$ 。您得到瞭解  $Z_f(s)=0$  的零點，從而定義了第二個零點位置在  $\omega_{z_2}=1/R_2C_1$ 。

考慮到這些結果並繼續努力，我們可根據<sup>[6]</sup>更新(7)

$$V_{op}(s) \approx -V_{out}(s) \frac{R_2}{R_1} \frac{\left(1 + \frac{1}{sR_2C_1}\right)\left(1 + sC_3R_1\right)}{(1 + sR_3C_3)(1 + sR_2C_2)} \quad (8)$$

這時考慮  $R_3 \ll R_1$  and  $C_2 \ll C_1$ 。

將(8)代入(6)中得出 LED 電流：

$$I_{LED}(s) = V_{out}(s) \frac{R_2}{R_{LED}R_1} \frac{\left(1 + \frac{1}{sR_2C_1}\right)\left(1 + sC_3R_1\right)}{(1 + sR_3C_3)(1 + sR_2C_2)} \quad (9)$$

輸出電壓  $V_{FB}$  是光耦發射極電流與電流鏡像分頻比  $a_{iv}$  的倍數

$$V_{FB}(s) = -\frac{I_{FB}(s)}{div} R_{pullup} \quad (10)$$

發射極電流是受 CTR 影響的 LED 電流：

$$I_{FB}(s) = I_{LED}(s) \text{CTR} \quad (11)$$

將所有這些運算式與(9)結合，我們得到所需的完整傳遞函數：

$$\frac{V_{FB}(s)}{V_{out}(s)} = -\frac{R_{pullup} \text{CTR}}{R_{LED} \cdot div} \frac{R_2}{R_1} \frac{\left(1 + \frac{1}{sR_2C_1}\right)\left(1 + sC_3R_1\right)}{(1 + sR_3C_3)(1 + sR_2C_2)} \quad (12)$$

它可用以下低熵格式表示，在分子中有反零點：

$$\frac{V_{FB}(s)}{V_{out}(s)} = -G_0 \frac{\left(1 + s_{z_1}/s\right)\left(1 + s/s_{z_1}\right)}{\left(1 + s/s_{p_1}\right)\left(1 + s/s_{p_2}\right)} \quad (13)$$

其中

$$G_0 = \frac{R_2}{R_1} \frac{R_{pullup} \text{CTR}}{R_{LED} \cdot div} \quad (14)$$

$$\omega_{z_1} = \frac{1}{R_2 C_1} \quad (15)$$

$$\omega_{z_2} = \frac{1}{R_1 C_3} \quad (16)$$

$$\omega_{p_1} = \frac{1}{R_3 C_3} \quad (17)$$

$$\omega_{p_2} = \frac{1}{R_2 C_2} \quad (18)$$

現在我們已有補償器傳遞函數，我們需要一種方法來調整交越點上的期望增益或衰減。需要選擇正確的  $R_2$  值，同時考慮由設計固定的或製造商強加的其他器件值（例如，電路中的  $R_{pullup}$ ）來獲得。(12)的幅值由下式確定：

$$|G(f_c)| = \frac{R_2}{R_1} \frac{R_{pullup} \text{CTR}}{R_{LED} \cdot div} \sqrt{\frac{1 + \left(\frac{f_{z_1}}{f_c}\right)^2}{1 + \left(\frac{f_{p_1}}{f_c}\right)^2}} \sqrt{\frac{1 + \left(\frac{f_c}{f_{z_2}}\right)^2}{1 + \left(\frac{f_c}{f_{p_2}}\right)^2}} \quad (19)$$

您可從中提取  $R_2$  的正確值，知道  $|G(f_c)|$  表示所選交越頻率  $f_c$  處的所需增益或衰減：

$$R_2 = |G(f_c)| \frac{R_1 R_{LED} \cdot div}{R_{pullup} \text{CTR}} \sqrt{\frac{1 + \left(\frac{f_c}{f_{p_1}}\right)^2}{1 + \left(\frac{f_{z_1}}{f_c}\right)^2}} \sqrt{\frac{1 + \left(\frac{f_c}{f_{p_2}}\right)^2}{1 + \left(\frac{f_c}{f_{z_2}}\right)^2}} \quad (20)$$

一旦  $R_2$  的值已知，您就可以使用(15)至(18)對其餘的補償元素進行計算。

## 補償策略

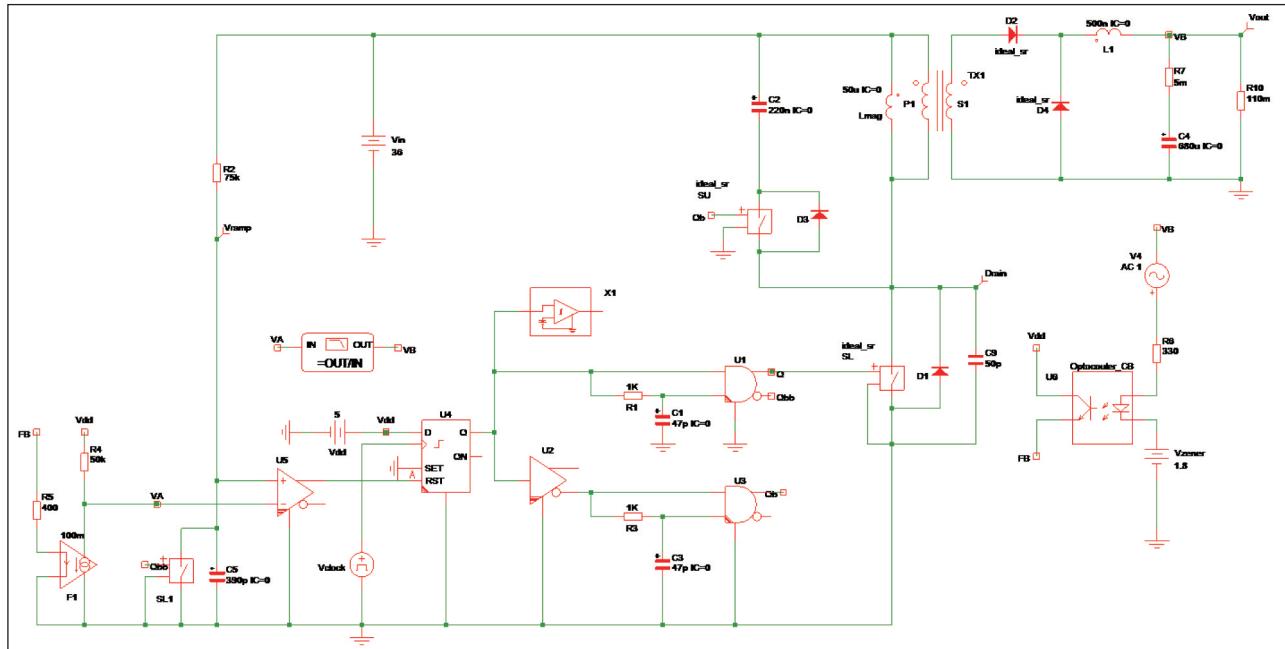

在手上有完整的 type 3 傳遞函數的情況下，我們可根據我們想要穩定的轉換器的功率級響應來想出一種補償策略。我們有幾種選擇來獲得這一響應。我們可以用 Mathcad 和我們給出的解析運算式(1)來計算它，也可在工作臺上計算它。對於後一個選擇，我們需要一個可以工作的硬體。另一個可行的選擇是圖 7 的 SIMPLIS 模擬電路。

下期待續……

圖 7：這簡單的閉環 ACF 范本使用展示版本本元素

## 參考資料：

- 1.C. Basso, The Small-Signal Model Of An Active-Clamp Forward Converter (Parts 1 to 3), www.How2Power.com, March 2014

- 2.ON Semiconductor NCP1566 page, http://www.onsemi.com/PowerSolutions/product.do?id=NCP1566

- 3.G. Stojcic, F. Lee and S. Hiti, Small-Signal Characterization of Active-Clamp PWM Converters, VPEC 1995, pp. 237-245

- 4.D. Dalal, L. Woofford, Novel Control IC for Single-Ended Active-Clamp Converters, HFPFC'95

Conf. Proc., pp. 136-146, 1995

- 5.Q. Li, F. Lee, M. Jovanović, Design Considerations of Transformer Dc Bias of Forward Converter with Active-Clamp Reset, Applied Power Electronics Conference Conf. Proc., pp. 553-559, March 14-18, 1998

- 6.C. Basso, Switch-Mode Power Supplies: SPICE Simulations and Practical Designs, McGraw-Hill, New-York 2014

- 7.C. Basso, Practical Implementation of Loop Control in Power Converter, Professional Seminar, Applied Power Electronics Conference, Charlotte (NC), 2015

# COMPOTECHAsia 賦書

每週一、三、五與您分享精彩內容

<https://www.facebook.com/lookcompotech>