# 5G 基礎設施和對端到端可程式設計性的需求

■作者：Achronix 供文

## 引言

我們目前處於蜂窩連接的轉型時期，未來無處不在的無線連接正在興起。在全球範圍內，2G、3G 和 4G 的成功推動手機使用量達到了令人難以置信的 75 億部。令人震驚的是，這使得移動設備的數量比全球人口還要多。或許更具影響力的是，蜂窩連接對那些之前被數位化剝奪權利的人產生的影響；例如，2016 年撒哈拉以南非洲地區每 100 人通常有 1 部固定電話，但有 74 台移動連接設備。

展望未來十年，隨著 5G 的出現，無線基礎設施將變得更加普遍，甚至與我們日常生活的方方面面完全融為一體。5G 延續了先前蜂窩標準（在驅動頻寬方面）的模式，但也將其擴展到更多設備和使用模式。

主要趨勢包括：

1. 對增強型移動寬頻 (eMBB) 和其他應用的頻寬增加需求，特別是以 10 倍現有輸送量或者更高速率驅動的暫態可用頻寬。

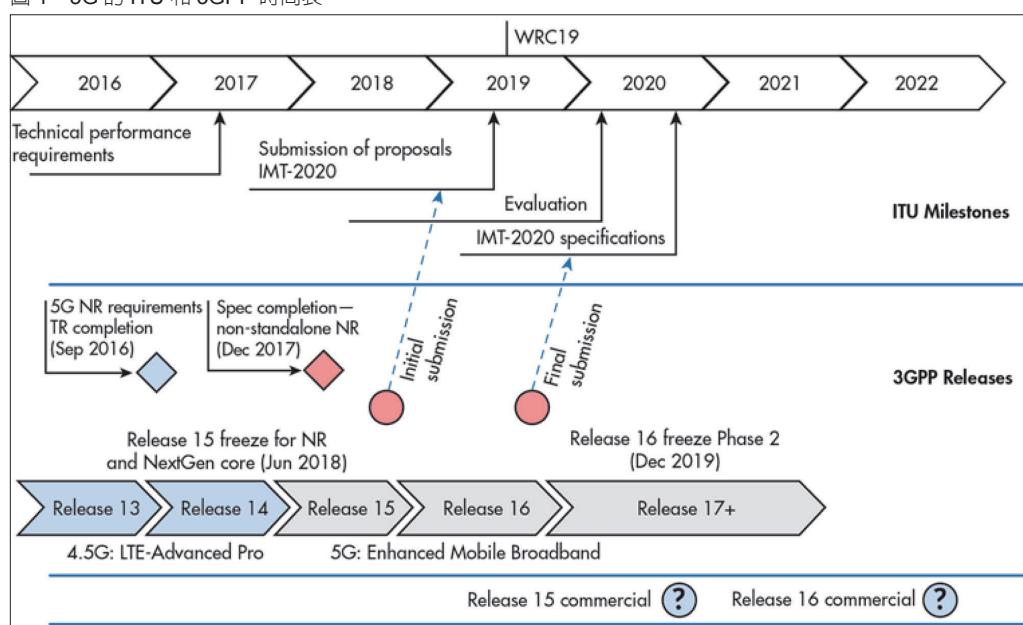

a. 這是 5G 標準化帶來的首波驅動力，其中 3GPP 已於 2017 年完成非獨立（即 LTE 輔助）

新無線電 (NR)，2018 年可提供 5G 獨立版，如圖 1 所示。

- b. 5G 的部署也將根據頻段情況分階段進行，首先部署 6GHz 以下，然後是毫米波 (mmWave) 頻率的連續頻段，以便在稍後階段支援關鍵 eMBB 應用。

- 2. 隨著物聯網 (IoT) 蜂窩網路連接的到來而連接到大量的設備。預計到 2020 年將有 500 億台蜂窩網路連接的設備。這些需求當中的一部分可以通過現有標準滿足，同時也要靠 Release 16 版本中海量機器類通信 (mMTC) 的現有規範去實現了。

- 3. 新的應用模式也在不斷湧現，這對移動設備及其蜂窩無線基礎設施提出了新的要求。示例包括：

- a. 用於連接多個電池供電物聯網端點的低頻寬、

圖 1：5G 的 ITU 和 3GPP 時間表

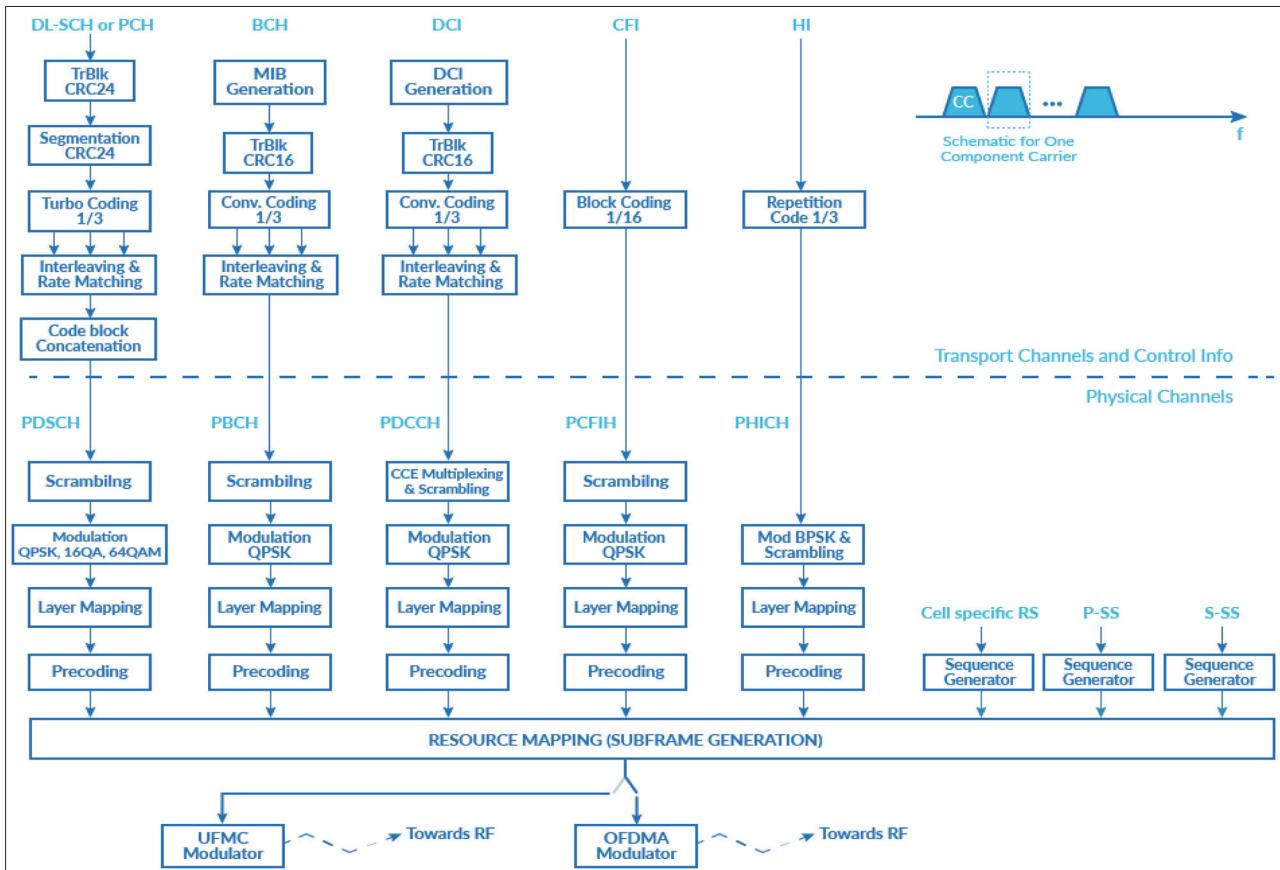

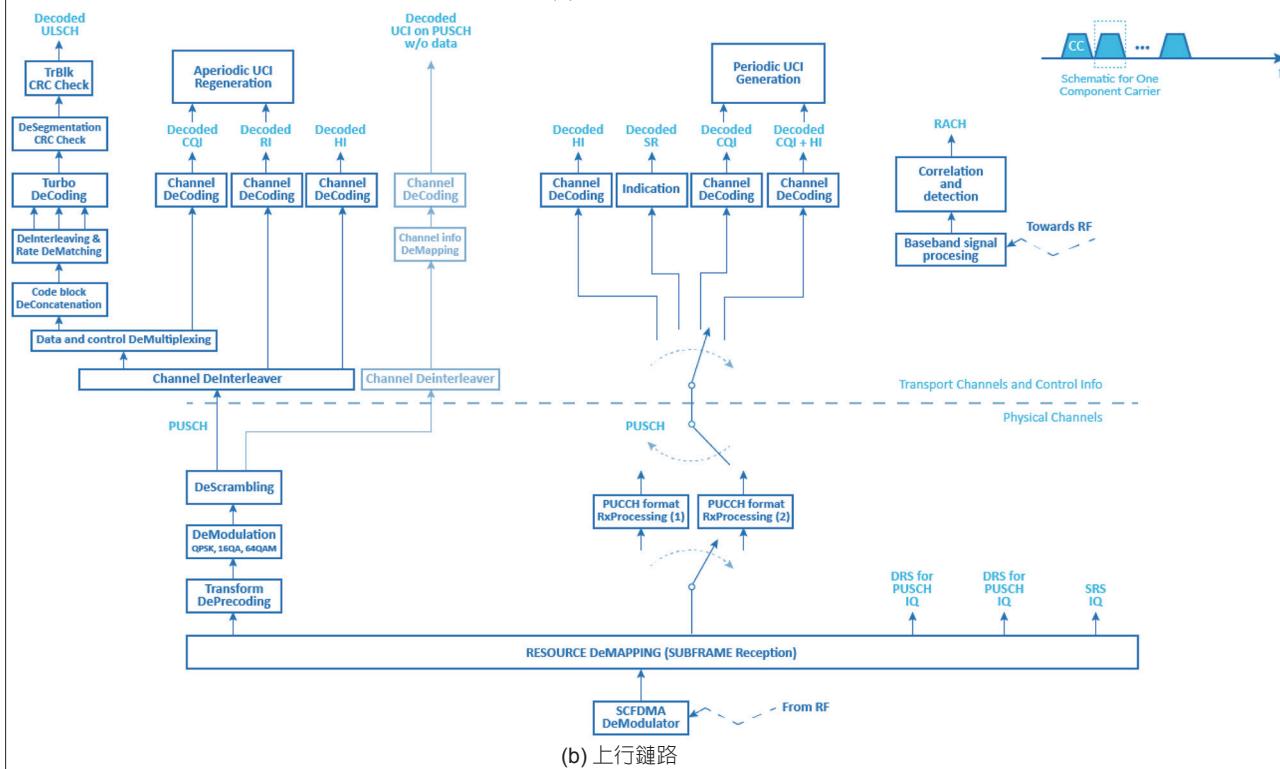

圖 2：基帶處理的高級原理圖

(a) 下行鏈路

低功耗的要求，以實現 mMTC 相關的連接和監控；

- b. 用於車輛到車輛和車輛到基礎設施的連接 (C-V2X) 高可靠性、低延遲蜂窩網路，以補充現有的 V2X 解決方案

- c. 為遠端手術和增強 / 虛擬實境等新興應用提供的高可靠性、低延遲支援

後兩類應用將通過即將推出的 3GPP 超可靠、

低延遲連接 (URLLC) 標準來解決。

4. 對邊緣分析和移動邊緣計算 (MEC) 的新需求。計算重心正在從以前估計的將資料發送到集中式計算資源進行處理，轉變為移到位於資料生成原點附近的分散式運算資源的新範例。造成這種轉變的原因是多方面的：

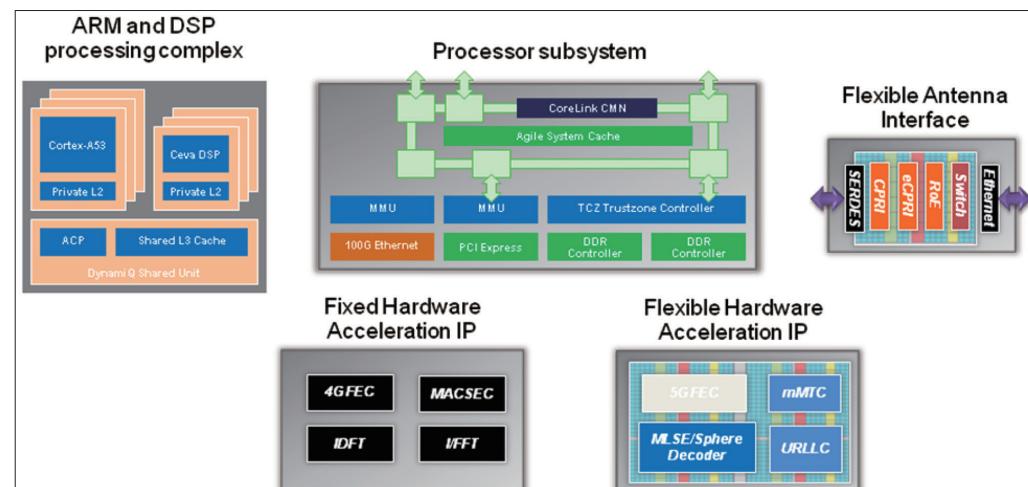

圖 3：關鍵基帶處理元器件

新興應用嚴格的延遲要求、越來越龐大的資料量，以及優化稀缺網路資源的願望等等許多方面。

## 基帶

在本文中，我們考慮如何通過具有高性能 CPU 子系統和包括 FPGA 可重程式設計加速硬體處理單元的 SoC 架構來成功應對 5G 的獨特需求。

基帶從網路介面 (例如乙太網) 獲取資料，並將其轉換為通過前傳 (Fronthaul) 介面傳輸到射頻前端進行傳入 / 傳出的複雜樣本。以下高級原

理圖包括用於 LTE 下行鏈路的發送器 (圖 2a)，以及用於上行鏈路的接收器 (圖 2b)。

## 基帶 L1 處理的案例研究

在這裡，我們舉例說明如何將基帶處理 (尤其是 Layer-1 層) 映射到關鍵處理元器件上，如處理器子系統、CPU 和 DSP 內核，以及固定和靈活的硬體加速，如圖 3 所示。

## 前傳 (天線介面) 連接

除了前面描述的處理元器件之外，還有一個靈活的天線介面功能模組：這是連接基帶和射頻單元所需的元件。傳統上，這是通用公共無線電介面 (CPRI)，有時是開放式基站架構計畫 (OBSAI) 相容

圖 4：可加速 5G 上市時間的分立結構

的部分。

然而，越來越多的方案在轉向指定一個更靈活的前傳介面，以允許基帶和 RF 前端之間的不同映射（如圖 4 所示）。IEEE 對下一代前傳介面 NGFI（IEEE1914）進行了持續的跟進，包括用於基於分組的前傳傳輸網路標準 IEEE1914.1 和乙太網無線電（RoE）包封和映射標準 IEEE1914.1。同時，還有其他行業項目指定了 5G 前傳介面並可共用，例如 eCPRI。

鑑於前傳介面面臨的各種規範、標準和要求，FPGA 很適合其應用，並通常用於支援此介面，如圖 3 所示。

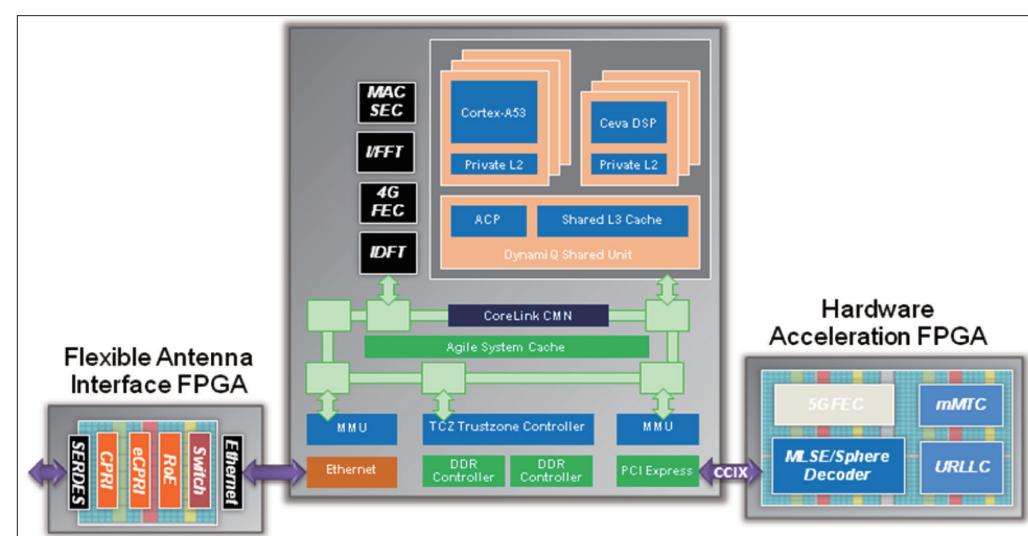

### 可加速 5G 上市時間的分立結構

圖 4 將 5G 所需的處理元器件映射為具有獨立器件的分立式架構，包括 CPU SoC、輔助 FPGA 加速和天線介面。此配置反映了在可以提供經過優化的 5G 專用積體電路（ASIC）之前，可以在 5G 原型設計和早期量產中部署的實施方案。

■ CPU 系統級晶片裡面包括：Arm 處理器組合以及用於 Layer-1 處理和硬化加速器的 DSP 內核，用於固定的、明確定義的功能。

○ 在此示例中，假設現有的 4G ASIC SoC 可用，因此具有通用加速（例如 MACSEC）以及 LTE 特定加速：前向糾錯（特別是 turbo 轉碼器）、

圖 5：基於 Chiplet 的方法可實現更高的集成度

快速傅立葉轉換和離散傅裡葉變換，以在上行鏈路上支持 SC-FDMA。

#### ■ 靈活的天線介面

○ 如前所述，前傳天線介面非常適合用 FPGA 來實現。這是線上配置的，資料從射頻單元發出（在上行鏈路上），然後是被轉換為諸如乙太網等具有標準連接的協定。

#### ■ 硬體加速 FPGA

○ 輔助加速 FPGA 實現了在基帶 SoC 上不可提供的所有必要的計算密集型功能。這可以是 5G 特定的功能或先前未曾規劃的功能。

○ 在此處顯示的示例中，使用了 CCIX 互連。該標準允許基於不同指令集架構的處理器將快取一致性、對等處理的優勢擴展到包括 FPGA 和定制 ASIC 在內的多種加速器件上。

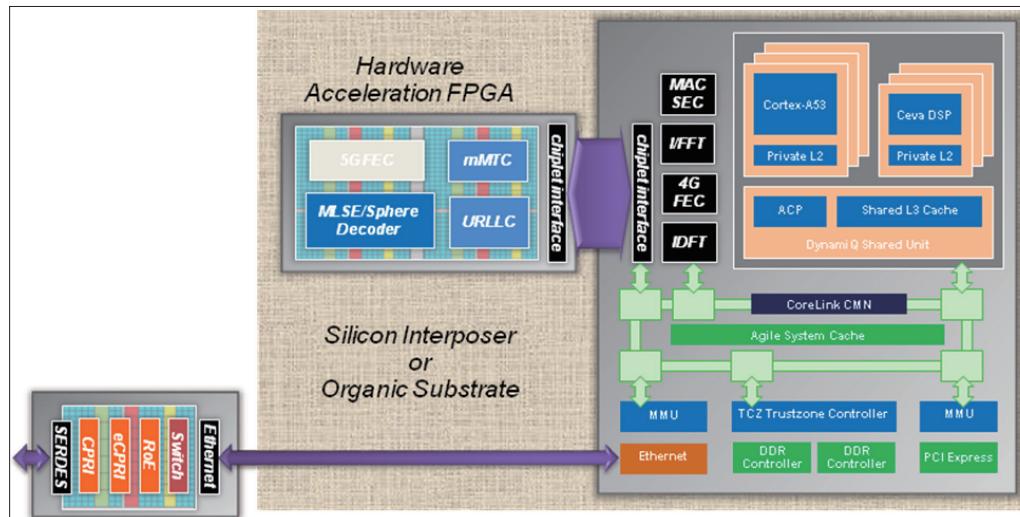

### 基於 Chiplet 的 5G 實現

圖 5 顯示了與圖 4 所示類似的架構，但是使用了基於系統級封裝晶片（chiplet）的方法進行了重新配置。在這種情況下，一個採用了更高頻寬、更低延遲和更低功耗的介面將 CPU SoC 片芯晶粒與輔助硬體加速 chiplet 晶片連接起來。支援前傳連接到射頻單元的 FPGA 器件在該示例中可以但並不是封裝集成在其中的；但實際上，如果有足夠的資源，它可以是與硬體加速 chiplet 晶片相同的 chiplet 器件。

用於封裝集成的兩種主要技術是使用矽仲介層或有機基板，以及某種形式的超短距離（USR）收發器。

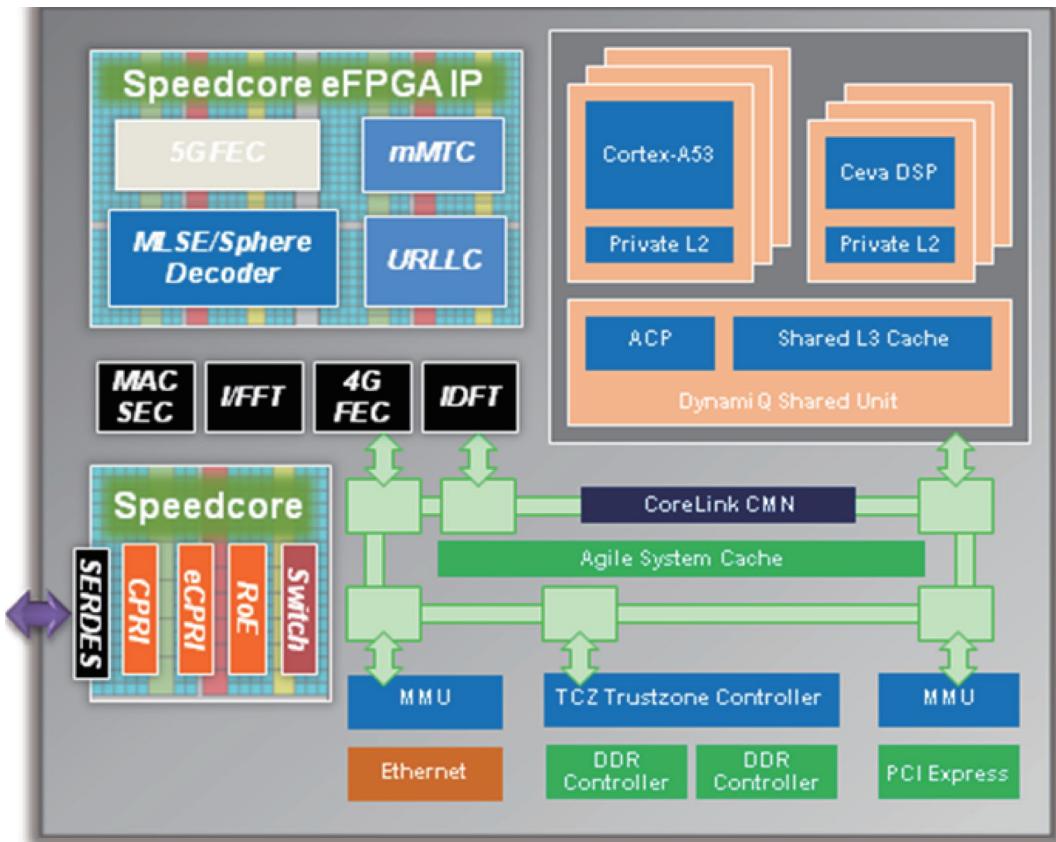

### 完全集成的 5G 實現方式

最後，圖 6 展示了本文考慮的最

圖 6：採用單片集成的、應用於 5G 基帶的異構多核系統級晶片

終、最高集成度的基帶架構。該方法包括與先前相同的處理元件，具有相同的功能，但嵌入式 FPGA (eFPGA) 集成在了晶片內。

這種緊密集成的單片集成方法具有許多優點。與基於 chiplet 的方法相比，該介面具有更高的頻寬、更低的延遲和更低的每比特能耗。此外，資源組合可以根據所考慮的特定應用進行定制，因此避免了不需要的介面、記憶體和核心邏輯單元。這樣可以實現以上所考慮的三種架構中最低單位成本。

如前所述，現在的主要目標是提供更快的上市時間、更高靈活性和未來可用性。之所以能加快了上市時間，是因為 SoC 可以提前流片，因為可以針對 eFPGA 進行後期修改 (例如 5G 標準中 Polar 碼的出現) 而不是完成即固定的 ASIC。來自新演算法或者未預計演算法 (例如新的加密標準) 的靈活性可以通過嵌入式可程式設計邏輯而不是軟體或外部 FPGA 來解決。最後，未來可用性可以延長 SoC

的生命週期，因為諸如 URLLC 和 mMTC 等新標準等大批量新興需求可以通過現有產品解決，而不需要進行新的開發。

## 總結

CPU 和可程式設計加速 (嵌入式或獨立 FPGA) 的緊密耦合，使開發人員能夠去創建可以一個應用於多個不同市場的平臺產品。這增加了特定產品的市場適用性並提高了開發投資回報。這甚至可

以在流片後再對市場進行定位 (或重新定位)，即最大化的可程式設計性所提供的內在靈活性可支援相當大的創新空間。

或許從 5G 的角度來看更為重要的是，高度可程式設計的解決方案可以加快產品上市速度。例如，在標準最終確定之前，不再需要推遲 SoC 的流片時間，後續改變的需求可以在軟體或可程式設計硬體中實現。這對於早期 5G 部署所面臨並在不斷增加的壓力，以及應對新標準的不斷湧現，這是一個突出優勢。 CTA