# SPI 介面簡介

■作者：Piyu Dhaker

ADI 北美核心應用部門的應用工程師

串列周邊介面 (SPI) 是微控制器和週邊 IC( 如感測器、ADC、DAC、移位暫存器、SRAM 等 ) 之間使用最廣泛的介面之一。本文將首先簡要說明 SPI 介面，之後將介紹 ADI 支援 SPI 的類比切換開關與多路轉換器，以及它們如何說明減少系統電路板設計中的數位 GPIO 數量。

SPI 是一種同步、全雙工、主從式介面。來自主控端 (master) 或從屬端 (slave) 的資料在時脈升緣或降緣同步。主控端和從屬端可以同時傳輸資料。SPI 介面可以是 3 線式或 4 線式。本文將重點介紹常用的 4 線 SPI 介面。

## 介面

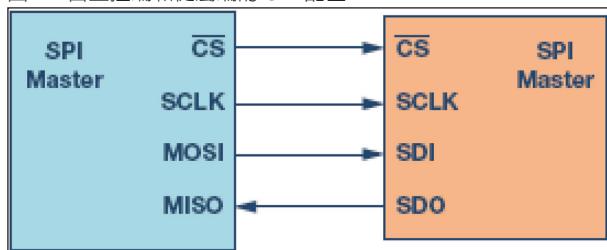

圖 1：含主控端和從屬端的 SPI 配置

4 線 SPI 元件具備四個訊號：

- 時脈 (SPI CLK, SCLK)

- 片選 (CS)

- 主控端輸出、從屬端輸入 (MOSI)

- 主控端輸入、從屬端輸出 (MISO)

產生時脈訊號的元件稱為主控端。主控端和從屬端之間傳輸的資料與主控端產生的時脈同步。相較於 I<sup>2</sup>C 介面，SPI 元件可支援更高的時脈頻率。使用者可查閱產品資料手冊，以瞭解 SPI 介面的時脈頻率規格。

SPI 介面只能有一個主控端，但可以有一個或多個從屬端。圖 1 顯示了主控端和從屬端之間的 SPI 連接。

來自主控端的片選訊號用於選擇從屬端。這通常是一個低位準有效訊號，拉高時從屬端與 SPI 匯流排斷開連接。當使用多個從屬端時，主控端需要為每個從屬端提供單獨的片選訊號。本文中所提到的片選訊號，則始終是低位準有效訊號。

MOSI 和 MISO 是數據線。MOSI 主要將資料從主控端發送到從屬端，而 MISO 則是將資料從從屬端發送到主控端。

## 資料傳輸

要開始 SPI 通訊時，主控端必須發送時脈訊號，並透過致能 CS 訊號選擇從屬端。片選通常是低位準有效訊號。因此，主控端必須在該訊號上發送邏輯 0 以選擇從屬端。SPI 是全雙工介面，主控端和從屬端可以分別透過 MOSI 和 MISO 線路同時發送資料。在 SPI 通訊期間，資料的發送 ( 串列移出到 MOSI/SDO 匯流排上 ) 和接收 ( 採樣或讀入匯流排 (MISO/SDI) 的資料 ) 是同時進行的。串列時脈緣則同步資料的移位元和採樣。SPI 介面允許使用者靈活選擇時脈的升緣或降緣來採樣和 / 或移位資料。欲確定使用 SPI 介面傳輸的資料位元數時，請參閱元件產品資料手冊。

## 時脈極性和時脈相位

在 SPI 中，主控端可以選擇時脈極性和時脈相位。在空閒狀態期間，CPOL 位元設定時脈訊號的極性。空閒狀態是指傳輸開始時 CS 為高位準且

表 1：透過 CPOL 和 CPHA 選擇 SPI 模式

| SPI 模式 | CPOL | CPHA | 空閒狀態下的時脈極性 | 用於採樣和 / 或移位資料的時脈相位 |

|--------|------|------|------------|--------------------|

| 0      | 0    | 0    | 邏輯低位準      | 資料在升緣採樣，在降緣移出      |

| 1      | 0    | 1    | 邏輯低位準      | 資料在降緣採樣，在升緣移出      |

| 2      | 1    | 1    | 邏輯低位準      | 資料在降緣採樣，在升緣移出      |

| 3      | 1    | 0    | 邏輯低位準      | 資料在升緣採樣，在降緣移出      |

在向低位準轉變的期間，以及傳輸結束時 CS 為低準且在向高位準轉變的期間。CPHA 位元選擇時脈相位。根據 CPHA 位元的狀態，使用時脈升緣或降緣來採樣和 / 或移位資料。主控端必須根據從屬端的要求選擇時脈極性和時脈相位。根據 CPOL 和 CPHA 位元的選擇，有四種 SPI 模式可用。表 1 顯示了這 4 種 SPI 模式。

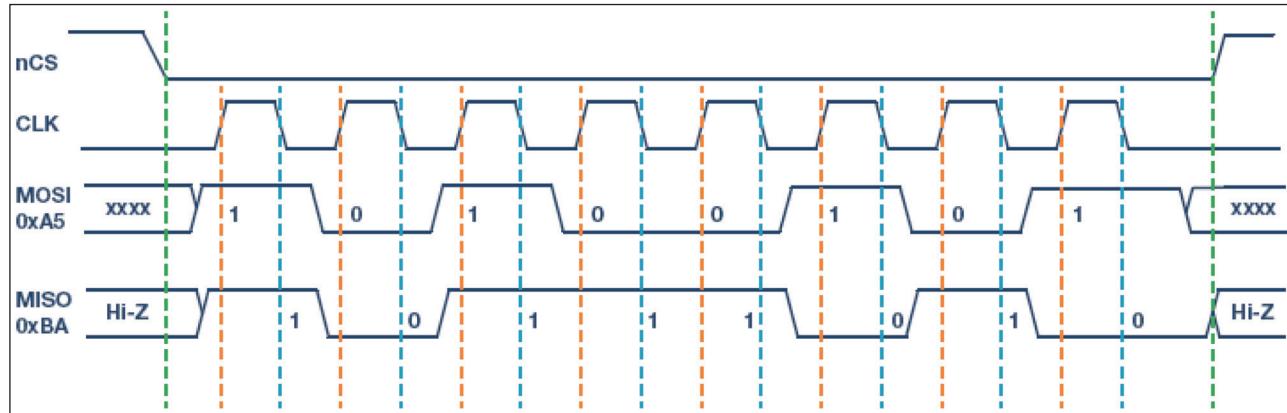

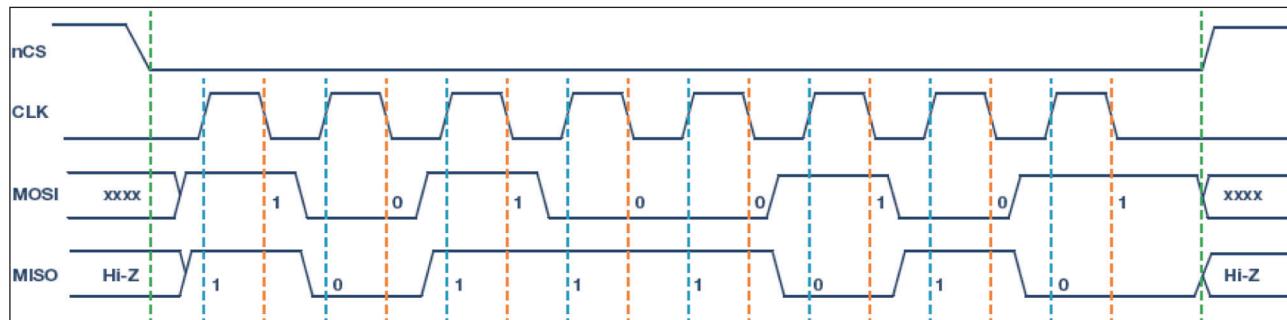

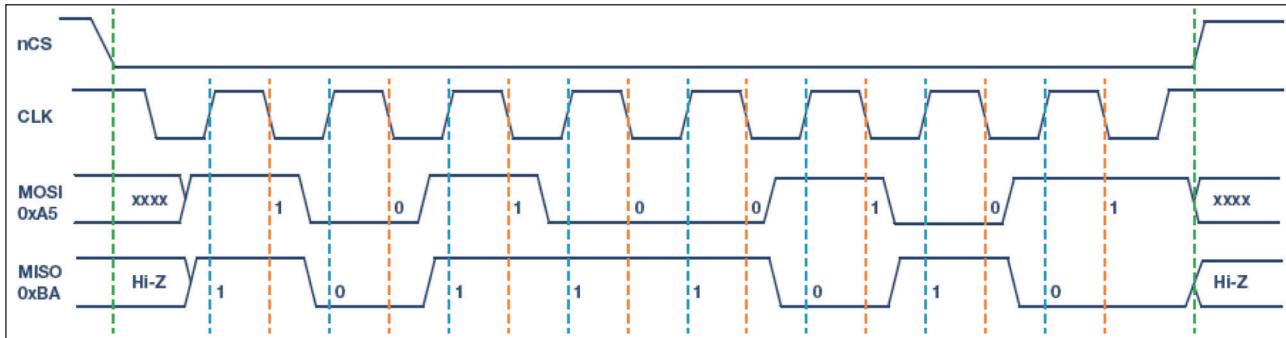

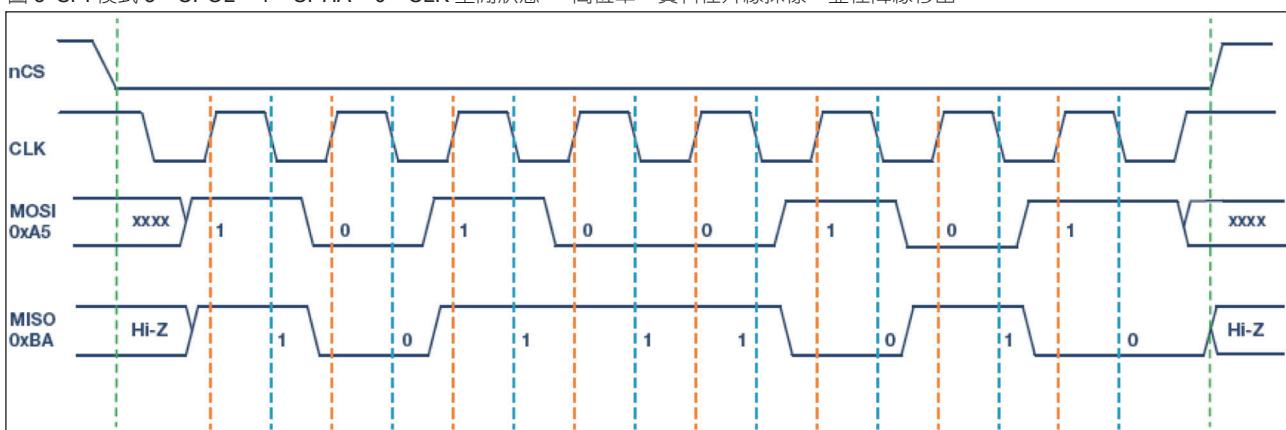

圖 2 至圖 5 顯示了四種 SPI 模式下的通訊示意。在這些示意中，資料顯示在 MOSI 和 MISO 線上。傳輸的開始和結束用綠色虛線表示，採樣邊緣用橙色虛線表示，移位邊緣用藍色虛線表示。請注意，這些圖形僅供參考。要成功地進行 SPI 通訊，使用者須參閱產品資料手冊並確保滿足元件的時序規格。

圖 3 所示為 SPI 模式 1 的時序圖。在此模式下，

圖 2:SPI 模式 0，CPOL = 0，CPHA = 0 : CLK 空閒狀態 = 低位準，資料在升緣採樣，並在降緣移出。

圖 3:SPI 模式 1，CPOL = 0，CPHA = 1 : CLK 空閒狀態 = 低位準，資料在降緣採樣，並在升緣移出。

時脈極性為 0，表示時脈訊號的空閒狀態為低準。此模式下的時脈相位為 1，表示資料在降緣採樣（由橙色虛線顯示），並且資料在時脈訊號的升緣移出（由藍色虛線顯示）。

圖 4 給出了 SPI 模式 2 的時序圖。在此模式下，時脈極性為 1，表示時脈訊號的空閒狀態為高準。此模式下的時脈相位為 1，表示資料在降緣採樣（由橙色虛線顯示），並且資料在時脈訊號的升緣移出（由藍色虛線顯示）。

圖 5 所示為 SPI 模式 3 的時序圖。在此模式下，時脈極性為 1，表示時脈訊號的空閒狀態為高準。此模式下的時脈相位為 0，表示資料在升緣採樣（由橙色虛線顯示），並且資料在時脈訊號的降緣移出（由藍色虛線顯示）。

## 多從屬端 (Multislave) 配置

多個從屬端可與單個 SPI 主控端一起使用。從

圖 4: SPI 模式 2, CPOL = 1, CPHA = 1 : CLK 空間狀態 = 高位準，資料在降緣採樣，並在升緣移出。

圖 5: SPI 模式 3, CPOL = 1, CPHA = 0 : CLK 空間狀態 = 高位準，資料在升緣採樣，並在降緣移出。

屬端可以採用常規模式連接，或採用菊鏈模式連接。

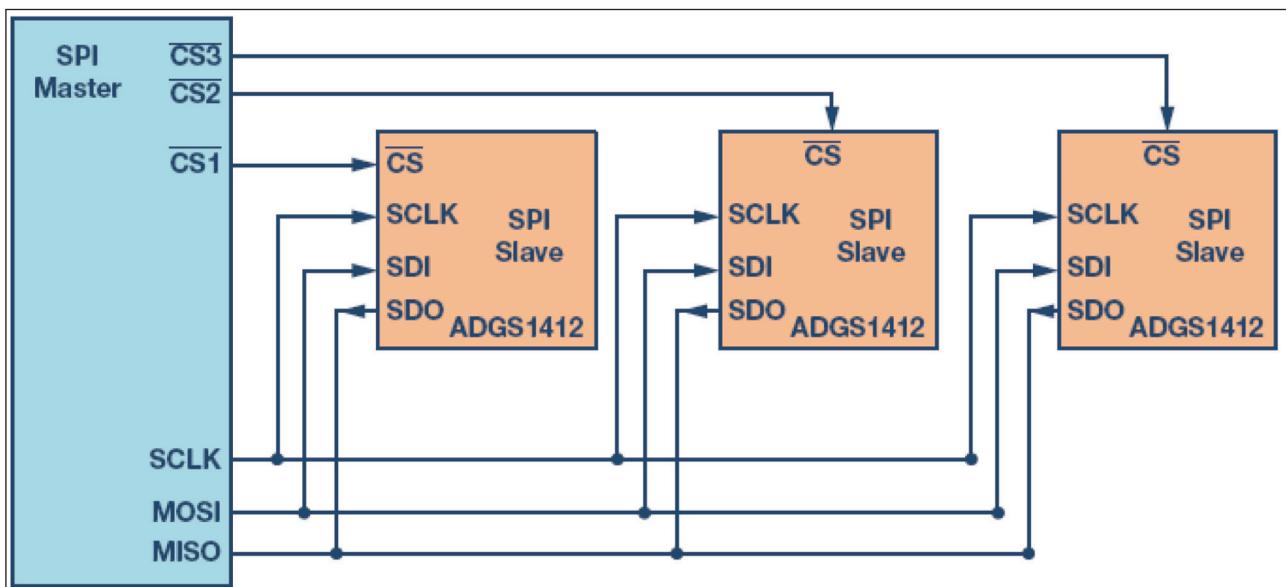

## 常規 SPI 模式：

在常規模式下，主控端需要為每個從屬端提供

單獨的片選訊號。一旦主控端致能(拉低)片選訊號，MOSI/MISO 線上的時脈和資料便可用於所選的從屬端。如果致能多個片選訊號，則 MISO 線上的資料會被破壞，因為主控端無法識別哪個從屬端正在傳

圖 6: 多從屬端 SPI 配置

輸資料。

從圖 6 可以看出，隨著從屬端數量的增加，來自主控端的片選線的數量也增加。這會快速增加主控端需要提供的輸入和輸出數量，並限制可以使用的從屬端數量。使用其他技術來增加常規模式下的從屬端數量是可行的，例如使用多工器產生片選訊號。

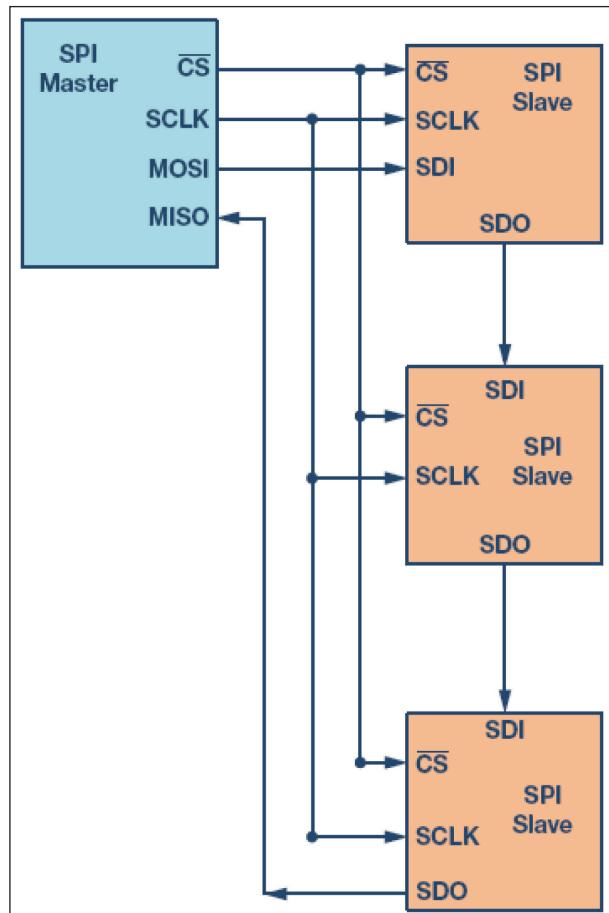

### 菊鏈模式：

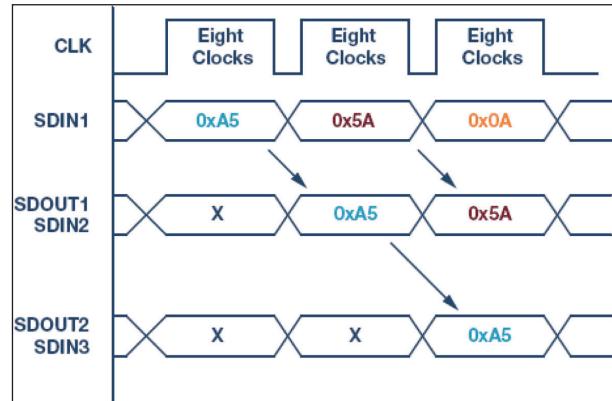

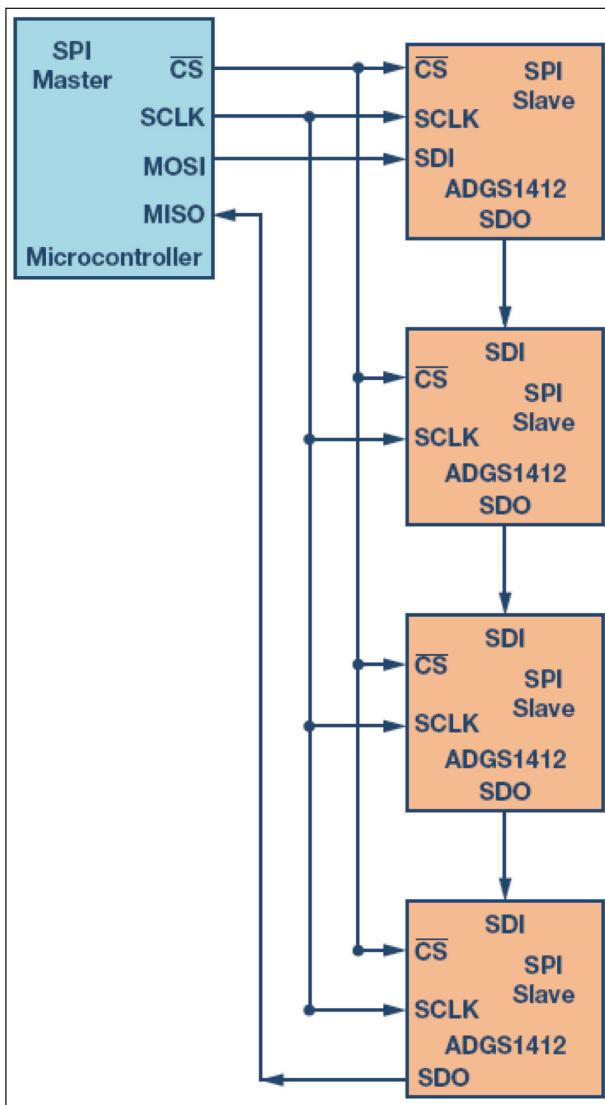

在菊鏈模式下，所有從屬端的片選訊號連接在一起，資料從一個從屬端傳播到下一個從屬端。在此配置中，所有從屬端同時接收同一 SPI 時脈。來自主控端的資料直接送到第一個從屬端，該從屬端將資料提供給下一個從屬端，依此類推。

使用該方法時，由於資料是從一個從屬端傳播到下一個從屬端，所以傳輸資料所需的時脈週期數

圖 7: 多從屬端 SPI 菊鏈配置

圖 8: 菊鏈配置：資料傳播

與菊鏈中的從屬端位置成比例。例如在圖 7 所示的 8 位元系統中，為使第 3 個從屬端能夠獲得資料，需要 24 個時脈脈衝，而常規 SPI 模式下只需 8 個時脈脈衝。圖 8 顯示了時脈週期和通過菊鏈的資料傳播。並非所有 SPI 元件都支援菊鏈模式。請參閱產品資料手冊以確認菊鏈是否可用。

### ADI 支援 SPI 的類比切換開關與多路轉換器

ADI 最新一代支援 SPI 的切換開關可在不影響精密切換開關性能的情況下大幅節省空間。本文的此部分將討論一個案例研究，說明支援 SPI 的切換開關或多工器如何能夠具體簡化系統級設計，並減少所需的 GPIO 數量。

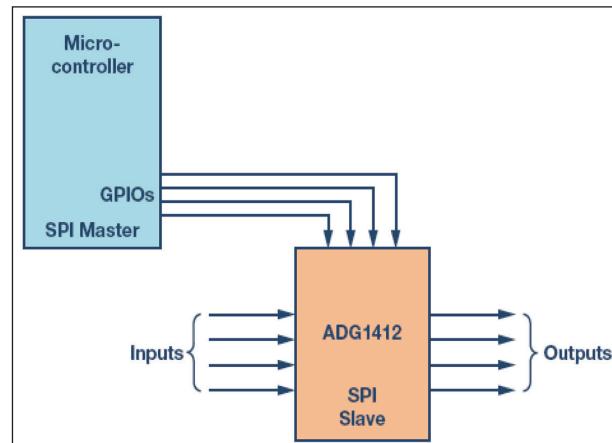

ADG1412 是一款四通道、單刀單擲 (SPST) 切換開關，需要四個 GPIO 連接到每個切換開關的控

圖 9: 微控制器 GPIO 用作切換開關的控制訊號。

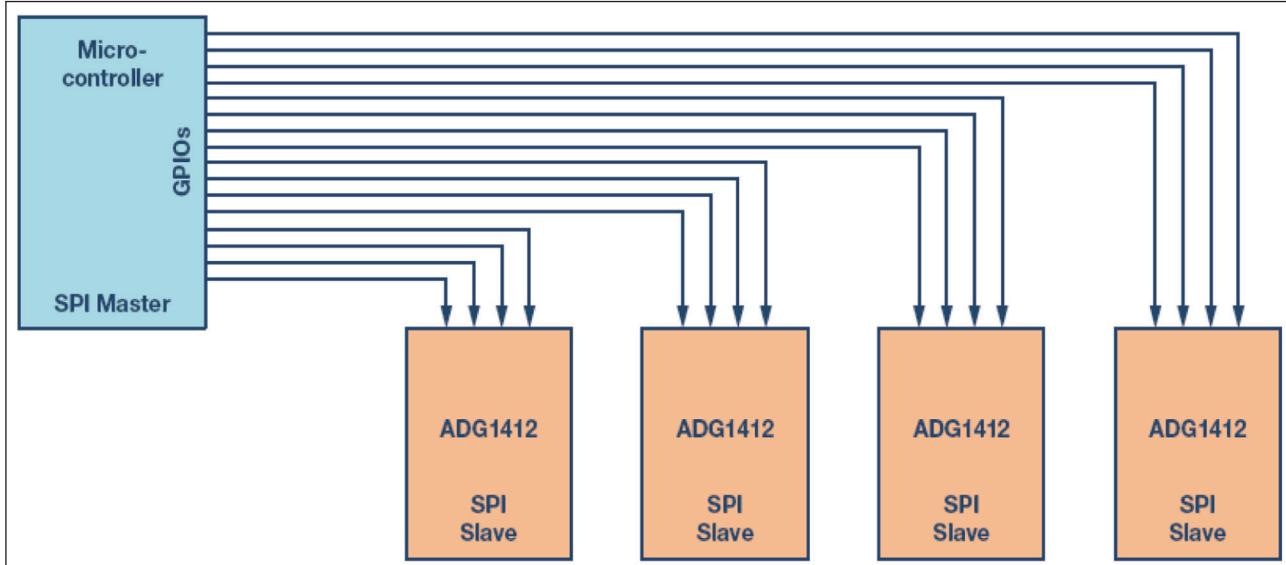

圖 10：在多從屬端配置中，所需 GPIO 的數量大幅增加。

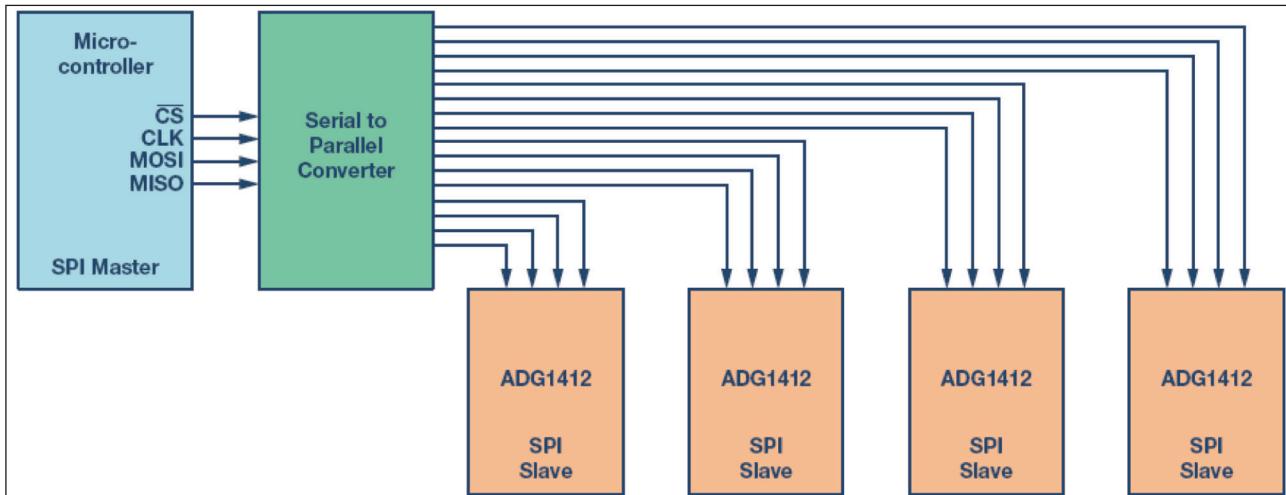

圖 11：使用串列轉平行轉換器的多從屬端切換開關

制輸入。圖 9 顯示了微控制器和一個 ADG1412 之間的連接。

隨著電路板上切換開關數量的增加，所需 GPIO 的數量也會顯著增加。例如，當設計一個測試儀器系統時，會使用大量切換開關來增加系統中的通道數。在  $4 \times 4$  交叉點矩陣配置中，使用四個 ADG1412。此系統需要 16 個 GPIO，限制了標準微控制器中的可用 GPIO。圖 10 顯示了使用微控制器的 16 個 GPIO 連接四個 ADG1412。

為了減少 GPIO 數量，其中一種方法是使用串列轉平行轉換器，如圖 11 所示。該元件輸出的平行訊號可連接到切換開關控制輸入，元件可透過序列

介面 SPI 配置。此方法的缺點是外加元件會導致物料清單增加。

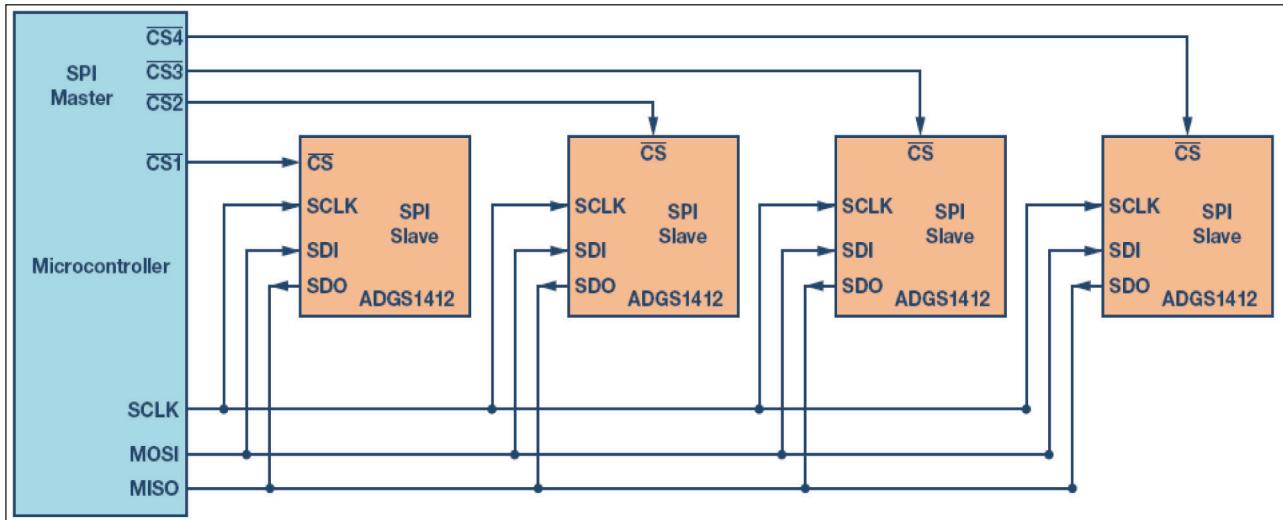

另一種方法是使用 SPI 控制的切換開關。此方法的優點是可減少所需 GPIO 的數量，並且還能消除外加串列轉平行轉換器的開銷。如圖 12 所示，不需要 16 個微控制器 GPIO，只需要 7 個微控制器 GPIO 就可以向 4 個 ADGS1412 提供 SPI 訊號。

切換開關可採用菊鏈配置，以進一步優化 GPIO 數量。在菊鏈配置中，無論系統使用多少切換開關，都只使用主控端（微控制器）的四個 GPIO。

圖 13 用於說明目的。ADGS1412 資料手冊建議在 SDO 針腳上使用一個上拉電阻。有關菊鏈模

圖 12：支援 SPI 的切換開關節省微控制器 GPIO

圖 13：菊鏈配置的 SPI 切換開關可進一步優化 GPIO。

式的更多資訊，請參閱 ADGS1412 產品資料手冊。為簡單起見，此示例使用了四個切換開關。隨著系統中切換開關數量的增加，電路板簡單和節省空間的優點很重要。在 6 層電路板上放置 8 個四通道 SPST 切換開關，採用  $4 \times 8$  交叉點配置時，ADI 支援 SPI 的切換開關可節省 20% 的總電路板空間。在文章“精密 SPI 切換開關配置提高通道密度”中，即詳細說明了精密 SPI 切換開關配置如何提高通道密度。

### 參考文獻

- ADuCM3029 產品手冊。ADI 公司，2017 年 3 月。

- Nugent, Stephen。“精密 SPI 切換開關配置提高通道密度”。《類比對話》，2017 年 5 月。

- Usach, Miguel。應用筆記 AN-1248：SPI 介面。ADI 公司，2015 年 9 月。[CTA](#)