# 可編程設計增益儀錶放大器：尋找合適的元件

■作者：Kristina Fortunado

ADI 線性產品與解決方案部門的產品應用工程師

## 簡介

資料擷取系統 (DAQ) 在許多業界應用廣泛，例如研究、分析、設計驗證、製造和測試等。這些系統與各種感測器介面也為前端設計帶來了挑戰。考慮不同感測器的靈敏度是必要的，例如，系統可能需要連接最大輸出為 10 mV 和靈敏度為微伏以下的負載感測器，同時還要連接針對 10 V 輸出而預處理的感測器。當只有一個增益時，系統需要具有非常高的解析度來檢測兩個輸入。即便如此，在最低輸入時訊號雜訊比 (SNR) 也會受影響。

在這些應用中，可編程增益儀錶放大器 (PGIA) 是適合前端的解決方案，可適應各種感測器介面的靈敏度，同時優化 SNR。整合式 PGIA 可實現良好的直流和交流規格。本文討論各種整合式 PGIA 及

表 1：可編程設計增益儀錶放大器規格

|              | AD825x                                                          | AD8231           | LTC6915                    |

|--------------|-----------------------------------------------------------------|------------------|----------------------------|

| 增益設定         | 1、2、5、10 (AD8250)<br>1、2、4、8 (AD8251)<br>1、10、100、1000 (AD8253) | 1 到 128，步長為 6 dB | 1 到 4096，步長為 6 dB          |

| CMRR (G = 1) | 80 dB                                                           | 80 dB            | 125 dB                     |

| 增益漂移         | 10 ppm/°C                                                       | 10 ppm/°C        |                            |

| 靜態電流         | 4.5 mA                                                          | 4 mA             | 2 mA                       |

| 頻寬           | 10 MHz                                                          | 2.7 MHz          | 200 kHz                    |

| 建立時間         | 0.78µs                                                          | 4 µs             |                            |

| 失調電壓 (G=1)   | 1.05 mV                                                         | 45 µV            | 10 µV                      |

| 失調電壓漂移       | 6.2 µV/°C                                                       | 50 nV/°C         | 0 nV/°C                    |

| 輸入偏置電流       | 50 nA                                                           | 500 pA           | 10 nA                      |

| 雜訊 (G=1)     | 45 nV/√Hz                                                       | 66 nV/√Hz        | 2.5 µV 峰峰 (0.1 Hz 至 10 Hz) |

| 增益非線性        | 6 ppm                                                           | 3 ppm            | 15 ppm                     |

| 軌對軌輸入        | 否 (-Vs+1) 至 (+Vs-1.5)                                           | 是 (超出供電軌 0.2 V)  | 是                          |

其優勢。文中並會討論相關的限制，以及為滿足特定要求而構建分立 PGIA 時應遵循的指導原則。

## 整合 PGIA

ADI 的產品系列中具備許多整合式 PGIA。整合式 PGIA 具有設計階段更短、尺寸更小的優勢。數位可調增益可透過內部精密電阻陣列而實現。為了優化增益、CMRR 和失調，可以對這些電阻陣列進行晶片內調整，以獲得良好的整體直流性能。同時，還可運用設計技巧來實現精小的 IC 佈局，使寄生效應最小，並提供出色的匹配，產生良好的交流性能。由於這些優點，如果有符合設計要求的 PGIA，強烈建議選擇此類元件。表 1 列出了可用的整合式 PGIA 以及其關鍵規格。

## PGIA

的選擇取決於應用。AD825x 由於具有快速建立時間和高壓擺率，在多工系統中非常有用。AD8231 和 LTC6915 採用零漂移架構，適用於需要在很

表 2:DAQ 系統規格

|               | ADAS3022                           | ADAS3023                  | AD7124-8                                                  |

|---------------|------------------------------------|---------------------------|-----------------------------------------------------------|

| 描述            | 16 位元、1 MSPS、8 通道 DAQ 系統           | 16 位元、8 通道同步採樣 DAQ 系統     | 整合 PGA 和參考電壓源的 8 通道、低雜訊、低功耗 24 位元 $\Sigma - \Delta$ 型 ADC |

| Gain Settings | 0.16, 0.2, 0.4, 0.8, 1.6, 3.2, 6.4 | 0.2, 0.4, 0.8, 1.6        | 1 到 128，步長為 6 dB                                          |

| 增益設定          | 0.16、0.2、0.4、0.8、1.6、3.2、6.4       | 0.2、0.4、0.8、1.6           |                                                           |

| CMRR (G=1)    | 90 dB                              | 95 dB                     | 85 dB                                                     |

| 增益漂移          | 0.1 ppm/ $^{\circ}\text{C}$        | 1 ppm/ $^{\circ}\text{C}$ | 2 ppm/ $^{\circ}\text{C}$                                 |

| 功耗 (最大增益)     | 12 mA                              | 10.5 mA                   | 1.2 mA                                                    |

| 轉換速率 (最大通道數)  | 125 kSPS                           | 125 kSPS                  | 19.2 kSPS(全功率)                                            |

寬廣的溫度範圍內提供精度性能的系統。

另外，還有許多元件整合多工器、PGIA 和 ADC 以形成完整的 DAQ 解決方案。實例有 ADAS3022、ADAS3023 和 AD7124-8。

這些解決方案的選擇主要取決於輸入訊號源的規格。AD7124-8 針對需要極高精度的慢速應用而設計，例如溫度和壓力測量。ADAS3022 和 ADAS3023 適用於相對較高頻寬的應用，例如程序控制或電力線監控，但其功耗高於 AD7124-8。

## 實現分立式 PGIA

一些系統可能有一兩個規格是上述整合元件無法滿足的。通常，若存在以下要求，則使用者需要利用分立式元件構建自己的 PGIA：

- 需要更高頻寬的多工系統，掃描速率非常高

- 超低功耗

- 系統需要客製的增益或衰減

- 高阻抗感測器的低輸入偏置電流

- 極低雜訊

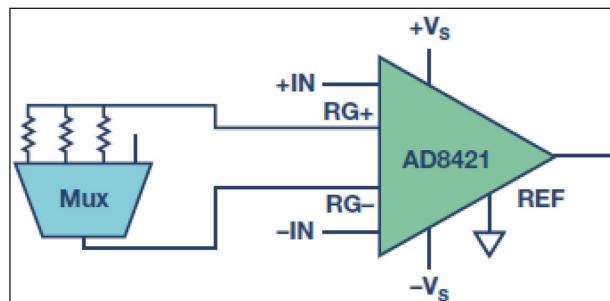

圖 1:AD8421 和用於切換增益的多工器

設計分立式 PGIA 常用的方法之一是使用具有所需輸入特性的儀錶放大器，例如低雜訊 AD8421，並搭配一個多工器來切換增益電阻以改變增益。

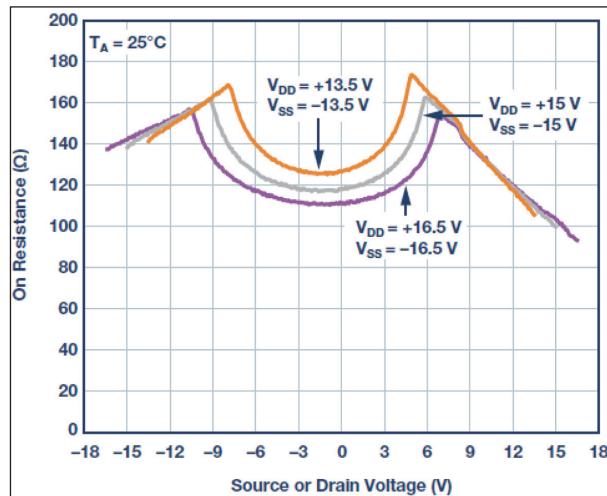

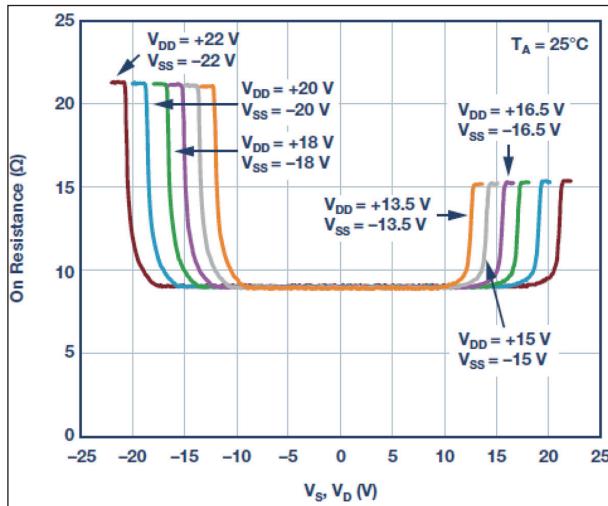

在這種配置中，多工器的導通電阻實際上與增益電阻串聯。該導通電阻隨漏極上的電壓而改變，這就產生了一個問題。圖 2 取自 ADG1208 產品手冊，其展示了這種關係。

圖 2:ADG1208 的導通電阻與漏極電壓的關係

導通電阻和增益電阻的串聯組合導致增益出現非線性誤差。這意味著增益將隨共模電壓而變化，這是很不好的。例如，AD8421 需要  $1.1 \text{ k}\Omega$  的增益電阻以獲得 10 倍增益。對於 ADG1208，當源極或漏極電壓改變  $\pm 15 \text{ V}$  時，導通電阻變化幅度高達  $40\Omega$ ，由此產生的增益非線性誤差約為 3%。若增益更大，該誤差將變得更加明顯，導通電阻甚至可能

表 3: 多工器中導通電阻與電容的權衡

|               | ADG1208 | ADG1408 |

|---------------|---------|---------|

| 導通電阻 (典型值)    | 120 Ω   | 4 Ω     |

| 漏極和源極電容 (典型值) | 7 pF    | 135 pF  |

變得與增益電阻相當。

或者，可以使用低導通電阻的多工器來降低這種影響，但相對的代價是輸入電容會更高。表 3 透過比較 ADG1208 和 ADG1408 說明了這一點。

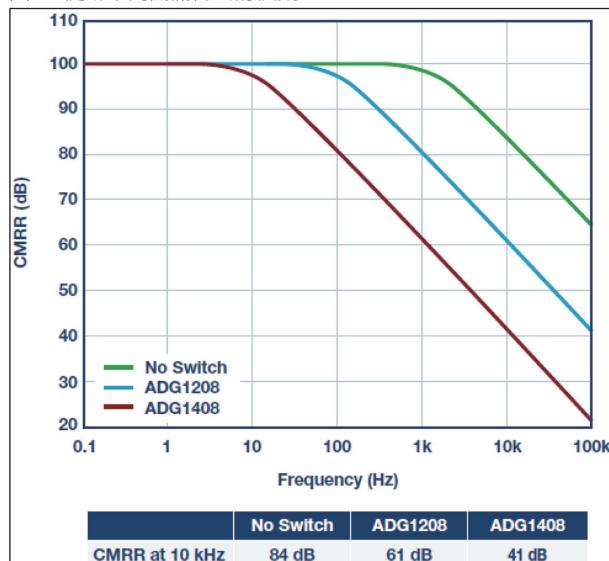

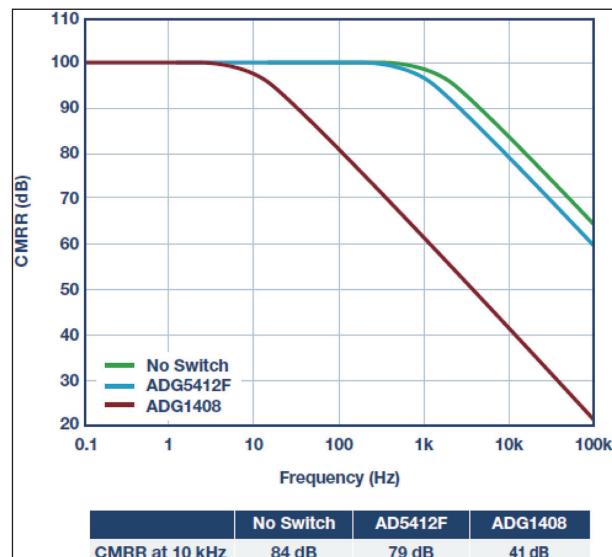

切換開關的輸入電容會導致圖 1 所示配置產生另一個問題，因為任何給定三引腳運放儀錶放大器上的 RG 針腳都對電容非常敏感。切換開關電容可能導致該電路出現峰化或不穩定。更大的問題是 RG 針腳上的電容不平衡導致交流共模抑制比 (CMRR) 降低，而 CMRR 是儀錶放大器的一項關鍵規格。圖 3 中的模擬圖顯示了 AD8421 的增益針腳上使用不同多工器時 CMRR 的降低情況。該圖清楚地表明，隨著電容的增加，CMRR 降幅更大。

圖 3: 使用不同開關得到的模擬 CMRR

為了減小交流 CMRR 降幅，最好的解決方案是確保 RG 針腳具有相同的阻抗。這可以透過平衡電阻並將切換開關元件放置在兩個電阻之間來實現，如圖 4 所示。在這種情況下，由於切換開關兩端固有的電容不平衡，多工器不發揮作用。此外，由於多工器的漏極短接在一起，RG 針腳的一側只能使用一個電阻，這仍然會導致不平衡。

圖 4: 使用平衡配置的分立 PGIA

在這種情況下，建議使用四通道 SPST 切換開關，例如 ADG5412F。除了切換開關支援靈活地使用平衡電阻之外，漏極和源極的電容也是平衡的，CMRR 降幅因此減小。圖 5 比較了 AD8421 的增益針腳上使用多工器與使用四通道 SPST 開關兩種情況下的交流 CMRR。

ADG5412F 還具有低導通電阻特性，其在漏極或源極電壓範圍內非常平坦，如圖 6 所示。在漏極

圖 5: SPST 切換開關與多工器配置兩種情況下的 CMRR 模擬

圖 6: ADG5412F 的導通電阻與共模電壓的關係

或源極電壓範圍內，其額定最大值為  $1.1\Omega$ 。回到最初的例子，AD8421 的增益為 10，增益電阻為  $1.1\text{ k}\Omega$ ，切換開關只會引入 0.1% 的增益非線性。儘管如此，仍有一個漂移分量，其在更高增益時會更加明顯。

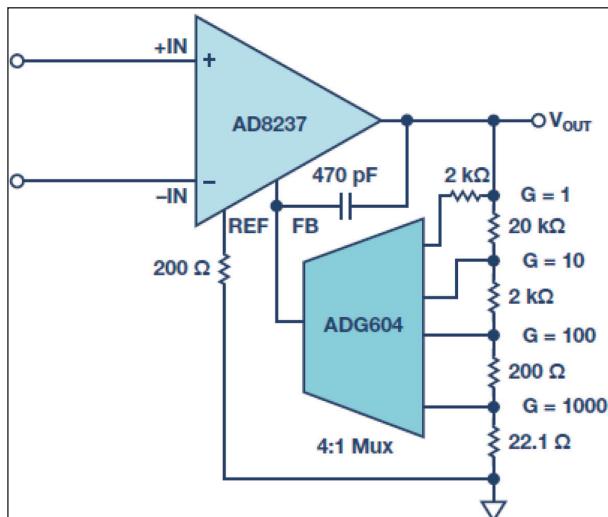

為了消除切換開關的寄生電阻效應，可以使用不同架構的儀錶放大器來實現任意增益。AD8420 和 AD8237 採用間接電流回饋 (ICF) 架構，是要求低功耗和低頻寬的應用的出色選擇。在這種配置中，開關置於高阻抗感測路徑中，因此增益不受開關導通電阻變化的影響。

這些放大器的增益是透過外部電阻的比率來設定的，設定方式與同相放大器相同，而這就為用戶

圖 7: 採用間接電流回饋的儀錶放大器的分立式 PGIA

提供了更高的彈性，因為增益設置電阻可以根據設計要求來選擇。標準薄膜或金屬膜電阻的溫度係數可低至  $15 \text{ ppm}/^\circ\text{C}$ ，相應的增益漂移要比使用單個外部電阻設置增益的標準儀錶放大器更好，後者的晶片內和外部電阻之間的不匹配通常會將增益漂移限制在  $50 \text{ ppm}/^\circ\text{C}$  左右。為獲得最佳增益誤差和漂移性能，可以使用電阻網路進行容差和溫度係數跟蹤。不過，這要以犧牲成本為代價，因此除非確有需要，否則應優先選擇分立電阻。

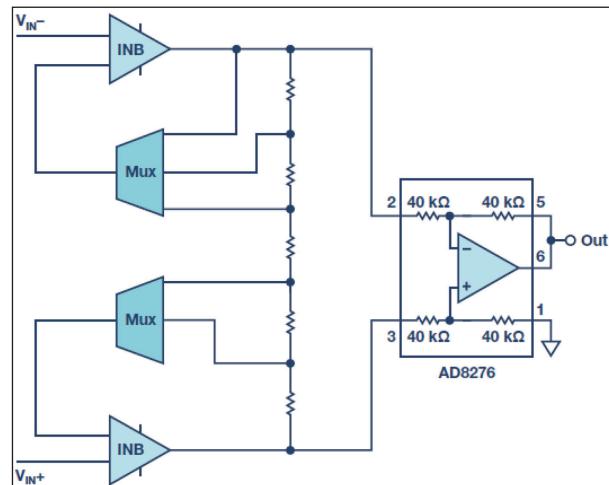

另一種解決方案，也是提供最大彈性的解決方案，是採用分立元件的三運放儀錶放大器架構，如圖 8 所示，透過多工器切換增益電阻。相較於儀錶放大器，運算放大器可供選擇的範圍要大得多，因此設計人員有更多選擇，這使他們能夠圍繞特定設計要求進行設計。濾波等特殊功能也可以內建於第一級中。第二級的差動放大器使此種架構達到完善。

圖 8: 分立 PGIA

輸入放大器的選擇直接取決於 DAQ 要求。例如，低功耗設計需要使用低靜態電流的放大器，而預期輸入端會有高阻抗感測器的系統，則可以利用超低偏置電流的放大器來最大限度地減少誤差。應使用雙放大器以更良好地追蹤溫度。

可以注意到，當使用圖 8 所示配置時，切換開關的導通電阻也與放大器的高阻抗輸入串聯，因此它不會影響增益。回顧導通電阻與開關輸入電容之間的權衡，由於對導通電阻的限制不復存

在，所以設計可以選擇低輸入電容切換開關，例如 ADG1209。這樣，不穩定性和交流 CMRR 降低得以避免。

與之前的設計一樣，增益精度和漂移將由電阻決定。可以選擇具有適當容差和漂移，符合應用設計要求的分立電阻。同樣的，使用電阻網路可以實現更高的精度、更好的容差和溫度跟蹤，不過成本會增加。

三運放儀錶放大器的第二級負責抑制共模電壓。此級建議使用整合電阻網路的差動放大器，以確保 CMRR 最佳。對於單端輸出和相對低頻寬的應用，AD8276 是一個不錯的選擇。如果需要差分輸出和更高頻寬，可以使用 AD8476。第二級的另一個選擇是使用 LT5400 作為標準放大器周圍的增益設置電阻。這可能會佔用更多的電路板空間，但另一方面又為放大器的選擇提供了更大的靈活性，用戶可以圍繞特定設計要求進行更多設計。

應注意的是，分立式 PGIA 的佈局需要小心。電路板佈局的任何不平衡都會導致 CMRR 隨頻率而

降低。

下表總結了每種方法的優缺點：

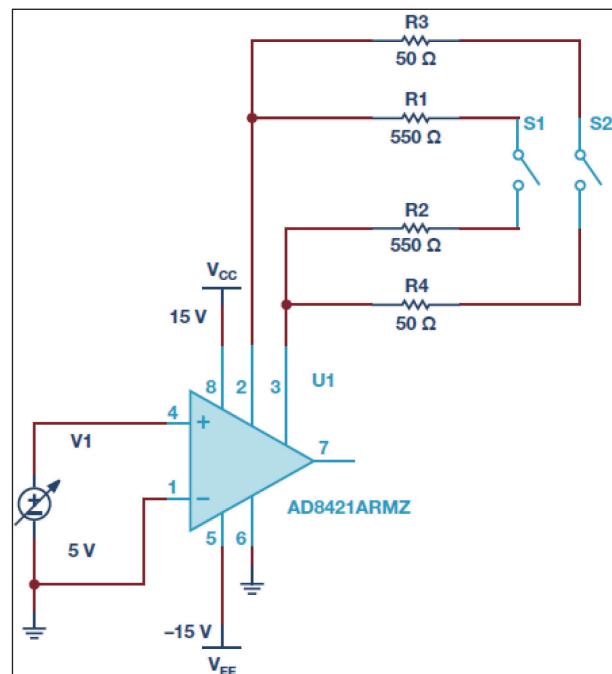

## 分立式 PGIA 設計示例

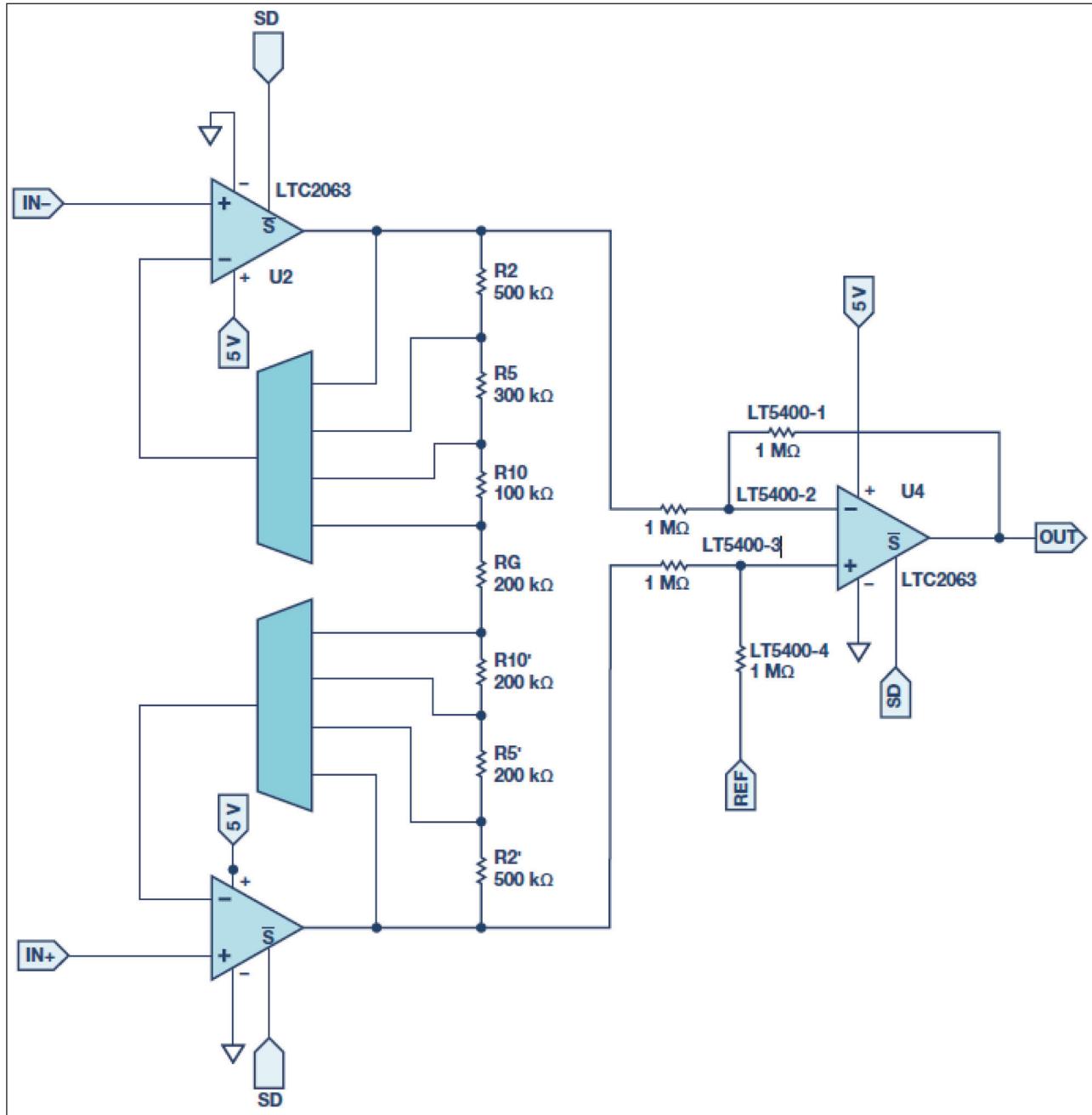

圖 9 約出了一個針對特定設計規格而構建的分立 PGIA 示例。在這種設計中，所構建的 PGIA 應具有非常低的功耗。輸入緩衝器選擇 LTC2063，其電源電流很低，最大值為  $2\mu\text{A}$ 。切換開關元件選擇 ADG659，其電源電流很低，最大值為  $1\mu\text{A}$ ，輸入電容也很低。

選擇電路中的被動元件時也需要注意，須滿足低功耗要求。被動元件選擇不當會導致電流消耗增大，抵消使用低功耗元件的作用。在這種情況下，增益電阻需要足夠大，以免消耗太多電流。所選電阻值(用來提供 1、2、5 和 10 的增益)如圖 9 所示。

對於第二級差動放大器而言，LTC2063 與 LT5400 四通道匹配電阻網路(1 M $\Omega$  選項)搭配使用可確保電流消耗最低，並且電阻的精確匹配也可保護 CMRR 性能。

表 4：可編程設計增益儀錶放大器不同實現方法的比較

| 方法                                                               | 優點                                                                                                                                                   | 弱點                                                                                                                                     |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 整合 PGIA                                                          | <ul style="list-style-type: none"> <li>■ 設計工作最少</li> <li>■ 對於良好的交流和直流性能進行優化</li> <li>■ 保證 CMRR 性能</li> <li>■ 所需電路板空間較小</li> <li>■ 單元件解決方案</li> </ul> | <ul style="list-style-type: none"> <li>■ 選擇有限</li> </ul>                                                                               |

| Balanced Configuration<br>(In-Amp with Switch)<br>平衡配置(儀錶放大器和開關) | <ul style="list-style-type: none"> <li>■ 與分立三運放儀錶放大器相比，設計工作量最小</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>■ 如果設計不當，容易產生不穩定性</li> <li>■ 與分立三運放儀錶放大器相比，儀錶放大器的選擇較少</li> <li>■ 切換開關的導通電阻會導致增益誤差和漂移</li> </ul> |

| Indirect Current Feedback with Mux<br>間接電流回饋，使用多工器               | <ul style="list-style-type: none"> <li>■ 與分立三運放儀錶放大器相比，設計工作量最小</li> <li>■ 易於配置</li> <li>■ 開關的導通電阻不會導致增益誤差和漂移</li> </ul>                              | <ul style="list-style-type: none"> <li>■ 輸入範圍有限</li> <li>■ 靈活性較低，可用的 ICF 儀錶放大器數量較少</li> </ul>                                          |

| ADA4077 and Clamping OVP<br>ADA4077 和箇位 OVP                      | <ul style="list-style-type: none"> <li>■ 最靈活，因為相較於儀錶放大器，運算放大器的選擇更多</li> <li>■ 高度可配置 - 可結合過濾、差分輸出等</li> <li>■ 切換開關的導通電阻不會導致增益誤差和漂移</li> </ul>         | <ul style="list-style-type: none"> <li>■ 需要較多元件</li> <li>■ 需要較多電路板空間</li> <li>■ 實現關鍵規格所需的設計工作量要多很多</li> </ul>                          |

圖 9: 低功耗 PGIA 設計

該電路採用 5 V 電源供電，並使用不同的共模電壓、差分輸入電壓和增益進行了評估。在參考電壓和輸入保持在中間電源電壓的最佳條件下，電路僅消耗 4.8 $\mu$ A 的電流。

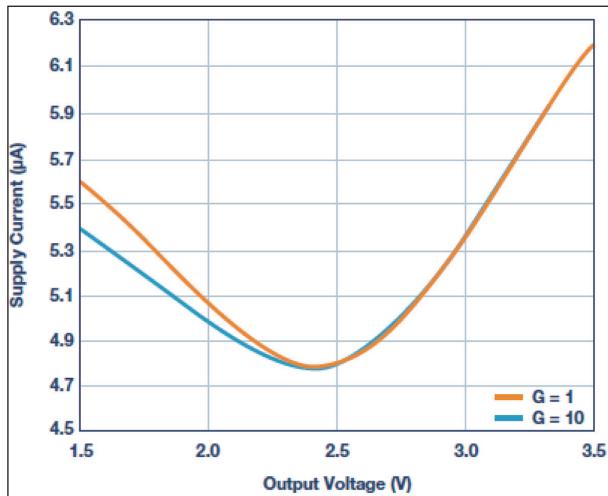

差分輸入變化時預計電流會有一定的增加，原因是電流會流過增益電阻，電流值等於  $|V_{OUT} - V_{REF}|/(2 M\Omega || 1 M\Omega)$ 。圖 10 顯示了不同增益下消

耗的電流。由於增益原因，資料是相對於輸出端測量。

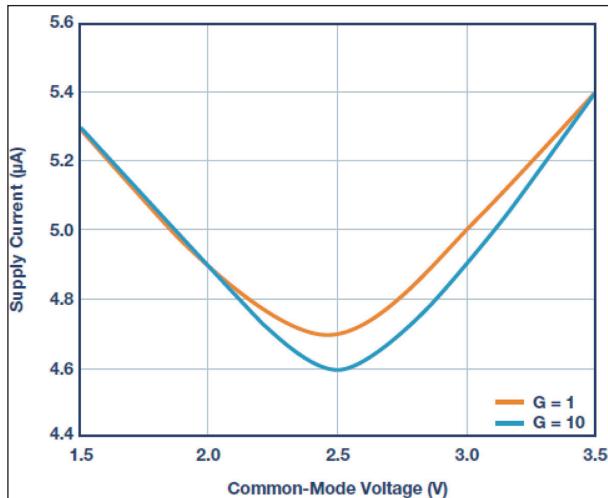

將不同共模電壓施加至輸入時，電流預計也會增加。施加的電壓將導致電流流過第二級中的電阻，引起額外的電流消耗，其值等於  $|V_{CM} - V_{REF}|/1 M\Omega$ 。LT5400 選擇 1 MΩ 電阻就是專門為了儘量減小這種電流。圖 11 顯示了共模電壓對不同增益下的

圖 10：電源電流與輸出電壓的關係

圖 11：電源電流與共模電壓的關係

電流消耗的影響：

另外還測量了關斷模式下電路的靜態電流。當所有元件關斷時，電路僅消耗 180 nA 的電流。這不會有變化，即使共模電壓、參考電壓和差分輸入等變數發生變化，只要它們都保持在電源範圍內即可。所有元件都具有關斷的選項，以防需要進一步節省功耗以及使用者希望斷電時能再重啓。在可攜式電池供電的應用中，該電路非常有用；若非如此，利用整合 PGIA 是無法實現關鍵規格的。

## 結論

可編程設計增益儀錶放大器是資料擷取領域的關鍵元件，即使配合不同靈敏度的感測器使用，也能實現良好的 SNR 性能。使用整合 PGIA 可縮短設計階段，提高前端的整體直流和交流性能。如果有符合要求的整合式 PGIA，設計中一般應優先使用這樣的元件。但是，當系統要求的規格無法透過現有整合元件實現時，則可設計一個分立式 PGIA。透過遵循正確的設計建議，即使採用分立式方法也可以實現最佳設計，並且可以評估各種建置方法，以確定具體應用的最佳配置。

作者感謝 Scott Hunt 和 Paul Blanchard 對本文的技術貢獻。

## 全球線上黑客松活動 MolHack 2019 起跑

全球 AI 人工智慧百強公司 英科智能有限公司 (Insilco Medicine, Inc.) 為搶吸臺灣具備深度學習和生物化學知識的人才，將於 2 月 25 日至 3 月 31 日舉辦「MolHack 2019」活動，競賽主題為「AI 學習小分子藥物結構分析」，預計將吸引來自全球傑出的深度學習和生物化學團隊報名參加。台灣區排名前 3 名之參賽者除了可獲得 Macbook Pro 15 吋及 NVIDIA GPU 獎品外，也將有機會成為英科智能研發團隊的一員。

傳統製藥往往需要耗時數十年才完成新藥開發，而在藥物研發中，最重要的能力是設計出新穎且具備特定性質、符合藥物學專家認可的分子結構。而這些特性必須能用如 Molecular ACCess System structural keys( 簡稱 MACCS ) 等型態的 fingerprints 編碼來表示。本次競賽將以基於 MACCS 分子特性生成之小分子結構作為深度學習挑戰內容，而要找出這些分子結構是可以透過設計、訓練以 fingerprints 作為生成條件的深度神經網路模型來達成。我們將這種演算方式稱之為條件式深度學習生成模型，藉由設計出符合 MACCS fingerprints 格式，產生新穎且獨特的分子結構。因此期待參賽者能在競中激盪出精彩的火花。

「英科智能 MolHack II 2019 線上黑客松」活動報名網址：<http://molhack.com/>