# Ka 頻段需要更多頻寬？ 這裡有三個選項

■作者：Brad Hall /

ADI 公司航空航天和防務部門射頻系統應用工程師

## 引言

隨著全球連接需求的成長，許多衛星通訊(satcom)系統日益採用 Ka 頻段，對資料速率的要求也水漲船高。目前，高性能訊號鏈已經能支援數千兆暫態頻寬，一個系統中，可能有成百上千個收發器，而超高輸送量資料速率已經成為現實。

此外，許多系統已經開始從機械定位型靜態拋物線天線轉向主動相控陣天線。在增強型技術和更高整合度的推動下，元件間隔得以大幅減小，並已能滿足 Ka 頻段的需求。透過在沿干擾訊號方向的天線方向圖中形成零位，相控陣技術還能提高降干擾性能。

下面將簡要描述現有收發器架構中存在的一些折衷選項，以及不同類型的架構在不同類型的系統中的適用性。本分析將分解介紹衛星系統的部分關鍵技術規格，以及如何從這些系統級技術規格獲得收發器訊號鏈層各元件的規格。

## 從系統級分析得到技術規格

從宏觀層面來看，衛星通訊系統需要維持一定的載波雜訊比(CNR, carrier-to-noise ratio)，此為鏈路預算計算的結果。維持該 CNR 可以保證一定的誤碼率(BER)。需要的 CNR 取決於多種因素，如糾錯、資訊編碼、頻寬和調變類型。確定 CNR 要求之後，就可以依據高層系統要求得到各個接收器與發射器的技術規格。一般而言，首先得到的是收發器的增益 - 系統雜訊溫度(G/T)品質因數和發射器的有效

全向輻射功率(EIRP)。

對於接收器，要從 G/T 得到低層接收器訊號鏈規格，系統設計者需要知道天線增益和系統雜訊溫度，該值為天線指向與接收器雜訊溫度的函數，如等式 1 所示。基於此，可以用等式 2 得到接收器溫度。

$$\frac{G}{T}(\text{dB}) = G_{ant}(\text{dB}) - 10\log(T_{sys}) \quad (1)$$

$$T_{sys} = T_{ant} + T_{RX} \quad (2)$$

然後可以用等式 3 計算接收器訊號鏈的雜訊指數：

$$NF_{RX}(\text{dB}) = 10\log\left(\frac{T_{RX}(\text{K})}{290\text{K}} + 1\right) \quad (3)$$

獲知接收器雜訊指數以後，可以進行級聯分析，確保訊號鏈是否符合這些必要技術規格的要求，以及是否需要進行調整。

對於接收器，首先基於接收器的距離(地到衛星或衛星到地的距離)和接收器靈敏度確定需要的 EIRP。獲知 EIRP 要求之後，需要在發射訊號鏈的輸出功率與天線增益之間做出折衷。對於高增益天線，可以減小發射器的功耗和尺寸，但其代價是增加天線尺寸。EIRP 是透過等式 4 來加以計算。

$$EIRP(\text{dBW}) = P_{TX}(\text{dBW}) + G_{ant}(\text{dB}) \quad (4)$$

只要謹慎選擇訊號鏈所用元件，就能維持輸出

功率不變，並且不會導致其他重要參數下降，如在其他系統中，則可能會導致干擾的輸出雜訊譜密度和頻外射頻能量。

發射器和接收器的其他重要技術規格包括：

- 暫態頻寬：訊號鏈在任意時間點可以處理的頻譜量

- 功率處理：訊號鏈在不導致性能下降的條件下要處理的最大訊號量

- 通道間的相位相干性：針對新興的波束成形系統，旨在確保通道間相位的可預測性，以便簡化波束成形訊號處理和校準

- 雜散性能：確保接收器和發射器不會在無用頻率下產生射頻能量，以免影響該系統或其他系統的性能

在訊號鏈的設計過程中，務必記住這些和其他技術規格，以便設計出能滿足任何給定應用需求的高性能系統，無論是寬頻多載波聚合集線器或是單個窄頻掌上型衛星通訊終端。

## 一般架構比較

確定高層技術規格以後，即可決定採用哪種訊號鏈架構。前面列出過並且可能對架構產生重大影響的一個關鍵技術規格是暫態頻寬。該規格會影響接收器的類比數位轉換器 (ADC) 和發射器的數位類

比轉換器 (DAC)。為了實現高暫態頻寬，必須以更高的速率對數位化儀採樣，結果一般會推高整個訊號鏈的功耗，但是，如果從單位功耗 (W/GHz) 來看，則會降低功耗。

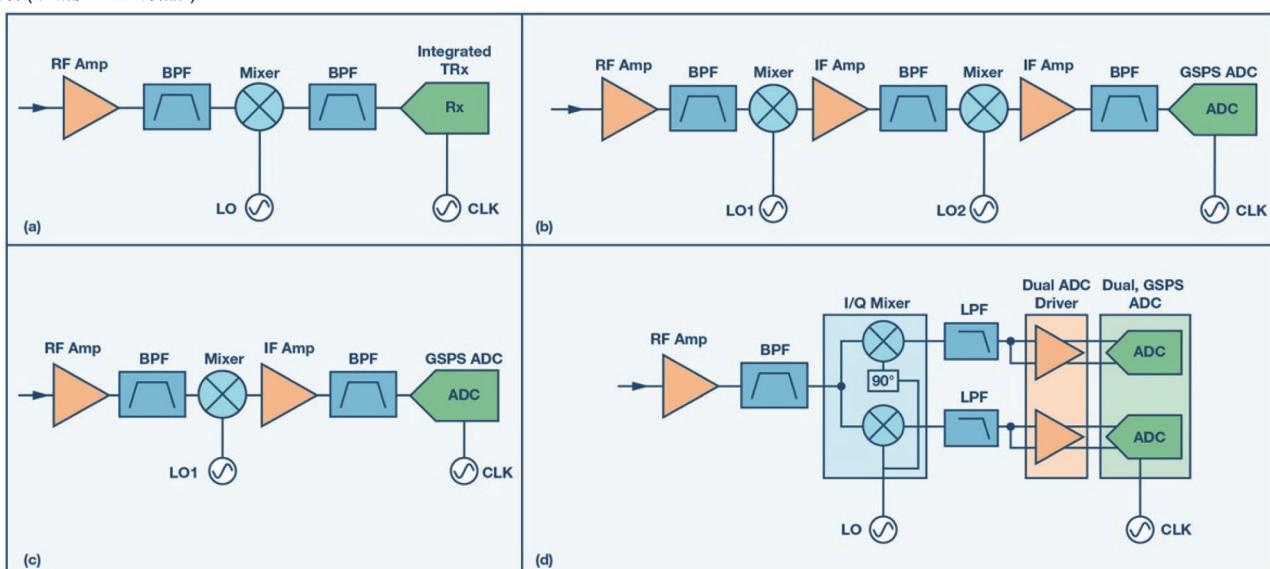

對於頻寬不足 100 MHz 的系統，許多情況下最好採用類似於圖 1a 的基礎架構。該架構將標準下變頻級與整合式直接變頻收發器晶片結合起來。整合的收發器可實現超高的整合度，從而大幅減小尺寸和功耗。

為了達到 1.5 GHz 的頻寬，可以將經典的雙變頻超外差架構與最先進的 ADC 技術結合起來；如圖 1b 所示。這是一種成熟的高性能架構，整合的變頻級用於濾除無用的雜散訊號。根據收到的頻段，用一個下變頻級將接收的訊號轉換成中頻 (IF)，然後用另一個下變頻級將最終的中頻訊號轉換成 ADC 可以數位化的低頻訊號。最終中頻越低，ADC 性能越高，但其代價是會增加濾波要求。一般而言，受元件數量增加影響，該架構是本文所提四個選項中尺寸最大、功耗最高的架構。

與其類似的選項如圖 1c 所示，圖中是一個單次變頻級，用於將訊號轉換成高中頻，再由 GSPS ADC 採樣。該架構利用了 ADC 能數位化的更多射頻帶寬，幾乎不會導致性能下降。市面上最新的

圖 1：架構比較，(a) 高中頻 (整合 TRx)，(b) 雙變頻超外差架構 (帶 GSPS ADC)，(c) 單變頻超外差架構 (具備 GSPS ADC)，(d) 直接變頻 (具備 I/Q 混頻器)。

GSPS ADC 可以對最高 9 GHz 的射頻頻率直接採樣。在本選項中，中頻中心在 4 GHz 和 5 GHz 之間，可在訊號鏈要求與 ADC 要求之間達到最佳平衡。

最後一個選項如圖 1d 所示。該架構的暫態頻寬增幅甚至更大，但其代價是非常複雜，並且有可能導致性能下滑。這是一種直接變頻架構，採用一個被動 I/Q 混頻器，後者可以在基頻上輸出兩個相互偏移  $90^\circ$  的中頻。然後用一個雙通道 GSPS ADC 對各 I 和 Q 腳進行數位化。在這種情況下，可以獲得最高達 3 GHz 的暫態頻寬。該選項的主要挑戰是在誤差透過混頻器、低通濾波器和 ADC 驅動器傳播時，要在 I 和 Q 路徑之間維持正交平衡。根據具體的 CNR 要求，這種折衷可能是可以接受的。

以上從宏觀層面簡要介紹了這些接收器架構的工作原理。清單並未羅列出所有的情況，也可以將各種選項綜合起來使用。雖然比較未涉及發射訊號鏈，但圖 1 中的每個選項都有一個對應的發射訊號鏈，其折衷情況也相似。

## Ka 頻段衛星通訊接收器示例

以上討論了各種架構的優點和不足，接下來，

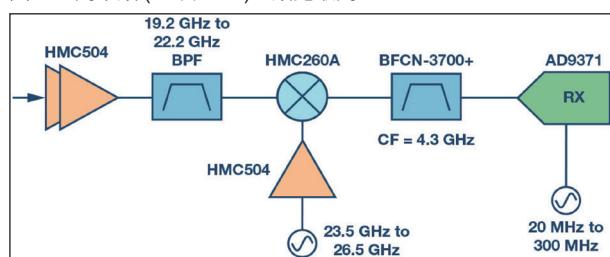

圖 2：高中頻 (整合 TRx)，頻寬最高 100 MHz。

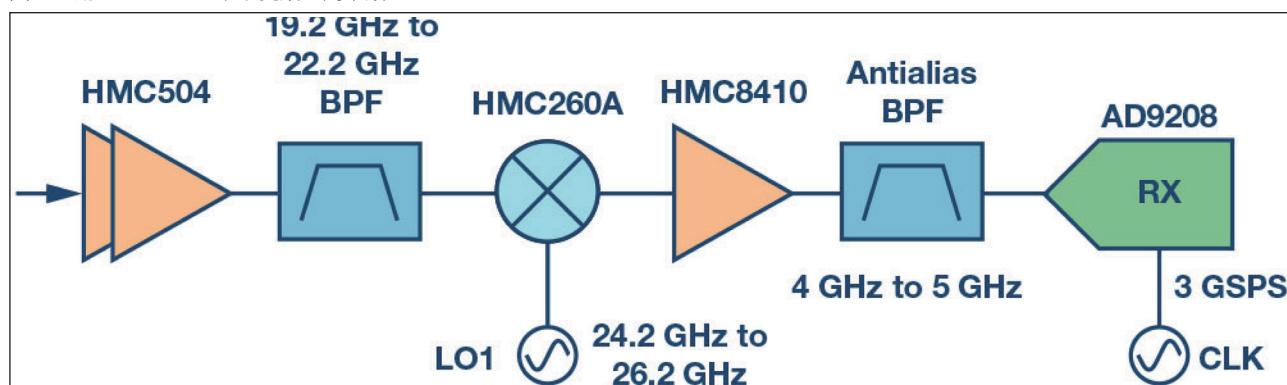

圖 3：用 GSPS ADC 單下變頻至高中頻。

我們可以將這些知識運用到真實的訊號鏈示例當中。目前，許多衛星通訊系統都運行在 Ka 頻段，以減小天線尺寸、提高資料速率。在高輸送量衛星系統中，這一點尤其重要。以下是採用不同架構的示例，我們將對其進行更加詳細的比較。

對於要求 100 MHz 以下暫態頻寬的系統，如甚小孔徑終端 (VSAT)，可以採用整合式收發器晶片的高中頻架構 (AD9371)，如圖 2 所示。該設計可以實現低雜訊指數，並且由於具有高整合度，所以其設計尺寸最小。現將其性能總結於表 1 中。

如果作為衛星通訊系統多個使用者的集線器，有些系統可能要同時處理多個載波訊號。這種情況下，每個接收器的頻寬或頻寬 / 功率就變得非常重要。圖 3 所示訊號鏈採用一款高速 ADC，即 AD9208，這是最近發表的一款高採樣速率 ADC，可以數位化最高 1.5 GHz 的暫態頻寬。在本例中，為了實現 1 GHz 的暫態頻寬，中頻被置於 4.5 GHz。這裡可實現的頻寬取決於位於 ADC 之前的抗混疊濾波器的濾波要求，但一般局限於奈奎斯特區的 ~75% ( 採樣速率的一半 )。

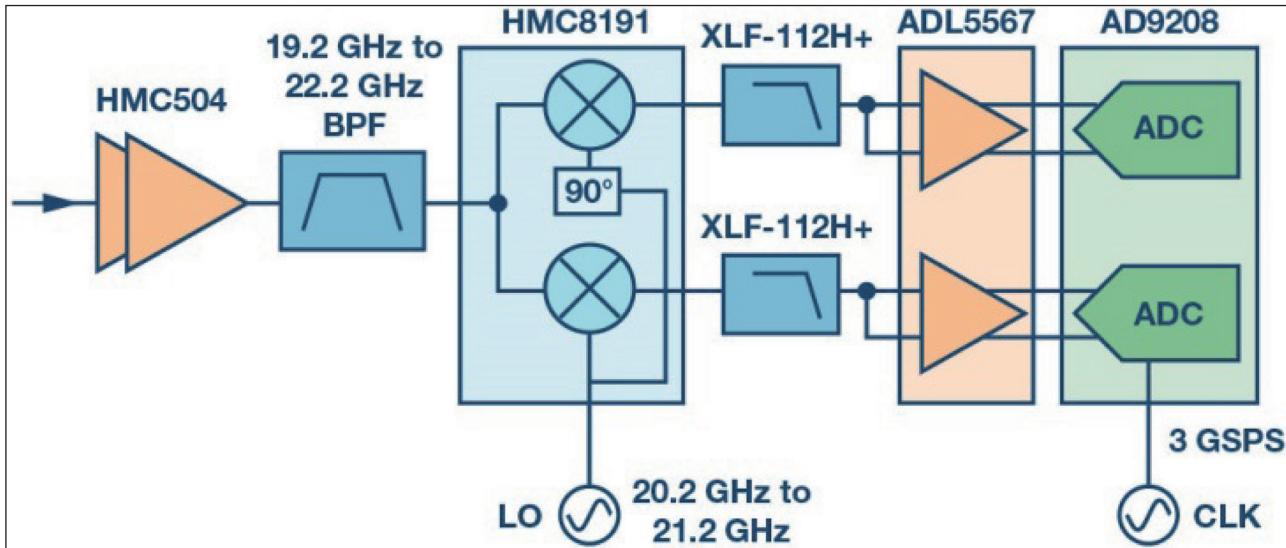

在要求最高暫態頻寬並且可能以 CNR 形式放棄性能的系統中，可以採用圖 4 所示訊號鏈。該訊號鏈採用一個 I/Q 混頻器，即 HMC8191，其鏡像抑制性能為  $\sim 25$  dBc。在這種情況下，鏡像抑制性能受到 I 和 Q 輸出通道間幅度和相位平衡的限制。在不採用更先進的正交誤差校正 (QEC) 技術的情況下，這是該訊號鏈的限制因素。該訊號鏈的性能總結見表 1。需要注意的是，NF 和 IP3 性能與其他選項類似，但功率 /GHz 指標則為三者中最低，並且

圖 4：用 I/Q 混頻器和 GSPS ADC 實現直接變頻。

從任意時間可以利用的頻寬量來看，其尺寸也屬最佳狀態。

這裡所提供的三種接收選項如下表所示，但需要注意的是，該表並未列出全部可能選項。這裡的總結旨在展示各種訊號鏈選項之間的差異。在任何給定系統中，最終的最優訊號鏈既可能是三者之一，也可能是任意選項的綜合運用。

另外，雖然表中只顯示了接收器端的情況，但發射器訊號鏈也存在類似的折衷情況。一般而言，隨著系統從超外差類架構轉向直接變頻類架構，需

要在頻寬與性能之間進行折衷。

## 資料介面

在資料被 ADC 或收發器數位化以後，必須透過數位介面交給系統處理。這裡提到的所有數位化儀都採用了高速 JESD204b 標準，從資料轉換器接收訊號，然後把訊號打包成幀，再透過少量佈線進行傳輸。晶片的資料速率因系統要求而異，但這裡提到的所有元件都有用於汲取和頻率轉換的數位功能，能夠適應不同資料速率，以滿足不同系統要求。該規格

在 JESD204b 通道上最高支援 12.5 GSPS 的速率，傳輸大量資料的高頻寬系統即充分利用了這一點。有關這些介面的詳細描述請參閱 AD9208 和 AD9371 的資料手冊。另外，FPGA 的選擇必須考慮該介面。供應商（如 Xilinx 和 Altera）提供的許多 FPGA 和其他 FPGA 目前已經在其元件中整合該標準，為與這些資料轉換器的整合提供了便利條件。

## 結論

本文詳細介紹了各種折衷情

表 1：Ka 頻段接收器詳情比較

|                         | 高中頻<br>(具備整合 TRx) | 高中頻<br>(具備 GSPS ADC) | 直接 變頻       |

|-------------------------|-------------------|----------------------|-------------|

| Digitizer               | AD9371            | AD9208               | AD9208(雙通道) |

| 暫態頻寬                    | 100 MHz           | 1 GHz                | 2 GHz       |

| NF(dB)                  | 2.5               | 2.3                  | 2.3         |

| IIP3(dBm)               | -19               | -20                  | -20         |

| 最大 Pin(dBm)             | -38               | -40                  | -41         |

| 其他雜散<br>(HD2、HD3、MxN)   | 65 dB             | 73 dB                | 45 dB       |

| 鏡像抑制 (dBc)              | 75                | 80                   | 25          |

| 濾波難度                    | 低                 | 中                    | 低           |

| 功率 (W)                  | 2.9               | 4.1                  | 6.1 (W/GHz) |

| 功率 /GHz (W/GHz)         | 29                | 4.1                  | 3.05        |

| 封裝尺寸 (mm <sup>2</sup> ) | 300               | 510                  | 580         |

況，並就 Ka 頻段衛星通訊系統適用的訊號鏈列舉了一些例子。同時也介紹幾種架構選項，包括利用整合式收發器 AD9371 的高中頻單次變頻選項，用 GSPS ADC 取代整合式收發器以提高暫態頻寬的類似架構，以及可以提高頻寬但會降低鏡像抑制性能的直接變頻架構。所介紹的訊號鏈雖然可以直接使用，但建議以其為基礎進行設計。根據具體的系統級應用，會出現不同的要求，隨著設計工作的推進，訊號鏈的選擇也將會越來越清晰。

## 參考文獻

- Bosworth, Duncan and Wyatt Taylor. "Bandwidth Demands Place New Strains on Satellite Communications Design." Analog Devices, Inc., 2016.

- Bosworth, Duncan and Wyatt Taylor. "Bandwidth Demands Place New Strains on Satellite Communications Design( 頻寬需求為衛星通訊設計帶來新的壓力 )。" ADI 公司, 2016 年。

- Delos, Peter. "A Review of Wideband Receiver Architectures." Analog Devices, Inc., 2017.

- Delos, Peter. "A Review of Wideband Receiver Architectures( 寬頻接收機架構方案綜述 )。" ADI 公司, 2017 年。

- Hall, Brad and Wyatt Taylor. "Small Form Factor SATCOM Solutions." Analog Devices, Inc., 2017.

- Hall, Brad and Wyatt Taylor. "Small Form Factor SATCOM Solutions( 小尺寸衛星通訊解決方案 )。" ADI 公司, 2017 年。

- Bousquet, Michel and Gerard Maral. Satellite Communications Systems—5th Edition. West Sussex: John Wiley & Sons, Inc., 2009.

- Bousquet, Michel and Gerard Maral. Satellite Communications Systems—5th Edition( 衛星通訊系統—第 5 版 )。West Sussex: John Wiley & Sons, Inc., 2009 年。

## 線上支援社區

瀏覽ADI線上支援社區，與ADI技術專家互動。

提出您的棘手設計問題、流覽常見問題解答，或參與討論。請瀏覽 [ez.analog.com](http://ez.analog.com)

## 經濟部工業局匯集專家資源 打造 IoT 產業生態鏈

經濟部工業局為帶動國內晶片設計與半導體產業於創新物聯領域之發展，委託財團法人資訊工業策進會規劃「北部物聯網智造基地」，並邀集產學專家籌組「智造服務團」，企盼藉此串接產學資源，打造由內而外 MiT 之創新物聯產品。

「北部物聯網智造基地暨智造服務團」於今年正式啓動，匯集產品設計與小量智造領域業者，成立「智造服務團」，導入專家資源促進創新物聯產品生成，並透過「台灣智慧玩具聯盟」建構關鍵領域產業生態鏈。

此次成立大會，邀請到物聯科技、品牌設計、跨域整合、國際通路、創新培育等跨界產業夥伴蒞臨，包括：松翰科技、愛文西門、台創中心、塔塔加品牌設計、玩具研發中心、智高實業、政治大學、文筆網路科技、愛魅客等，將在現場分享發展創新物聯產品各層面之關鍵要點，期以產業經驗加速智造服務之發展。

經濟部工業局期盼透過創新物聯服務，導入國內晶片設計解決方案，進而帶動半導體產業發展，提供創意物聯網產品鏈結場域試煉；「北部物聯網智造基地」將結合臺北數位產業園區 (digiBlock Taipei)，預計成為北部地區創新加值樞紐，協助新創團隊加速實踐商品化及對接市場，發揮資源整合最大總效益。