# 接收器 IC 混合式混頻器 頻率合成器和 IF 放大器

■作者：Tom Bosia, Russell Martin, Marc Goldfarb,

Dragoslav Culum, Ben Walker, Ed Balboni/ ADI 公司

無線基地台曾經封裝在採用氣候控制技術的大型空間中，但現在卻可以安裝在任何地方。隨著無線網路服務供應商試圖實現全域訊號覆蓋，基地台元件供應商也正面臨著壓力，他們需要在更小的封裝中提供更多的功能。

來自 ADI 公司的一對積體電路 (IC) 提供了一種解決方案，其重新界定了接收器前端混頻器的意義。實際上，該 IC 在混頻器 IC 內部整合了曾經附加於接收器內混頻器的許多元件，例如，本地振盪器 (LO) 和中頻 (IF) 放大器。利用這些 IC，可以大幅減少蜂巢式基地台的大小，同時還能帶來軟體定義無線電 (SDR) 的彈性，而能因應多種不同的無線標準。

這裡所提到的 IC 型號，分別為 ADRF6612 和 ADRF6614，根據設計二者支援的 RF 範圍為 700

MHz 至 3000 MHz，LO 範圍為 200 MHz 至 2700 MHz，IF 範圍為 40 MHz 至 500 MHz。它們支援低端或高端 LO 注入，包括一個板載鎖相環 (PLL) 和多個低雜訊電壓控制振盪器 (VCO)，全部封裝在 7 mm × 7 mm 48 接腳的 LFCSP 外殼中。超高的整合度和元件密度，加上多樣性和可編程能力，可以支援多種不同的無線標準，完全滿足現代微蜂巢式的小量生產需求。

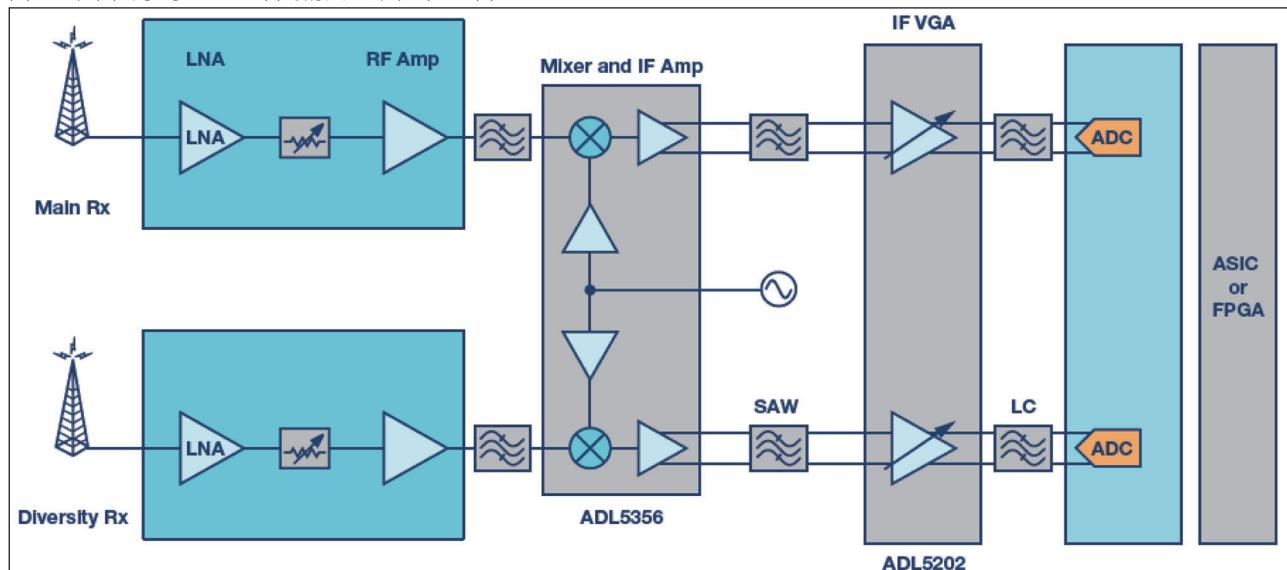

為了能更良好地理解這些高度整合的混頻器 IC 在節省空間方面的優勢，不妨回憶一下 2010 年左右時的蜂巢式基地台的前端，如圖 1 所示。雙混頻器架構的頻寬範圍約為 1 Ghz，需要多個元件來處理當時的蜂巢頻率範圍，即 800 MHz 至 1900 MHz。頻率合成由一個獨立的 PLL 和窄頻 VCO 模組提供，

圖 1：框圖所示為 2010 左右時的典型蜂巢式基地台。

圖 2：通道複用方案要求在 GSM 無線系統中採用低相位雜訊的寬頻寬 VCO，避免因阻塞導致性能下降。

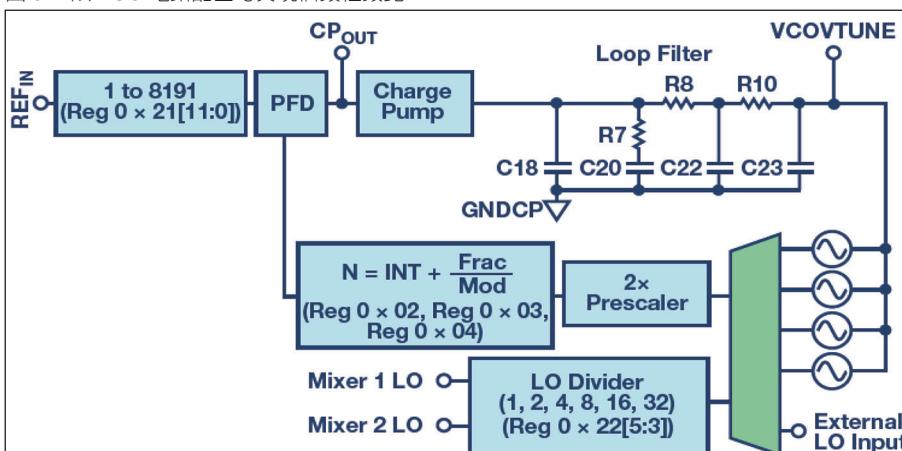

圖 3：該 VCO 電路配置可實現倍頻程頻寬。

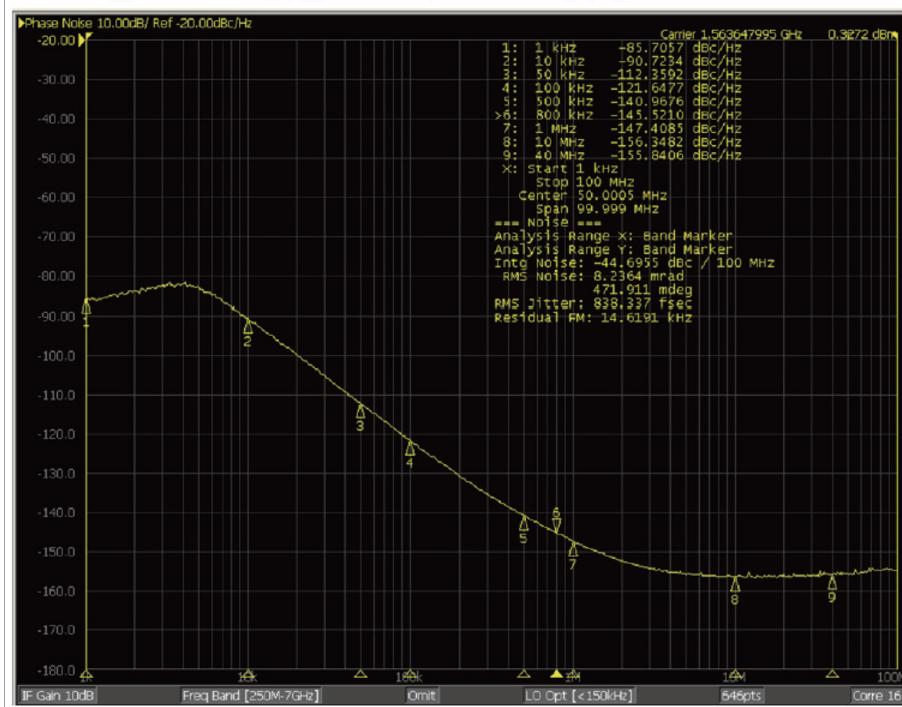

**ADRF6614 GSMVCO1 Phase Noise—Locked**

$f_{REF} = 153.6 \text{ MHz}$ ,  $f_{PFD} = 1.6 \text{ MHz}$ , Bleed = 32 (0  $\mu\text{A}$ ), CSSCALE = 8 mA

需要用一個特有的 PLL 回路濾波器才能實現最佳性能。每個目標頻段均採用專門的 VCO 模組，結果增加了基地台內所需要的電路板面積。

另外，這些分立式元件是透過低阻抗傳輸線路相互連接起來的，結果會增加訊號損失。而結果是，其需要很大的電流將 VCO 輸出驅動到足夠的位準，以便混頻器能在訊號阻塞條件下產生低相位雜訊和雜訊係數。

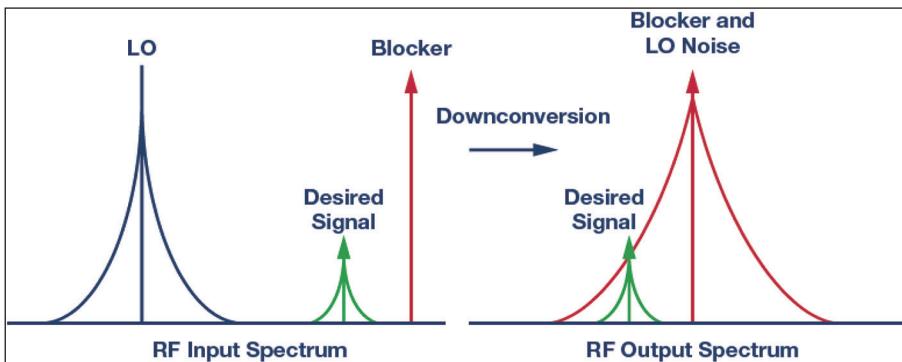

整合 VCO 的接收器 IC 並非新事物。但要實現多載波要求的寬頻寬和低相位雜訊，全球行動通訊系統 (MC-GSM) 無線網路一直是個挑戰。GSM 的通道複用方案要求接收 LO 具有極低的相位雜訊，尤其是在相間通道失調頻率為 800 kHz 的情況下，如圖 2 所示。如果這些相間通道的多餘相位雜訊與同樣處於 800 kHz 失調條件下的無用訊號相混合，則可能使相位雜訊轉換成 IF 輸出，從而降低系統的靈敏度。

低 VCO 相位雜訊通常是透過高品質因數 (高 Q) 諧振器和窄頻設計實現的。頻分也能降低雜訊。透過使 VCO 操作於接收器 LO 頻率的整數倍，隨後進行的分頻即可使相位雜訊降低一個 6 dB/ 倍頻程，如圖 3 所示。GSM 在 1800 MHz 至 1900 MHz 頻段內的相位雜訊要求極高，其嚴重程度大約相當於 800 MHz 至 900 MHz

頻段內相位雜訊的兩倍。

在低相位雜訊以外，現代基地台接收器設計必須支援無線通訊網路當前使用的多種調製方案。除 GSM 以外，其他調製方案包括寬頻碼分多址 (WCDMA) 和長期演進 (LTE) 系統。接收器設計通常包括若干不同的 VCO，其相位雜訊性能配置為中等水準，透過組合的方式滿足基地台倍頻程頻寬需求。

一旦將若干個 VCO 配置為在最高操作頻率下產生一個倍頻程頻寬，則可用二分頻實現較低的 LO 頻率。ADRF6612 接收器混頻器採用的就是這種方法，其中，VCO 基頻範圍為 2.7 Ghz 至 5.6 Ghz，透過從 1 至 32 分頻，兩級頻分實現 200 Ghz 至 2700 Mhz 的 LO 頻率。對於同時包括 MC-GSM 的應用，ADRF6614 接收器混頻器包括兩個額外的高性能 VCO 內核，用於提供 1800 Mhz 至 1900 MHz GSM 頻段所需要的 LO 頻率。

由於現代無線微蜂巢可能不具備氣候控制環境的優勢，所以這些接收器 IC 一類的元件可在較寬廣的極限溫度範圍內提供一致、可靠的性能。為了在較寬廣的工作溫度範圍內實現規定的性能，ADRF6612 和 ADRF6614 IC 中的 PLL 和 VCO 採用了多種校準技術。

對於低雜訊寬頻寬，每個 VCO 核心採用一個 8 位的容性數模轉換器 (CDAC)，後者可以為給定的 LO 頻率選擇正確的頻段 (128 選 1)。系統會仔細監控 VCO 諧振器幅度的任何變化，並用自動位準控制 (ALC) 系統調整幅度，以獲得最佳輸出幅度。每個 IC 都會在工作頻率被重新程式設計的時候執行校準序列。如此可以確保所選頻段將 VCO 調諧變容二極體的調諧電壓集中於最佳範圍內，使頻率合成器在所需工作溫度範圍保持鎖定。

每個 ADRF6612 和 ADRF6614 IC 中的四個 VCO 核心可以確保其工作範圍具有合適的重疊性，能適應不同的環境條件和器件製造容差。對於環境和製程差異，核心一般會以相同的方向移動頻率，因而內建了充足的重疊機制，使得頻率合成器能夠始終實現鎖定條件。

一旦確定校準方案，就可以無限地維持頻率，調諧電壓範圍支援需要的同步範圍。在時分雙工 (TDD) 系統中，基地台可能根據不同的時隙改變頻率，其工作時間可能按微秒計。在頻分雙工 (FDD) 系統中，可能需要多年鎖定單個頻率。

在 ADRF6612 和 ADRF6614 IC 系統工作期間，任何時候都不允許出現故障停機事故。因此，溫度變化和元件老化效應可透過 VCO 的變容調諧電壓範圍，以及頻率調諧靈敏度 ( $k_V$ ) 進行處理，溫度範圍有可能達 145°C。每個 IC 會根據需要持續監控元件溫度並調整 VCO 偏置。

ADRF6612 和 ADRF6614 IC 採用一種獨特的方法，可將由雜散訊號產物導致的接收器靈敏度下降問題達到最低。利用頻率合成器的整數模式和精巧迴路濾波器可使參考雜散產物低至 -100 dBc 以下。最小雜散訊號對調變方案至關重要，如 MC-GSM。對於 LTE 和其他調變方案，或者在需要精細的頻率階躍的情況下，頻率合成器可以操作於小數 N 分頻模式。參考路徑整合一個 13 位元分頻器，整數和小數路徑各自整合 16 位元分頻器，具有極大的彈性。

對於需要共置相位追蹤接收通道的應用中，如多輸入多輸出 (MIMO) 系統，可以透過菊鏈方式將 ADRF6612 和 ADRF6614 IC 級聯起來，以便允許其中一個單元作為主頻率合成器，分別透過其外部 LO 輸出和輸入埠為其他從機接收器供電。如此就可以最大限度地降低額外 LO 分配放大器及其相位雜訊相應增大的程度。

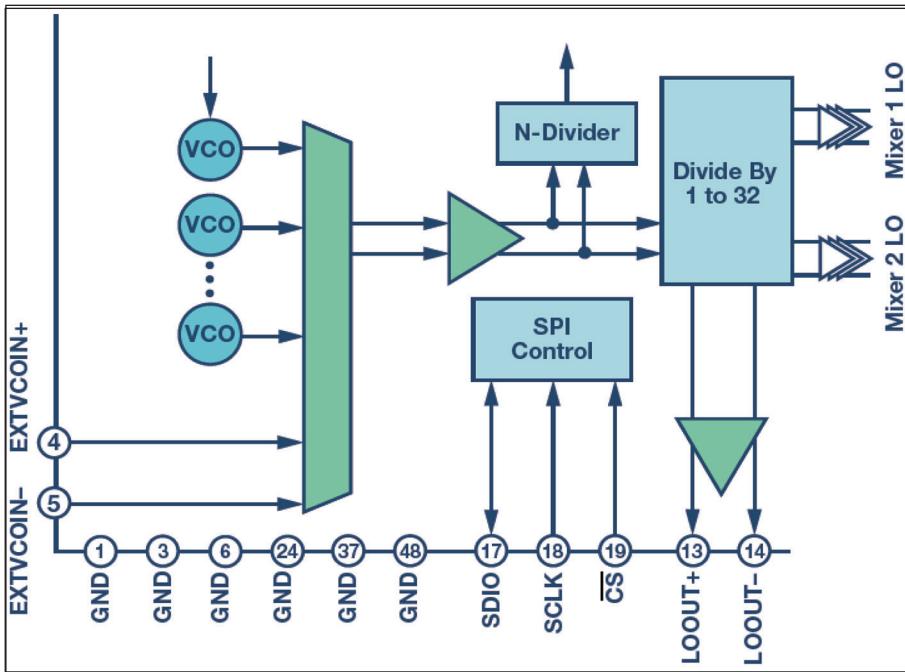

為了同時支援高端和低端 LO 注入，每個 IC 的 LO 鏈提供了彈性的訊號處理，如圖 4 所示。使用 1 至 32 的整數分頻比，即使是 700 Mhz 頻段和高 IF，也可實現低端注入。LO 級在從 200 Mhz 至 2700 Mhz 的整個 LO 範圍內，同時為被動混頻器核心提供一個方波驅動。<sup>1</sup>

現代無線基地台頻內訊號在頻率上接近低位準輸入訊號，因而蜂巢式接收器可以充當阻塞訊號。在這種情況下，在目標訊號之上，來自阻塞訊號附近 LO 放大器的相位雜訊被混頻進 IF 輸出頻段。如

圖 4：本 LO 訊號鏈用於支援無線基地台接收器。

此有時能大幅降低接收器的訊號雜訊比 (SNR)。

由於阻塞訊號可能較大(高功率),所以VCO相位雜訊必須極低,並且LO鏈不會在阻塞器失調條件下降低噪底。在這些超高的阻塞位準下,接收器雜訊係數會最終被阻塞訊號主導,並根據阻塞器功率水準的高低下降。

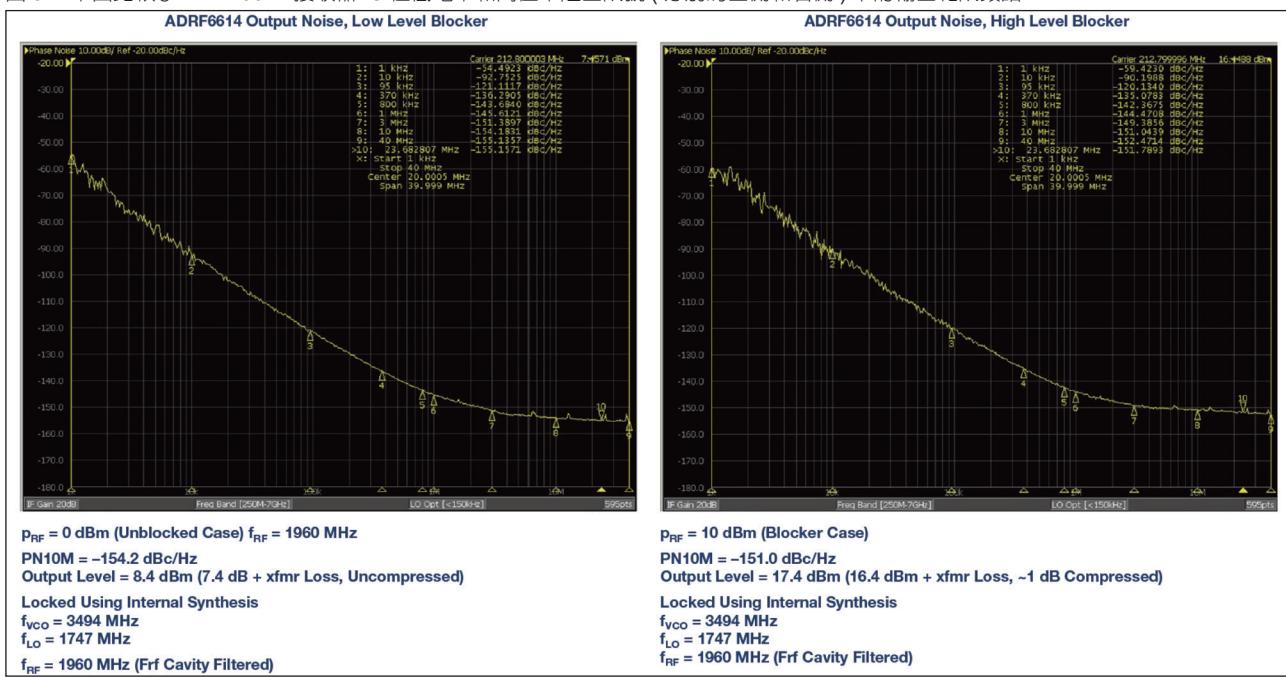

圖 5：本圖比較了 ADRF6614 接收器 IC 在低電平和高位準阻塞訊號（分別為左側和右側）下的輸出雜訊頻譜。

在分立式接收鏈方案中，可以在 LO 路徑上引入一些濾波機制，以在阻塞器失調條件下，最大限度地降低來自 VCO 和 LO 分配放大器的相位雜訊。然而，在整合式前端中則必須相當謹慎，避免 LO 鏈中的加性相位雜訊。

## ADRF6612 和 ADRF6614

IC 採用高增益 LO 鏈和硬限幅放大器以將 LO 鏈驅動至限幅。當每個級進入硬限幅時，在其他情況下，會增大相位雜訊的 LO 鏈小訊號增益將大幅下降，從而將阻塞條件下的雜訊係數下降問題減至最小。

來自阻塞訊號的雜訊折疊會降低接收器輸出雜訊頻譜性能，提高輸出底層雜訊，從而降低接收器雜訊係數。根據設計，ADRF6612 和 ADRF6614 接收器 IC 可在最大限度減小接收器雜訊係數降幅的條件下承受較大的阻塞訊號，如圖 5 所示。即使輸入阻塞位準為 10 dBm，在載波失調 10 MHz 條件下，

圖 6：本訊號鏈所示為典型無線基地台接收器中採用的元件。

接收器的雜訊係數也只會下降 3.2 dB，即使轉換增益在極端阻塞電平下縮減 1 dB，亦是如此。

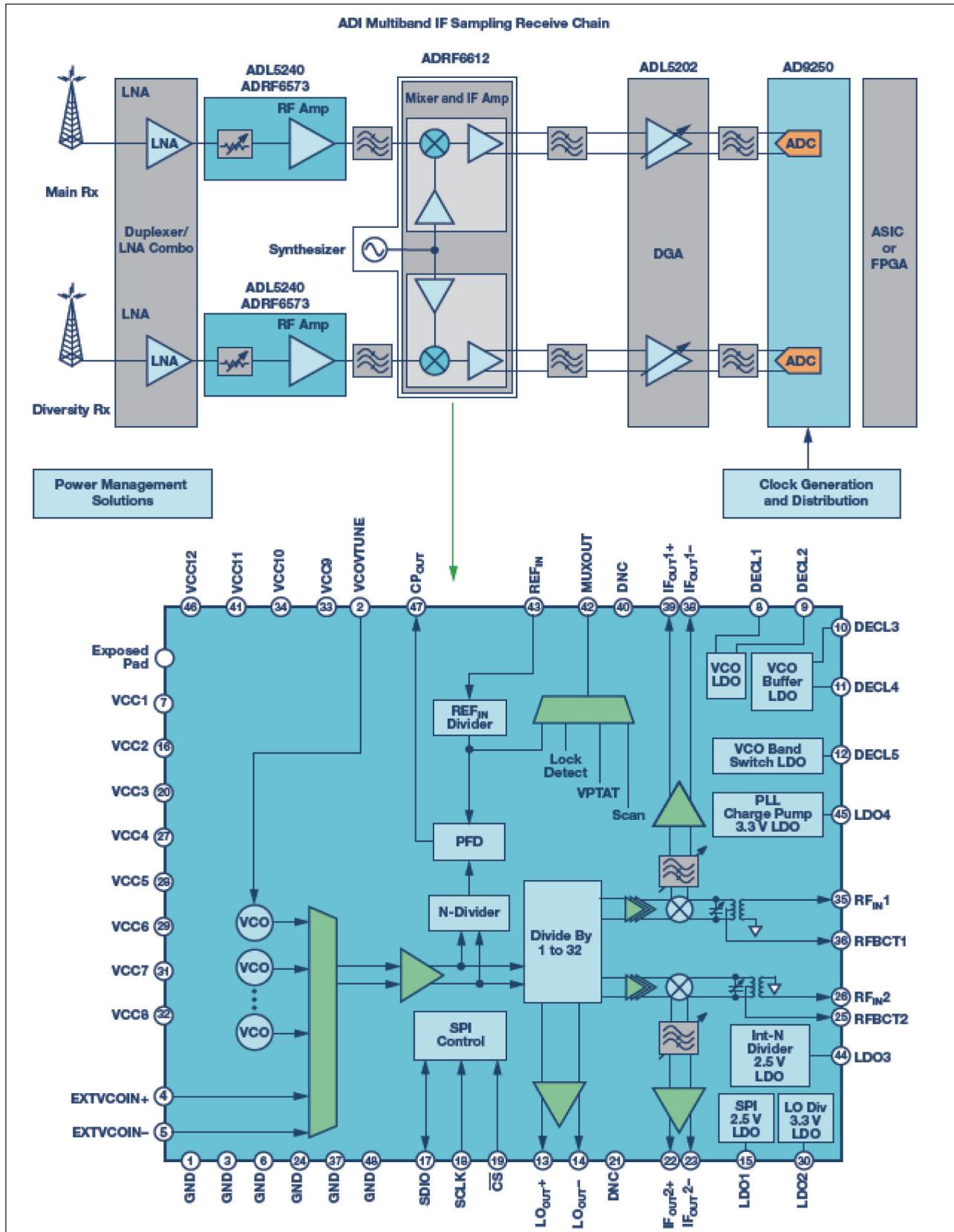

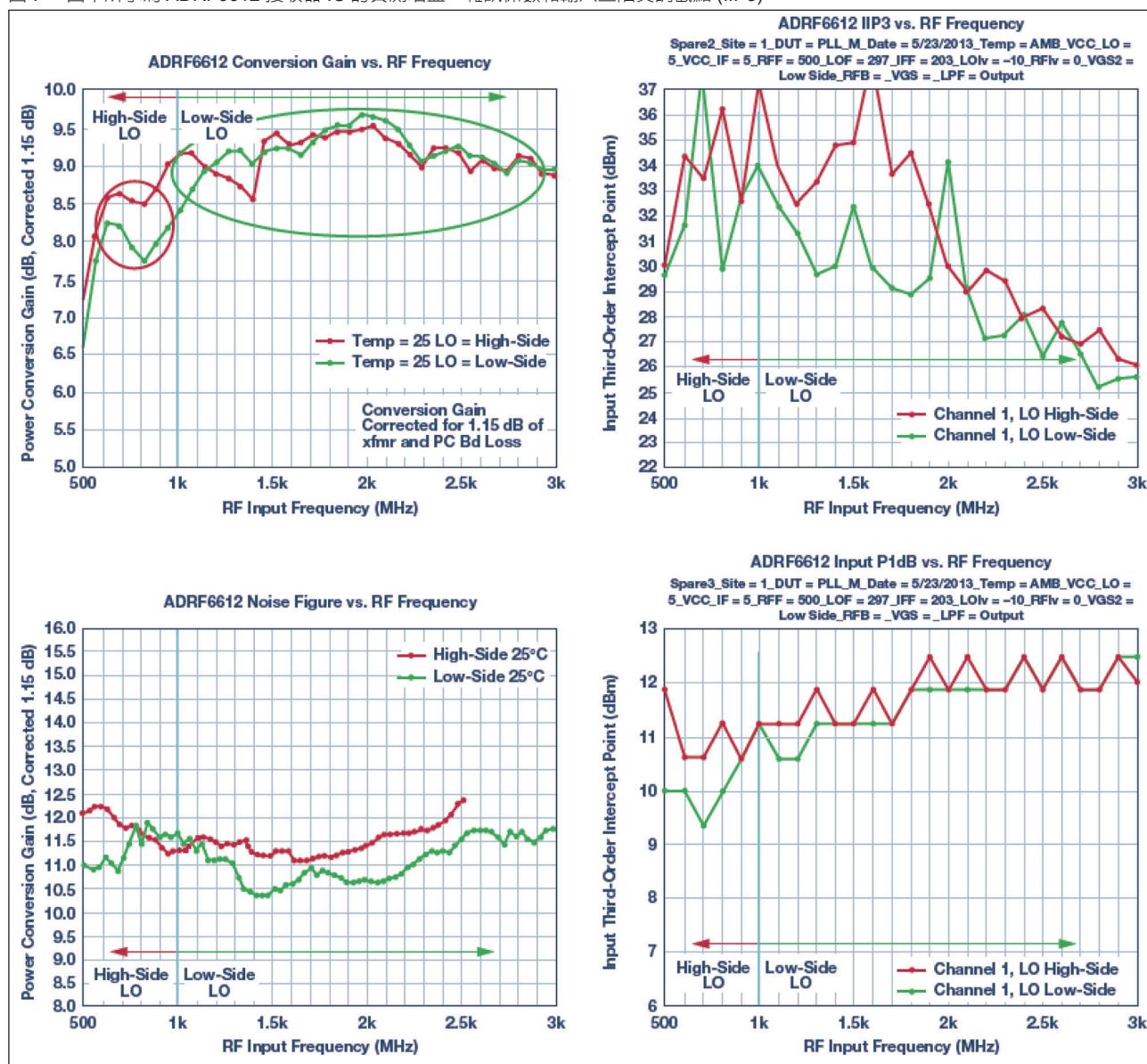

這些接收器 IC 具有超高的整合度，因而對現代無線基地台設計者而言，可以大幅提升性能，節省 DC 功耗，如圖 6 所示。IC 所採用的一種技術，可以同時優化晶片上混頻器周圍的 RF 和 IF 級。

該技術首次用於 ADRF6612，在整個溫度範圍內和整個頻率範圍內，以及低功耗條件下，最低 IIP3 超過 25 dBm，在整個溫度範圍內則為 29 dBm 至 2 GHz。該技術還具有最佳接收路徑雜訊係數性

圖 7：圖中所示為 ADRF6612 接收器 IC 的實測增益、雜訊係數和輸入三階交調截點 (IIP3)。

能和高轉換增益，如圖 7 所示。

### 參考文獻

1. Marc Goldfarb, Russel Martin, and Ed Balboni.“Novel Topology Supports Wideband Passive Mixers.”(新型拓撲結構支援寬頻被動混頻器) Microwaves & RF ,第 90 頁 ,2011 年 10 月。

2. Marc Goldfarb.“Apparatus and Method for a Wideband RF Mixer.”(寬頻 RF 混頻器裝置和方法) ADI 公司 ,2012 年。

3. ADRF6612 數據手冊。ADI 公司，2016。

4. ADRF6614 數據手冊。ADI 公司，2016。

## 作者簡介

**Tom Bosia** [[thomas.bosia@analog.com](mailto:thomas.bosia@analog.com)]

於 2013 年加入 ADI 公司，擔任 RF 產品工程師。加入 ADI 公司之前，在 Raytheon、Cree 和 Auriga Microwave 等公司擔任 RF 測試工程師，在微波半導體領域積累了超過 25 年的經驗。2001 年獲得麻省大學羅威爾分校電氣工程學士學位。

**Russell Martin** [[russell.martin@analog.com](mailto:russell.martin@analog.com)]

於 2002 年加入 ADI 擔任產品工程師，負責 IC 產品的市場發表工作達 15 年；後來成為 ADI 公司 RF 和微波部門 (RFMG) 的工程經理。2002 年畢業於伍斯特理工學院，獲電氣工程學士學位。

**Marc Goldfarb** [[marc.goldfarb@analog.com](mailto:marc.goldfarb@analog.com)]

在類比、RF 和微波積體電路領域擁有超過 35 年的設計經驗，涉及軍事、工業和消費電子等應用。他曾從事過 SiGe / 砗、GaAs 和微波混合積體電路技術等工作。加入 ADI 公司之前，Marc 曾在 Pacific Communications Sciences, Inc. (PCSI)、Raytheon 和 MA-COM Microwave Associates 公司工作，歷任多個工程職位。他畢業於紐約特洛伊倫斯勒理工學院，獲工程碩士學位；獲 13 項專利，在參考類資料和行業期刊上發表論文多篇。

Marc 目前是 RF 和微波部門 (RFMG) 的一名設計工程師，主要負責無線基礎設施 RF IC 開發工作；目前擔任多個 5G 通訊基礎設施 (5G IC) 專案的設計

組組長。

**Dragoslav Culum** [[dragoslav.culum@analog.com](mailto:dragoslav.culum@analog.com)] 是 ADI 公司的產品線經理。他在無線通訊領域擁有超過 10 的工作經驗。2014 年，在 Hittite 併購完成後，Dragoslav 加入 ADI。他於 2008 年加入 Hittite，並歷任多個職位，包括應用工程師、行銷工程師和多個產品系列的產品線經理。Dragoslav 分別從麥克馬斯特大學和卡爾頓大學獲工程學士學位和工程碩士學位。

**Ben Walker** [[benjamin.walker@analog.com](mailto:benjamin.walker@analog.com)]

於 2003 年和 2004 年分別獲得麻省理工學院的工程學士學位和工程碩士學位。2004 年以來，他一直在 ADI 公司 RF 和微波部門工作，參與了因應無線基礎設施市場的多種電路設計工作。Ben 的興趣包括鎖相環、電壓控制振盪器和 RF 開關及衰減器設計。

**Ed Balboni** [[ed.balboni@analog.com](mailto:ed.balboni@analog.com)]

在高性能、高整合度無線電收發器電路設計領域擁有 30 年經驗。他擅長基於 SiGe BiCMOS、雙極性和 CMOS 技術設計面向通訊產品的微波、RF、混合訊號和類比電路。Ed 於 2000 年加盟 ADI 公司，在 RF IC 設計部門擔任 IC 設計師和設計經理。他在 ADI 負責開發支援無線基礎設施的高性能 RF IC 元件，包括蜂巢式基地台和點對點微波。加入 ADI 之前，Ed 曾在麻省劍橋的 Draper 實驗室工作，負責 MEMS 慢性感測器和低功耗通訊電子元件的設計。Ed 1985 年畢業於麻省大學洛威爾分校，獲電氣工程學士學位，1990 年畢業於東北大學，獲電氣工程碩士學位。

# COMPOTECHAsia 賴書

每週一、三、五與您分享精彩內容

<https://www.facebook.com/lookcompotech>