# 低功率消耗的 SRAM 與 DRAM 的關聯性

■作者：湯朝景 kurjoy-tang-sir@outlook.com

## 前言

靜態隨機存取記憶體 (SRAM) 的基礎知識是門鎖電路，始由六顆電晶體組成，並且使用差動式存取技術來完成資料寫入以及資料讀出，後來就將此命名為 6T SRAM cell 來與 5T SRAM cell 形成區別。由於五顆電晶體仍有較大的佈局面積以及較多的功率消耗，於是又有四顆電晶體以及二顆電阻器，此為 4T2R SRAM cell。本文提出在標準的 CMOS 製程技術下有一存取技術可配合往下遞減的電晶體數量，並且這一存取技術以及 3T SRAM cell 會與動態隨機存取記憶體 (DRAM) 之間具有關聯性。

## 功率消耗與電晶體的數量

電晶體的功率消耗又細分為靜態功率消耗以及動態功率消耗。電晶體的功率消耗是關聯於電晶體參數、供應電壓以及電路設計，其中，靜態功率消耗會隨著電晶體的數量而增加。在 SRAM 晶片內部有一電壓源是專門供應至儲存細胞 (storage cell)，這一供應電壓可名為細胞電壓 (V<sub>cell</sub>)。當各種 SRAM cell 皆使用相同的細胞電壓之時，六顆電晶體的結構具有最大的功率消耗，但具有最佳的穩定性、最快的寫入速度以及最寬的工作溫度範圍，另外，也關聯於存取電路的技術。

存取電路以及控制電路可以改變儲存細胞的功率消耗，其中，降低細胞電壓是最明顯且最相關的因素。一般而言，五顆電晶體的結構具有較慢的寫入速度，但在降低細胞電壓之後則可增加寫入速度，然而也有可能降低讀取速度；換言之，在寫入作業

之中要降低細胞電壓來增加速度，在讀取作業之中要升高細胞電壓來增加速度，但是，要動態地改變細胞電壓也需要額外的控制電路以及切換時間。英特爾公司 (INTEL corp.) 有一專利申請號 PCT/US11/68286，對應臺灣專利申請號 101149814，這一專利文件的主要技術是有一可變電壓源 (Variable Voltage Source) 可在寫入期間降低細胞電壓，並且在讀取期間升高細胞電壓，此一技術正符合本人在 2006 年 10 月所發表的文章，可參「記憶體設計探索，電子與電腦，90 期」。

當儲存細胞的電晶體數量在六顆以上就不止會有較多的功率消耗，也會增加存取電路以及控制電路的複雜度，並且在一般設計上會使用差動式存取電路，甚至會有更多的控制信號穿梭於記憶體陣列而增加佈局的複雜度。當電晶體數量等於五顆就會在功率消耗以及記憶能力的穩定性達到最佳的平衡。當電晶體數量在四顆以下並且不使用差動式存取電路則會形成單軌且強健的記憶體 (Single-Rail-and-Robust Memory)，意即某一邏輯準位具強穩定性，另一邏輯準位具弱穩定性。在標準的半導體製程之下，如今被區別為 Bulk CMOS 製程，三顆電晶體會是 SRAM 技術的極限。

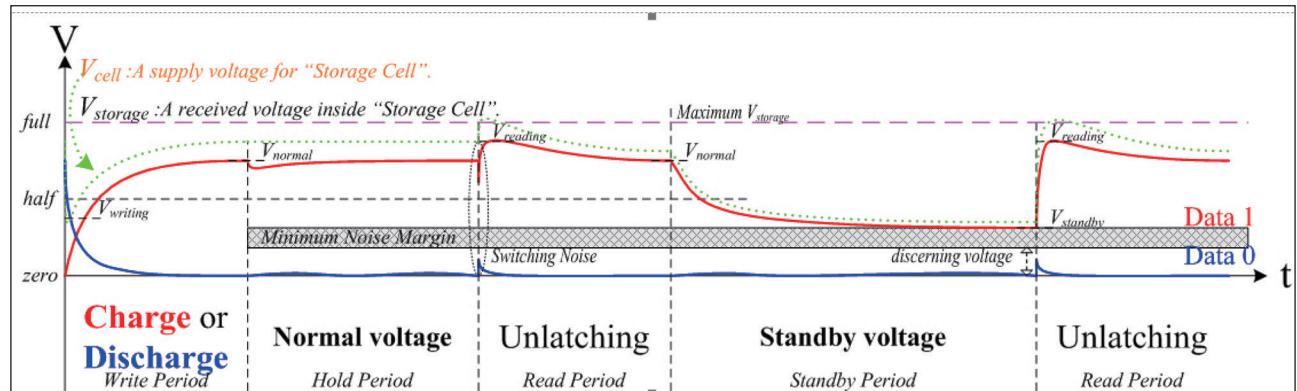

由於門鎖電路在記憶能力上具有一定的穩定性，於是多數的細胞結構皆可降低細胞電壓來減小洩漏電流，所以可將工作電壓區分為常態電壓 (normal voltage)、寫入電壓 (writing voltage)、讀取電壓 (reading voltage) 以及待機電壓 (standby voltage)，這些工作電壓的準位關係像是讀取電壓高

於或等於常態電壓，常態電壓高於或等於寫入電壓，寫入電壓高於或等於待機電壓；換言之，門鎖電路對於工作電壓具有非常寬廣的範圍。圖 1 是工作電壓的示意圖用於呈現這些工作電壓在各作業期間的波形，這些電壓準位也可降低。其中，待機電壓的最小值也與電晶體的溫度係數有關，像是溫度升高會增加洩漏電流則可降低待機電壓；要降低常態電壓就不止關聯於電晶體的次臨界電流，也要提升存取電路的性能。

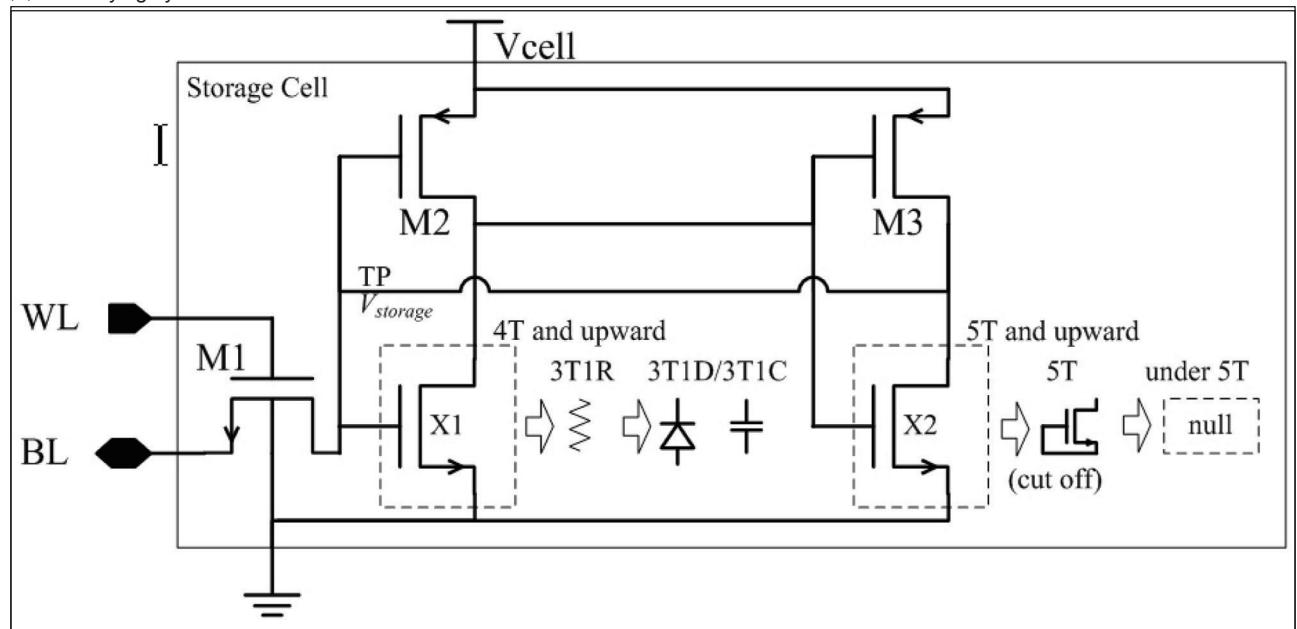

圖 2 呈現關於細胞結構從五顆電晶體發展至三顆電晶體的過程，這一細胞結構的設計是配合單端式存取電路，所以使用單一位元線 (BL) 來傳輸資料。圖中有標記 M1, M2, M3, X1, X2，這些元件組

成儲存細胞，還有一測試點 (TP) 用於探測儲存細胞的儲存狀態，它的電壓值即是儲存電壓 ( )。在五顆電晶體以上的結構會有 X1 以及 X2，其中，若令 X2 的電晶體一直處於截止區 (cut off region) 就可在超過工業規格的溫度範圍之後仍然可以高速寫入，並且資料穩定的能力也可輕易達到軍用規格的溫度範圍。在四顆電晶體以下的結構會有 X1，像是 4T, 3T1R, 3T1D, 3T1C。在這上述的細胞結構之中，4T SRAM cell 的優勢在於佔用很小的佈局面積而能達到高速存取以及很寬的工作溫度範圍，也就是這結構在穩定性、存取速度、佈局面積之間取得了最佳的平衡。

圖 1:Waveform for all periods of 4T and upward or 3T1R SRAM cell

圖 2:A varying symbol for 5T to 3T SRAM cell

### 3T SRAM Cell

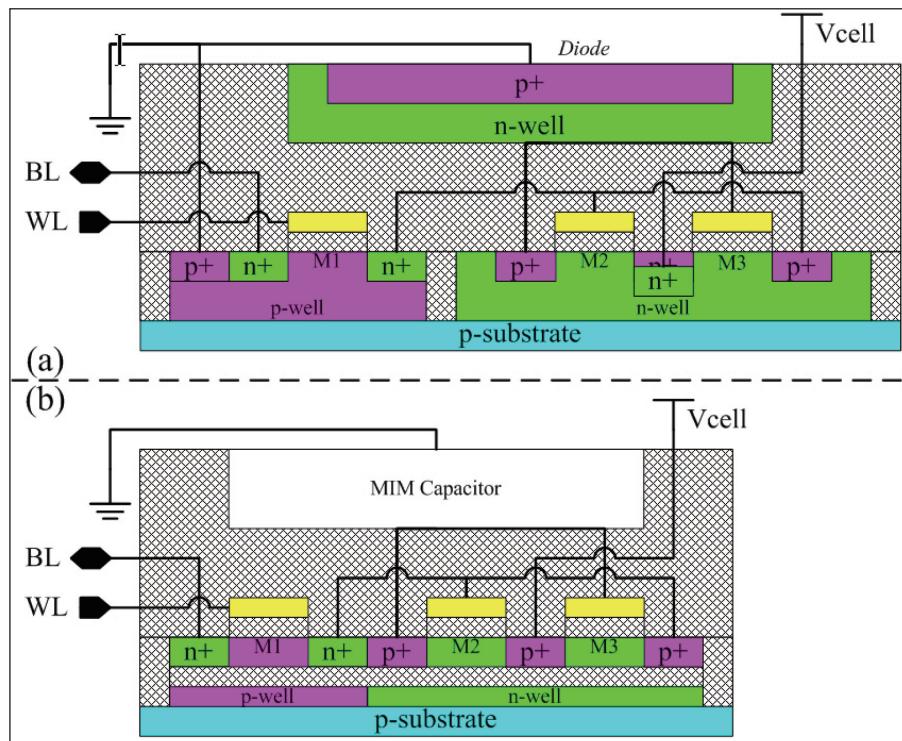

3T1R SRAM cell 是基於 4T2R SRAM cell 的設計構想，即是引入高阻抗電阻器的製程來縮小佈局面積：3T1D/3T1C SRAM cell 可輕易嵌入到系統單晶片 (SoC) 之中，甚至更容易達到低功率消耗的設計目標，這一技術思想已經申請專利保護；以上這些細胞結構可以統稱為 3T SRAM cell。圖 3 所呈現的物理結構是關於 3T1D/3T1C SRAM cell，並且使用垂直堆疊 (vertical stack) 的製造技術來縮小佈局面積。

圖 3(a) 是 3T1D SRAM cell，它的電器特性是結合電晶體的切換特性以及二極體的逆向飽和電流，所以靜態功率消耗會受到逆向飽和電流的約束，除此之外，M1 不止有一洩漏電流，還有一基體電流，故此能夠增強記憶能力。圖 3(b) 是 3T1C SRAM cell，它的電器特性是結合電晶體的切換特性以及電容器的直接穿透電流，並且使用絕緣體上矽 (SOI) 的製程技術。上述二者的存取特性不同於 3T1R SRAM cell，這迥異的特性來自於逆向飽和電流以及直接穿透電流，這些電流導致其餘電晶體的

圖 3:Physical structures of 3T SRAM cell by vertical stack

工作區域產生了微妙的變化，導致寫入電壓有可能低於待機電壓，除此之外，更容易發生破壞性讀出 (destructive readout)，故此對於存取電路的性能會有更嚴峻的挑戰。

### SRAM 與 DRAM 的關聯性

由於 3T SRAM cell 很容易發生破壞性讀出，並且對於存取電路的性能有更嚴峻的要求，所以在整理 3T SRAM cell 的電器特性時突然發現到動態隨機存取記憶體有其相似之處，這也促成那些用於 SRAM cell 的存取電路也可轉用到 1T1C DRAM cell。一般而言，1T DRAM cell 是使用差動對的位元線來傳輸資料，這一特點類似 6T SRAM cell，除此之外，又要在完成預充電之後才能讀取資料，這一特點是各種 SRAM 所不必進行的動作，所以這二者在存取技術上是完全不相關，當然也對應完全不同的存取電路以及控制電路。然而，當 SRAM 的細胞結構可以設計到三顆電晶體的時候，加上存取電路可以對這種細胞結構完成寫入作業以及讀取作業的時候，對於 1T DRAM cell 的存取技術就發

生了出乎意料之外的新發展，這使得它的存取速度可以相當於 SRAM，所以可稱這發展誕生了第三代 DRAM 技術；另外，它的儲存電壓在寫入期間以及保持期間的波形如同 3T DRAM cell 的儲存節點 (storage node)。

現今可稱 3T DRAM 是第一代 DRAM 技術，這時期是使用單端式寫入位元線以及單端式讀取位元線來分別進行寫入資料以及讀取資料，這就像是雙埠存取 (dual-port access)；為了縮小佈局面積而誕生了第二代 DRAM 技術，亦即 1T DRAM。圖 2 是使用單一位

元線來進行存取資料，所以本文將這樣的儲存細胞所形成的陣列結構命名為單端式儲存陣列 (Single-Ended Storage Array)，與其相對的陣列結構就是差動式儲存陣列 (Differential Storage Array)，像是 6T SRAM 以及第二代 DRAM 技術。

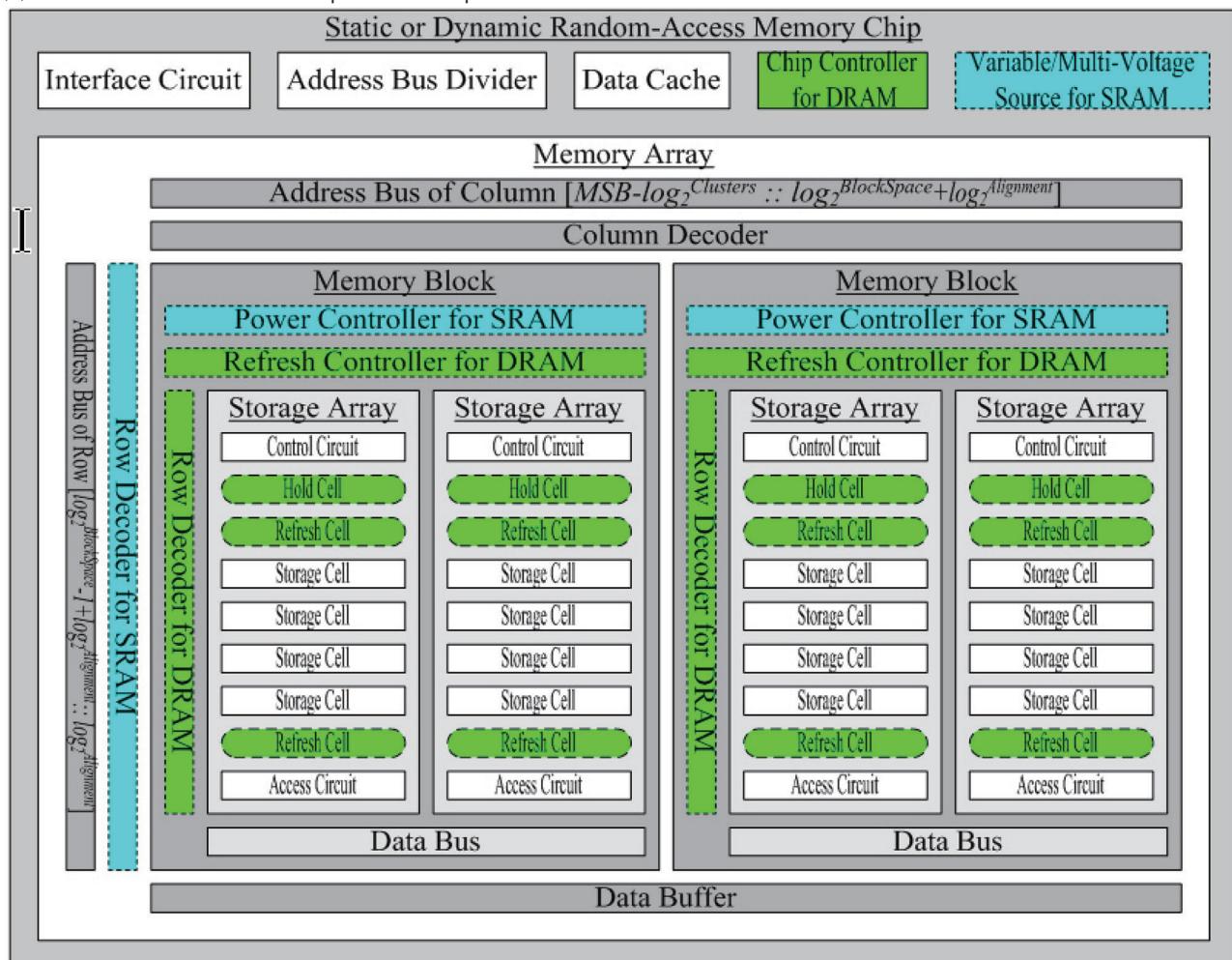

圖 4 呈現 SRAM 晶片或 DRAM 晶片的內部架構，這些記憶體晶片會配置許多儲存陣列，本文將這些儲存陣列所形成的佈局區域命名為記憶體陣列，並且這又可分割出許多記憶體區塊，還可聚集這些記憶體區塊成一區塊簇 (Block Cluster)。這些記憶體區塊配置相同的定址空間，簡稱區塊空間，這一區塊空間包含多個與資料寬度相等的單端式儲存陣列，或是包含多個與半數資料寬度相等的差動式儲存陣列。

圖 4: A architecture inside SRAM chip or DRAM chip

當要求 SRAM 晶片實現各記憶體區塊各自省電之時就需要使用多電壓源 (Multi-Voltage Source) 的設計，當要求晶片實現整體切換常態電壓以及待機電壓之時就需要使用可變電壓源的設計，甚至可以將其混合使用；另外，寫入電壓以及讀取電壓的切換電路則設計在功率控制器 (Power Controller) 之內來達到高速存取的要求。DRAM 晶片在記憶體區塊之內包含更新控制器 (Refresh Controller) 以及列解碼器即可經由平行技術來執行局部更新作業。

## SRAM 相對於 DRAM 的功率消耗

多數文獻對於 SRAM 以及 DRAM 的功率消耗未有公平的對照參數，並且多以單一 6T SRAM cell 對比單一 1T DRAM cell，那些研究人員顯然無視

SRAM 的發展以及 DRAM 的劣勢。如果能令這二者使用相同的製程參數以及相同的容量則有公平的比較基礎，並且多數位元在多數時間是處於資料保持狀態，除此之外，DRAM 需要更新電路以及頻率產生器來維持儲存狀態，甚至需要晶片控制器 (Chip Controller) 來管理資料流量以及控制命令，然而，SRAM 可降低細胞電壓來減小功率消耗，所以，從相同長久的保持期間來比較維持儲存狀態所產生的功率消耗才能進行較量，這才有正確的分析原則。

當 SRAM 技術可由三顆電晶體來實現之時就不止縮小佈局面積，也能兼具效能以及省電，相對地，DRAM 技術不能降低工作電壓也不能去除更新電路，所以 DRAM 技術在這時的優勢將止於佈局面積。

## 結論

在使用 INTEL 80286 處理器組成個人電腦的時期，延伸式記憶體以及擴展式記憶體皆是當時為了增加記憶體空間以及提高存取速度的硬體擴充技術，又有 RAM Disk 技術來替換軟碟機的資料存取，所以，使用隨機存取記憶體取代硬碟機也是行之有年的傳統。在伺服器連接高速的電腦網路又加入雲端運算的技術之後，頻繁的資料存取以及超大資料量的高速處理就需要高速的主記憶體搭配高速的儲存裝置，像是電池備份靜態隨機存取記憶體 (BBSRAM) 以及非揮發靜態隨機存取記憶體 (NVSRAM)，那麼對於 SRAM 技術以及 DRAM 技術在存取速度以及功率消耗的規格要求也會提高。

## 作者介紹：

湯朝景：2012 年至 2017 年在經濟部智慧財產局任職專利審查委員。發表相關的期刊如後：「記憶體設計探索，電子與電腦，90 期，2006/10」；「善用 CMOS 特性 3T SRAM 技術難題有解，新電子科技，2012/5」；「DRAM 的技術瓶頸與創新，電子工程專輯，2017/9」；「DRAM 的創新技術與製程微縮，電子與電腦，221 期，2017/9」。

## 首屆“全球程式設計師節” 共議“軟體定義世界”

首屆“全球程式設計師節”日前在大陸西安開幕，全球程式設計師與來自海內外的軟體行業意見領袖、“一帶一路”沿線國家代表、大陸“一帶一路”門戶城市政府、知名軟體企業、軟體創企、大學和科研機構等各界嘉賓薈聚西安。

我們的世界正在以前所未有的速度進入一個更加智慧的時代。科技的進步和升級，離不開軟體程式的支援。軟體已經在我們的身邊無處不在，正實實在在地改變我們的生活，對人類世界的重要性與日俱增。“軟體定義未來”不再只是一句口號。這些軟體程式的背後，就是千千萬萬的程式設計師。正是他們，用程式為我們構建了全新的數字世界。

作為程式設計師群體的盛會，全球程式設計師節以“Coding the Future( 碼未來 )”為核心主題，首屆全球程式師節聚焦與探索“一帶一路”發展契機，以“數位絲路 碼動未來”為年度主題。

大會“碼動思想”論壇，聚集了軟體產業的產業領袖和新銳力量，共同分享、探討、展望軟體產業的未來發展之路。除了最先進的軟體技術與工具，碼動思想主論壇還就中國軟體產業的創新前景進行了深度剖析及共同思考數字時代的程式設計師將面臨哪些新的變革和機會。

本屆活動主要由“碼”動思想論壇、“碼”創科技展覽、“碼”出智慧大賽、“碼”喚激情嘉年華等活動組成。活動由西安市人民政府、中國電子資訊行業聯合會共同主辦，由西安軟體園和中軟國際有限公司負責具體執行工作。此次為期兩天的活動，線下參加總人數超過 1 萬人，核心嘉賓、重要來賓約 400 人，線上關注與參與的程式師群體粗略估計將超過 100 萬人。