# 5G 設計／製造／測試／驗證，AI 神救援

■文：任莢萍

去年由工研院主辦的「2019 國際超大型積體電路技術研討會」(VLSI) 上，台積電 (TSMC) 曾預言，5G 半導體潛在市場容量 (TAM) 將分為兩階段增長：2020～2024 年是電信業務、2025～2027 年將以企業端為主力。從 4G 跳到 5G 系統，基礎設施核網到 BBU (基頻處理單元) 及 RRU (遠程射頻單元) 的元件數是 4.5 倍、總功率是 2.5 倍，終端方面更面臨以下挑戰：

1. Sub-6GHz、毫米波 (mmWave) 將分頭並進，且將與 Wi-Fi 801.11 ax/ay/ad 並存；2. 運算力須提升

30%、功耗逾兩倍、感測器超過 10 個、攝影鏡頭大於 3 個。

為此，技術有三大要求：一是更高的運算力，數據吞吐量須提升百倍、延遲減少 30～50 倍；二是功率及頻寬須增加 2.5 倍；三是射頻 (RF) 與邏輯的整合——100 倍連接、20 倍載波聚合 (CA) 組合以及多接入多輸出 (MIMO)。更高的數據傳輸率和頻寬需要更多數位 RF 支援，是 4G 的兩、三倍，可經由技術演進改善 RF 電路效能：

1. 單元容量變大，先進節點可帶來更好的數位內容並減少功耗；

2. 採用整合扇出型 (InFO) 封裝可藉由重分佈製程 (RDL)、更高品質的電感和整合式被動元件 (IPD) 增強 RF 收發器效能；3. 可拿掉基板，以減少封裝厚度。

## 「相位陣列」是啓動毫米波應用的鑰匙

此一創新作法，為 CMOS 帶來更多機會。相較於 III-V 族分立式器件，整合矽光子學 (SiPh) 的 CMOS 外形僅有 1/10、單一 Gbps 功耗 < 5 mW、且成本只有 1/6。

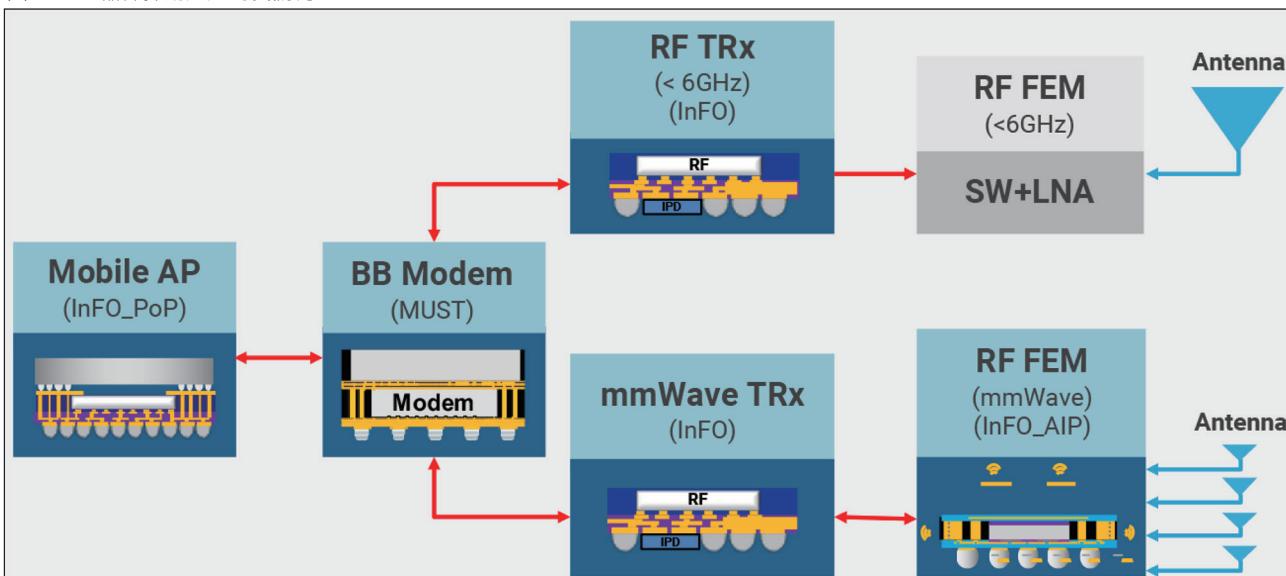

圖 1：5G 器件採用先進封裝概況

資料來源：TSMC：[https://www.tsmc.com/chinese/dedicatedFoundry/technology/platform\\_mobile\\_tech\\_WLSI.htm](https://www.tsmc.com/chinese/dedicatedFoundry/technology/platform_mobile_tech_WLSI.htm)

台積電指出，在系統級設計方面，基礎設施的關卡包括邏輯之間、記憶體與被動元件的整合，設備端除了上述後兩者外，以天線整合為最大課題。台積電介紹，他們的整合型晶圓級天線封裝 (InFO\_AiP) 具有均質 RDL，可獲得更高的增益並降低必要損耗，同時以毫米波射頻前端模組 (FEM) 晶片整合偶極 (dipole) 和天線貼片 (patch)。

簡言之，台積電的策略是以先進邏輯建構運算、以專有技術實現連接、以先進封裝成就整合。他們強調，自有整合技術平台有助於 5G 和人工智慧 (AI) 系統級創新。另一晶圓廠格羅方德 (GlobalFoundries) 提到，雖然受限於大氣吸收與向農限制 (或稱為「香農限制」，Shannon limit，指在特定雜訊標準下之信道理論的最

大傳輸率)，傳輸距離短是缺點，但毫米波在 5G 通訊仍有兩大優勢：1. 毫米波較 Sub-6GHz 擁有更多可用頻譜；2. 具備高頻、小波長特性，天線更小，利於窄波束及高指向，而相位陣列 (phased array) 是啟動毫米波應用的鑰匙。

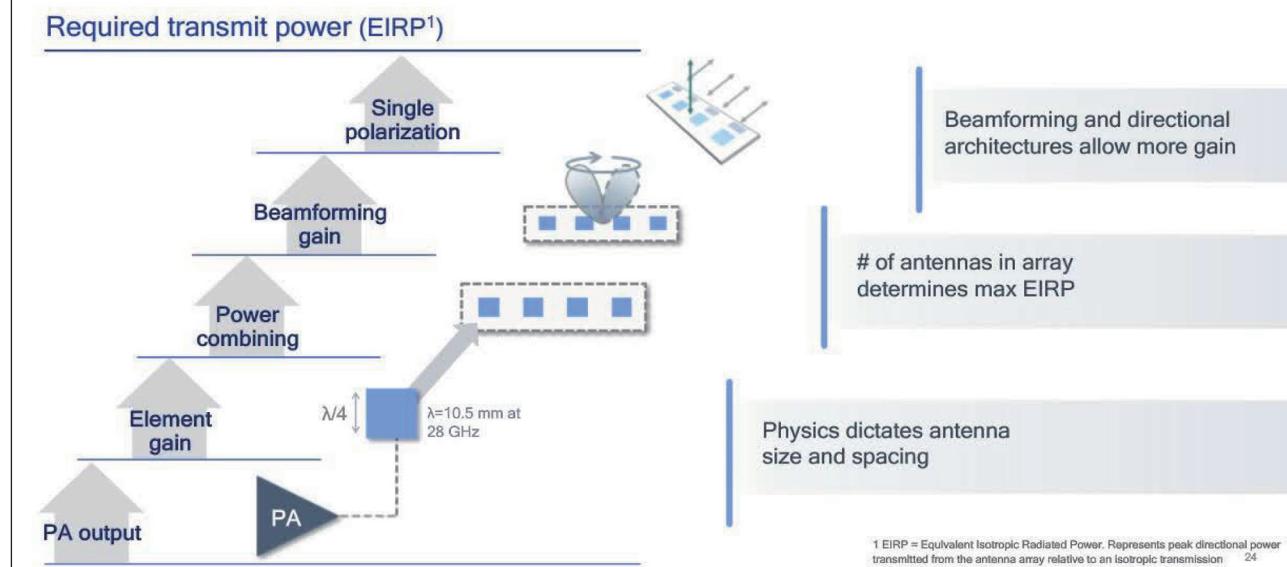

遵循「等效全向輻射功率 (EIRP) = 總輻射功率 (TRP) + 方向性」，短距離、高聚焦的天線波束，可利用空間多工 (Spatial Multiplexing) 減少發射功率／元件；而大型陣列的放大器發射功率需求一旦降低，就可以現行矽技術實現。在特定毫米波頻率下，EIRP、接收靈敏度、器件尺寸和功率預算，將決定陣列大小及波束成形 (Beamforming) 架構。高通 (Qualcomm) 補充， $EIRP (\text{dBm}) = P_{\text{out}} (\text{dBm}/\text{element}) + \text{波束成}$

形增益 + 天線增益，在既定 EIRP 下，倍增毫米波天線單元數量能降低四倍元件發射功率及兩倍直流功率消耗，進一步窄化波束、改善空間過濾效果。

## PA 在毫米波通訊扮演關鍵角色

然而，此舉的代價是：電路板空間也要隨之倍增，且設計更趨複雜、收發器成本也更高。另高通指出，為求完整覆蓋，用戶設備 (UE) 會設計多天線模組，通常有兩種設計：一是位於表面，每個模組有 2X2 雙極化 (dual-polarized) 貼片陣列、1X2 及 2X1 偶極 (dipole) 陣列；二是在邊緣，每個模組有 4X1 雙極化平面 (planar) 陣列。有限外觀尺寸／基板面積、多元信道衰減和阻塞是必要考量，

圖 2：行動毫米波之發射功率衡量

### Achieving required transmit power for mobile mmWave

資料來源：高通：<https://www.qualcomm.com/invention/5g/5g-nr/mmwave>

且初期天線模組的設計將受制於分立式 RF 晶片。統整毫米波 UE 難點涵蓋：

1. 波束方向變換及子陣列轉換迅速；

2. 偏振 (polarization) MIMO；

3. 為提升效率和散熱效能，須最小化後置放大器損耗；

4. 為改善鏈路預算 (link budget)，須最小化前置低雜訊放大器 (LNA) 損耗；

5. 最小化總成本。

高通認為，III-V 族技術在截止頻率 (fT) 加乘崩潰電壓 (BV) 優於 CMOS，毫米波頻率的雜訊指數 (Noise Figure) 亦更為合理；惟 UE 應用的整合複雜度仍極具挑戰。現階段，28 nm Bulk CMOS 最適合用於設計 5G NR 毫米波晶片，而 Bulk CMOS 電容可透過優

化基板提供不錯的開關效能。毫米波的大頻寬也是課題。受限於截止頻率，每個位階的收發增益會降低，使許多負載 LC 諧振 (LC tank) 導致落降 (droop)、造成頻帶訊號衰減。超外差 (Super Heterodyne) 架構會導致中頻 (IF) 產生大分數頻寬 (FBW)，對於系統中的其他無線電和時脈介面更易感。

振幅調變／相位調變 (AM/PM) 及 AM/AM 頻寬擴張，亦使數位預失真 (DPD) 工作更加困難，包括整個天線陣列和其中單一元件 DPD、以及量測接收器能力和數量。最後，是 GHz 頻段的寬頻 ADC/DAC 取樣問題。高通還提到，功率放大器 (PA) 在毫米波通訊扮演關鍵角色，須滿足以下要求：

1. 功率：收發堆疊和功率梳理

- (power combing)；

2. 強固性：PA 的耐用度及老化效應；

3. 線性度 (linearity)：為 AM/AM、AM/PM 做適應性誤差的 Class AB 設計；

4. 效率：或可借助 Doherty 功率放大器改善功率退回 (Power Back-off, PBO)；

5. 整合：PA/LNA/SW 協同設計以合併匹配網路；

6. 成本效益。

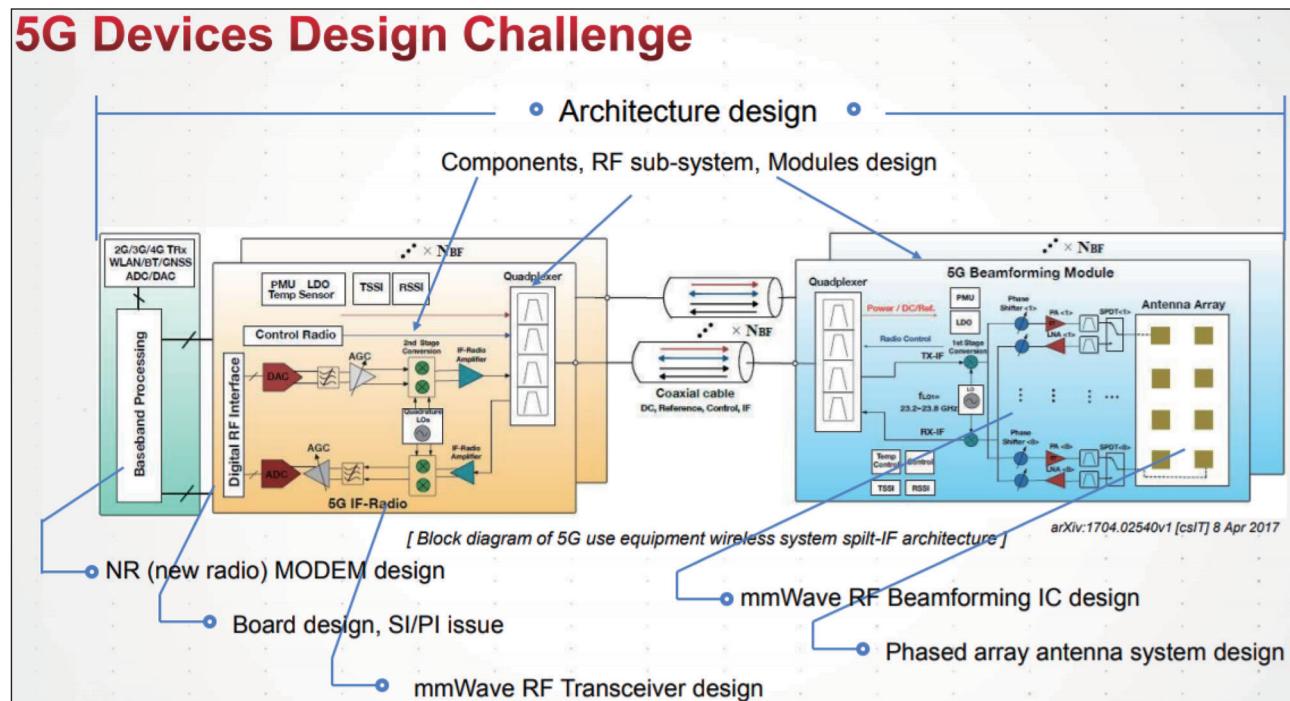

## 設計、製程、測試、驗證，步步為營

高通說明，PA 器件在初期 T0 和產品生命終期需更高的最大振盪頻率 (fmax) 和良好可靠度。當趨近飽和功率 (Psat) 和高後退 (back off) 以支援 QPSK 和 64 QAM 時，

圖 3：5G 裝置設計的挑戰

## 5G Devices Design Challenge

資料來源：keysight : [https://keysightevent.com/kw2019/handout/pdf/a6/\(A6\)%203GPP%205G%20NR%20System%20Design%20&%20Verification%20Solution\\_Jiarui%20Wu.pdf](https://keysightevent.com/kw2019/handout/pdf/a6/(A6)%203GPP%205G%20NR%20System%20Design%20&%20Verification%20Solution_Jiarui%20Wu.pdf)

Class AB PA 會發送較高的輸出功率 (Pout) / 功率輔助效率 (PAE)，而藉由 PA 差異化堆疊可減少器件可靠度顧慮，將 PA 輸出匹配與 LNA 輸入匹配共同設計是毫米波收發器成功的關鍵。其次，由於電容元件較大，伴隨 Bulk CMOS 頻率而來的轉換場效電晶體 (SW FET) 導通電阻 (Ron) 與插入損失 (Insertion loss) 將增加，且基於多堆疊 SW FET 之空乏電容 (Coff) 特徵值將被低估。

優化 SW FET 的源極／汲極 (source/ drain) 金屬重疊狀況，可減少 25 ~ 50% 的 Coff 特徵值——視「接觸式間距」(Contacted Poly Pitch, CPP) 而定，另閘極過驅動 (overdrive gate) 可減少 10 ~ 15% 的導通電阻、基極偏壓 (Bulk Bias) 可減少 10% Coff，且優化 Bulk CMOS 元件基板，可減少電容值。高通總結，單晶片 (SoC) 需要製程技術整合 PA、LNA、SW、移相器 (Phase Shifter)、本地振盪器 (LO) 和智慧控制元件以實現簡單、小巧的天線，而 PA 和 LNA 設計離不開可靠、低雜訊的 RF 器件，優化金屬堆疊則可獲得電磁 (EM) 更佳的器件及 T-line routing。

是德科技 (Keysight) 5G 計畫總監 Roger Nichols 表示，加入行動網路營運商生態系統需要一連串測試：開發初期須對調製解調器、晶片和晶片組進行不同測試，以滿足性能要求及許多可供製造的測量標準，符合所謂「可製造性設計」(DFM) 和「可測試性設計」(DFT)；其次是一致性測試，確保設備在任

照片人物：是德科技 (Keysight) 5G 計畫總監 Roger Nichols

何地方皆能運作。營運商還會有個別測試，勒令設備和基地台的網路以相同方式工作，暢行無阻。更重要的是，無線基地台有不同體系，集成度越高、測量工作越不能掉以輕心，須格外留意空中傳輸 (OTA) 的兩端測量值是否會因增益或干擾而有所扭曲。

### 5G 問市三寶：GCF/PTCRB 准入認證、互操作性、無線電資源管理

EIRP、TRP 與有效的無方向性敏感度 (EIS) 是 5G 毫米波 OTA 驗證的三大重點項目。波束成形是 5G 毫米波的關鍵要素，但毫米波無法穿透物體且傳輸距離有限，故需將訊號定向到待測物 (DUT) 周圍，配合大量的微型基地台發送訊號、後由天線陣列接收。Nichols 表示，集成度將決定是否可透過導導方式進行測量，若天線的引線被

內嵌在裝置中、無法用纜線簡單對接，OTA 遂成唯一測試途徑。此外，為降低大型天線測量的暗室成本、測量時間和空間，宜使用「間接遠場」量測高頻毫米波，即「縮距天線量測場」(CATR)。

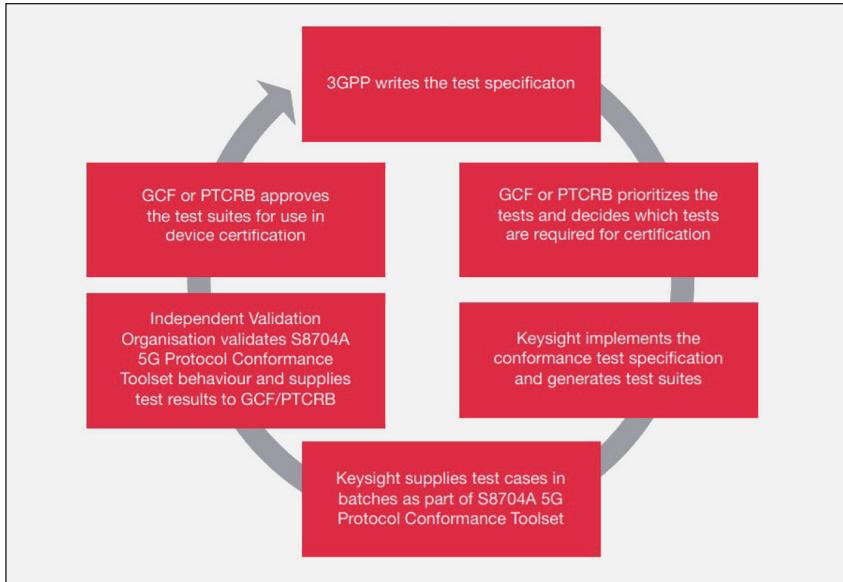

除了基本的電磁干擾 (EMI) 測試，Nichols 分別就基地台和 UE 兩部分說明：基地台的重點在於相鄰頻帶的訊號靈敏度和抑制等性能測量，例如，上行鏈路共享信道與接入信道周圍的控制信道是否正常運行？才能據以處理互調失真。UE 測試更見複雜，基於測試成本考量，通常僅會針對一致性或 GPS Global 進行認證——此動作類似 Wi-Fi 的 DCF (分佈式協調功能)，限縮必要的 UE 測試範圍，為此，測試設備公司會與 3GPP 中的全球認證論壇 (GCF) 與美國聯邦通信委員會 (PTCRB) 等機構緊密合作，這些測試被視為是營運商准入認證。

圖 4：5G 需求驗證環節

資料來源：Keysight：<https://www.keysight.com/tw/zh/assets/7018-06566/technical-overviews/5992-3832.pdf>

除了場域測試，還要確認協定系統和天線是否能正常工作——「互操作性測試」旨在確保對 UE 的數學運算正確，並再次驗證偏離中心操作時的 RF 收、發是否良好。這是一項性能測試，須正確操作才能驗證物理通道。開發者還得讓通訊設備在正確的時間點、根據呼叫運行訊號管理工作——即「無線電資源管理」(RRM)，可透過協定系統正確控制 RRM 測試示例。UE 處

理切換的聲音大小或毫米波處理，與選擇 RRM 的性能與移動性有很大關係，故須進行大量測試，包括將散熱片 (radiator) 等所有可能影響 RF 效能的權重變數考慮在內。

## 5G、AI 相互為用

毫米波空間中的所有方向皆是自由定向，且所有移動皆是單向；只要改變接收方位，就可改變移動方向。特別一提的是，若高頻

訊號無法從近場直接轉換到遠場，須確保其平面波存在待測物上，才能準確測量；而不同類型的間接遠場，可能充斥競爭對手的多個角度 RRM。另有量測設備業者表示，目前 5G 的最大增長主力仍在行動消費市場，由於 Sub-6GHz 的 5G 設備可與 4G 基礎設施共用（非獨立組網，NSA），該頻段將成為 5G 先鋒部隊；惟因頻譜資源實在有限，毫米波終究是未來必經之路。

麻煩的是，如果只是連接無線電和天線做測試，因為沒有考慮到增益效果或雜訊干擾，無法真正量化定向波束的形態而影響訊號調變，所以 OTA 測試頓成熱門。因應大批量生產 5G 毫米波所需，OTA 測試設備需有運動元件相助，包括：將光學前端傳送到小型無線電前端，以及將集中的無線接入網路基頻做邊緣運算。面對諸多繁複工序、且可能是全新的學習曲線，AI 將可加速原型設計、模擬、除錯到驗證的時程。由此可知，5G 不僅是通往 AI 的捷徑，易地而處，AI 也是鋪設 5G 錦繡前程的左膀右臂。

# COMPOTECHAsia 驗書

## 每週一、三、五與您分享精彩內容

<https://www.facebook.com/lookcompotech>