# 不只是加速協作！ FPGA 展露大將之風

■文：任莢萍

照片人物：賽靈思軟體與人工智慧資深經理羅霖

智慧應用不斷推陳出新，最初被用於概念驗證 (PoC) 的現場可編程邏輯閘陣列 (FPGA)，地位亦不可同日而語。龍頭廠商賽靈思 (Xilinx) 表示，近幾年來在一個電路板上，FPGA 可作為中央處理器 (CPU)、圖形處理器 (GPU) 或微控制器 (MCU) 的加速引擎或協作處理器，然而如今的 FPGA，擔當主控的能力可毫不遜色！賽靈思軟體與人工智慧資深經理羅霖直指，5G 通訊、自動駕駛、感測器融合 (Sensors Fusion) 演算法演進極

快、且效率要求高，FPGA 憑藉配置靈活特性、加上安謀 (Arm) 強力生態的助攻，FPGA 隱然有升格主角之勢。

## ASIC 等級的 FPGA X SoC 等級的設計套件

Zynq-7000 全可編程應用處理器單晶片 (AP SoC)，是 Xilinx 開啓異構運算的經典，採 28nm、集 FPGA 硬體可編程性與 Arm 軟體編程兩者之長，不僅能實現關鍵分析與硬體加速，還能結合各式 CPU、數位訊號處理器 (DSP)、專用標準產品 (ASSP) 及單一元件混合訊號，有利於客製化智能、差異化獨特應用。第二個好處是讓編程工具更加友善、降低開發者的進入門檻：Zynq-7000 所使用的 Vivado HLx 版本開發套件乃是基於 C/C++、OpenCL (開放運算語言) 和 IP 設計優化而成、且可重複使用，能協助 FGPA 新手盡速駕輕就熟並整合自動化。

羅霖評估，傳統專用晶片 (ASIC) 的設計約需 1~2 年，但 FPGA 從設計到量產最快不到一年就能完成，特別適合用於開發大量

新應用。再者，豐富的作業系統 (OS)、中介軟體 (middleware)、堆疊 (stack)、加速器 (accelerator)、多重軟／硬體保全機制，以及序列、平行、MIPI 和感測器等 I/O 週邊接口，也是各家 FPGA 廠商力拼的基本配備，以最佳化系統層級效能。Xilinx 於 2013 年首開先河、採 20nm 製程導入全新 UltraScale 可編程架構，解決系統流量擴充、延遲率與晶片互連的瓶頸，標榜是「ASIC 等級的 FPGA」，運算效能媲美專用晶片。

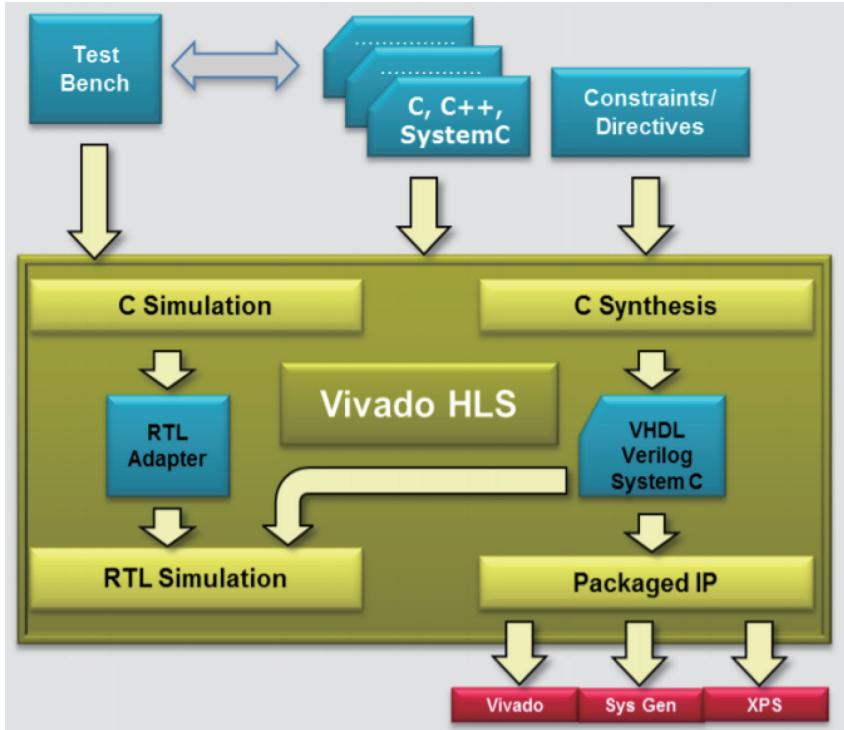

同年震撼業界的還有「首款 SoC 等級的 Vivado 設計套件」，擁有可加速 C / C++ 系統級設計和高階合成 (HLS) 完整函式庫，將視訊處理功能整合在跨平台電腦視覺庫 OpenCV，方便開發者在雙核心 Arm 處理器嵌入視覺運算功能。此前，FPGA 雖以設計彈性著稱，但自成一格的編程環境也讓不少人望而生畏；有了這套貼心配備，開發者在開發 Arm-based 處理器的同時，能經由 FPGA 為密集運算自動加速，號稱較硬體加速的 C/C++ 演算法提升百倍效能。此外，相較於 RTL (暫存器傳遞語言) 設計流程，Vivado HLS 亦可讓系統驗證

圖 1 : Vivado HLS 工作圖

資料來源：Xilinx 官網：[https://www.xilinx.com/support/documentation/sw\\_manuals/xilinx2014\\_1/ug902-vivado-high-level-synthesis.pdf](https://www.xilinx.com/support/documentation/sw_manuals/xilinx2014_1/ug902-vivado-high-level-synthesis.pdf)

和建置時間加速百倍。

## 「異構多重處理」深受智能攝影機&邊緣 AI 青睞

之後，因應多重處理興起，2015 年緊接推出 16nm Zynq UltraScale+ MPSoC (異構多重處理系統晶片)，集成多達七個可編程處理器 (含 AP、即時處理器和圖形處理器)。今年初瞄準規格仍在不斷完善的 5G 通訊再推第二代 Zynq UltraScale+ 射頻 (RF) 單晶片，已於 6 月正式量產，能涵蓋 sub-6GHz 所有頻段、支援直接射頻取樣；近期將問市的第三代元件再延伸毫米波 (mmWave) 介面，讓覆蓋更完整，並減少 20% 功耗。不過羅霖透露，穿戴式的消費電子

設備功耗須壓在 1W 以下，現階段並非 Xilinx 的目標市場。

相對的，智能攝影機 (< 5W) 和邊緣人工智慧 (AI) 設備 (> 10W) 是他們主力所在，尤以車用先進駕駛輔助系統 (ADAS)、保全監控、無人商店、無人搬運車

(AGV) 和自動光學檢測 (AOI) 最為看好，它們各自有著嚴謹的行規：馬達控制等工業應用有 IEC 61508 安全標準把關；車用除了須滿足 AEC-Q100 晶片可靠度外，隨著自動駕駛程度的提高，ISO 26262 等功能性安全 (Function Safety) 日受重視，而 Xilinx 車用產品大都已符合 ASIL C 或 D 安全等級。順帶一提，FPGA 雖可支援浮點運算，但不少專家主張 ADAS 較適合「定點量化」運算。

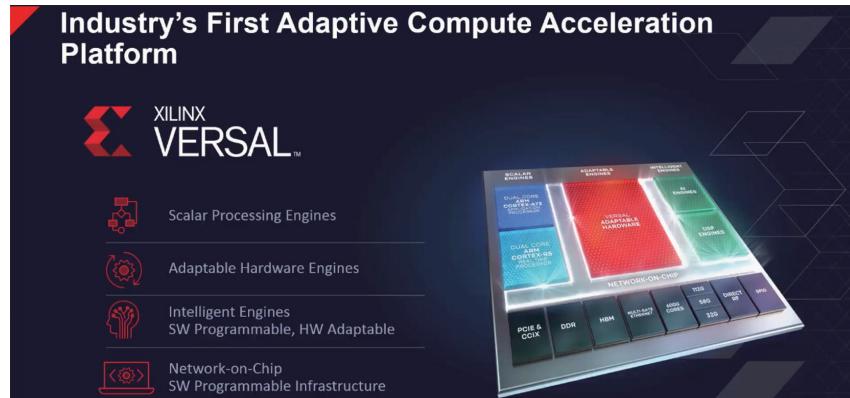

對此，羅霖解讀：定點因為效率較高，的確是圖像、影像和通訊的主流技術；以精確度取勝的浮點，則較適合天氣或金融等敏感資料的應用，取決於對資料容忍度而定。另一方面，靜態圖像 vs. 動態圖像的運算側重也不同，關鍵在於：低延遲，動態連續稍縱即逝，而靜態沒有時間概念，對延遲較寬鬆。他還提到，與記憶體的數據往返亦是影響延遲的因素之一，FPGA 的分佈式片上記憶體可按需配置，對運算效能也有幫助。Xilinx 在 28nm、20nm 和 16nm 投產皆拔得頭籌，去年底發佈的「Versal」ACAP (自

圖 2 : Versal ACAP 是業界第一個自行調適運算加速平台

資料來源：Xilinx 官網：<https://www.xilinx.com/video/acap/versal-industrys-first-acap.html>

行調適運算加速平台)，再次於 7nm 先馳得點。

## 接軌 AI，「軟體定義硬體」時代來臨！

Versal ACAP 當中的 Prime 系列與 AI 核心系列於 2019 下半年開始全面供應。其最大特色是：內嵌純量處理引擎、自行調適硬體引擎、搭載先進記憶體和介面技術的智慧引擎，可提供異質加速、擴展性及 AI 推論能力（號稱較 GPU 高出八倍）。此外，此平台的系列產品可從任一引擎直接存取記憶體並支援客製化記憶體階層，可進一步優化處理效能；且內建所有元件皆透過具備主從連結埠的網路單晶片（Network on Chip, NoC）互連，每秒傳輸頻寬達太位元（Terabit）並兼具低延遲、低高耗及原生軟體的可編程能力。

羅霖總結，單一功能的 ASIC 不易應對複雜場景及日新月異的 AI 演算法，為匹配多元演算法，「軟體定義硬體」已是大勢所趨；而 Versal ACAP 已囊括基本底層核心、工具鏈、編譯器和函式庫，

圖 3：Vitis 堆疊

資料來源：Xilinx 提供

其好處是：只要使用常規的設計工具、軟體、IP、中介軟體和框架，不論是有無電子工程基礎的軟、硬體工程師或資料科學家，都能輕鬆投入 AI 開發，針對軟、硬體進行編程與最佳化。為無縫運用各種開放原始碼的標準開發系統並組建環境，Xilinx 日前在既有 Vivado 設計套件之外，再發佈堆疊式統一軟體平台「Vitis」。

Vitis 旨在將硬體模組封裝成為「具軟體可調用」(software-callable) 功能，讓開發者得以專注於演算法，共有五層架構：1. 基

礎層為目標平台，由電路板與預編程 I/O 組成；2. 第二層為核心開發套件，用以管理不同領域之間的資料移動，包括開源的執行時間函式庫，以及編譯器、分析器與除錯器等核心開發工具；3. 第三層是在八個 Vitis 函式庫中提供逾 400 個最佳化開源應用，讓軟體開發者能使用標準應用程式介面 (API) 落實硬體加速；4. 第四層是 Vitis AI，整合了配置 Xilinx 硬體的領域專用架構 (DSA)，便於開發者套用 TensorFlow、Caffe 等框架。CTA

# COMPOTECHAsia 臉書

## 每週一、三、五與您分享精彩內容

<https://www.facebook.com/lookcompotech>