# 半導體創新，急如星火

■文：任茲萍

每次關於半導體的場合，總少不得對「摩爾定律」(Moore's Law)品頭論足一番；有人主張它已近窮途末路，更有人直接宣告它的消亡。事實究竟如何？今後又有哪些創新可能？

## 「摩爾定律」仍活躍，新製程須協同設計優化

照片人物：台積電副總黃漢森

已在 7nm 奪魁、正積極部署 3nm 製程的台積電 (TSMC) 斷言：「摩爾定律」本身就是一部創新史，至今依然活躍。副總黃漢森說明，標準的電池逆變器、高密度靜態隨機存取記憶體 (SRAM)、邏輯閘及微處理器 (MPU) 的電晶體密度皆仍循此軌跡前進；5nm 是目前效能最佳、密度最高的製程，且具備廣泛的 EUV( 極紫外線 ) 光罩層，設計生態系統也已就緒，惟量

產仍有風險存在。放眼未來，單一功能密度 ( 單一 IC 的元件數量 ) 和成本將是下世代技術的改善重點，而器件微縮 (Scaling) 是當前要務。技術進步將使新度量標準的使用成為可能。

基本上，技術節點 (node) 數值越小，晶片的集成密度就越高；但黃漢森強調，進入先進製程後，技術節點與閘極長度 (Gate Length) 不可混為一談——由於會有內部電場 ( 閘極與源極、汲極 ) 的互相干擾，電子波動特性甚至會開始主導電性，須考慮量子物理效應，導致電晶體閘極的物理特徵尺度大於節點數值，這在製程上是個棘手問題。因此，電晶體微縮也是一段創新歷程——常與摩爾定律相提並論的登納德縮放定律 (Dennard Scaling) 聚焦於能量需求將隨之減少，後經等量擴充 (Equivalent Scaling)，如今當道的鰭式場效電晶體 (FinFET) 和全耗盡型絕緣上覆矽 (FD-SOI) 是採通道幾何微縮 (Channel Geometry Scaling)。

新製程必須協同設計技術共同優化，以達成減少軌道高度、自我對準 (self-aligned) 接觸、單擴散 (Single diffusion break) 與最後閘極截止 (Gate-cut last) 等目標；當衡量電晶體效能與密度時，須留

意記憶體不足、非多核心晶片、沒有加速器，以及打線是否會延遲大晶片傳輸等問題。知名技術研究機構愛美科 (imec) 則特別關注能源與功耗，總裁暨執行長 Luc Vanden hove 博士表示，疾病、氣候變遷仍時刻威脅我們的生活，借助大數據可強化應變能力，但這對能耗是一大考驗，須透過設計標準找到最有效的回收方法，並優化每個子系統以降低對功率的需求。

## CEA-Leti 聚焦邊緣 AI，力推先進 FD-SOI

照片人物：CEA-Leti 執行長 Emmanuel Sabonnadière

與比利時 imec 和德國 Fraunhofer 並列全球三大技研領先者的「電子暨資訊技術實驗室」(CEA-Leti)，將目光放在邊緣人工智慧 (AI) 的先進節點。執行長 Emmanuel Sabonnadière 指出，

記憶體、設計、FD-SOI、感測器和軟體工具缺一不可；其中，28nm FD-SOI 每瓦運算能力達 2.9 TOPS/W，非常適合奈米加速器和深度卷積神經網路 (CNN)。平面 FD-SOI 早已用於類比電路設計，現將 FD-SOI 與 3D 和嵌入式記憶體結合，可為 AI 建置效率電路。相較於 FinFET，FD-SOI 可動態改變邏輯電路的工作點位，在設計階段就能實現低功耗、高效能。

當神經網路根據最終用戶所接受的新數據推斷事物時，AI 推論 (Inference) 需要緊湊且省電的電路。先進 FD-SOI、3D 集成和非揮發性記憶體 (NVM) 的結合將為專用電路另闢蹊徑，可在分佈式電子產品的有限功率預算內顯著提高性能，且讓器件更輕薄、密度更高、電晶體通道的電子遷移率更好，反應更靈敏；意法半導體 (ST) 有兩款晶片已採用此技術。CEA-Leti 是 FD-SOI 技術的始祖，並於 1992 年協助成立矽絕緣研究的領導廠商 Soitec；FD-SOI 技術現已被集成到數百萬台控制台和智慧手機中，讓應用程式以極低的能耗進行高性能處理。

CEA-Leti 已對外揭示 12nm 及更高製程的先進 FD-SOI 藍圖，現正與頂級半導體公司討論尋求新型移動和汽車應用。Sabonnadière 大膽預測，FD-SOI 未來可能會成為需要高能效處理之互聯汽車市場的標準配置。與此同時，可利用類比增壓器 (Analogue Booster) 的基體偏壓 (Body Bias) 改善傳統類比設計，藉由強化／弱化電晶體取得

功耗電壓控制震盪器／低雜訊放大器 (VCO/LAN)，以補償電晶體的不匹配，其目的是：獨立設計並減少多個運行點 (running-point) 的應用面積，以便多爭取 30 ~ 50% 的可用空間。

### 3D 整合 + AI 深度學習平台，讓邊緣設備更聰明

從 FD-SOI 延伸而來的「CoolCube」單片三維 (monolithic 3D) 整合專利則是提升密度和連接性的秘技，可維持反向偏壓 (back bias)、在中間置入新的互連層以緩解路由壅塞，且只要裝置的型態與架構相同，頂端和底部層可以是異質結構。新的嵌入式記憶體亦可與 FD-SOI 整合以擴大應用，包括：微控制器 (MCU)、應用資安及邊緣 AI 皆適用。受惠於新興可變電阻式記憶體 (RRAM)，功耗更具優勢；另一項以脈衝編碼 (Spike-coding) 的深度神經網路 (DNN)，乃專為極低功耗系統而生，例如：以 RRAM 等 NVM 製作大量平行突觸 (synaptic) 的記憶體。

簡單、效率且容量可調為其特點，主要供類比運算之用，聰明的

Retina 即是使用此類 3D 堆疊，好處包括：可使用低頻處理器、直接互連像素、處理迅速，最重要的是：它擁有百倍運算力、十倍能源效率，且處理延遲極低；可完美縮放，不會因為礙於頻寬而有尺寸限制，可做「異質整合」(Heterogeneous Integration, HI)。例如，應對感測器內置複雜處理，尤其適合重隱私的感測應用；每個像素可獨立處理，結合經典電腦視覺和 AI 演算法可拓展新的應用範圍。CEA-Leti 還展示邊緣 AI 深度學習平台「N2D2」，存取資料庫容易，十分有利神經網路的學習探勘。

其次，「N2D2」內建轉出模組，可在不同硬體自動產生編碼——為 CPU、GPU、FPGA 等商用現貨 (COTS) 元件獨立產生編碼，且能符合特定大廠的硬體規範；Sabonnadière 認為，這是邊緣 AI 必備的剛性需求。該平台設有多重比較準則，可對延遲性、硬體成本、記憶體需求及功耗做綜合評估，且方便使用者做資料整備和半自動資料標記，對資料庫處理／預處理助益良多。再者，基於 CEA IP 的 NN 硬體加速器類似編碼作用，能在導入階段協助決策。

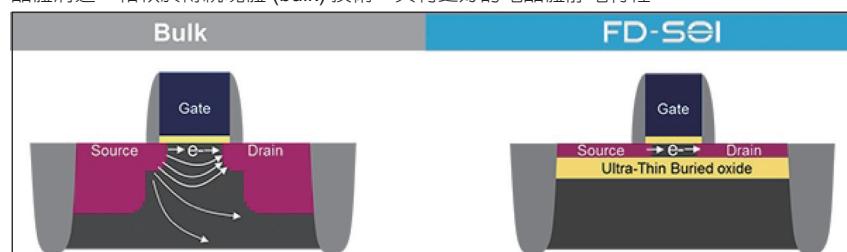

圖說：FD-SOI 將超薄絕緣體層 (埋入式氧化物) 放置在矽基的頂部，藉由超薄矽膜產生電晶體溝道；相較於傳統塊體 (bulk) 技術，具有更好的電晶體靜電特性

資料來源：意法半導體：[https://www.st.com/content/st\\_com/en/about/innovation---technology/FD-SOI/learn-more-about-fd-soi.html](https://www.st.com/content/st_com/en/about/innovation---technology/FD-SOI/learn-more-about-fd-soi.html)

最後，一個值得推敲的思惟是：業界該如何蓄積創新能量？

## 下世代微電子氣候漸成，亟需產官學研通力合作

照片人物：新加坡國立研究基金會總裁劉德成教授

新加坡國立研究基金會總裁劉德成教授分享他們的創新經驗：新加坡向來將研發視為對未來的投資，每年編列的企業研發創新( RIE )預算約佔 1% 國民生產毛額(GDP)，旨在建立產業技術深度和能力、開拓產業視野、檢視產業並創造市場，由政府擔任火車頭角色，藉此吸引更多私人研發投資以建立活躍的生態系，收到外溢效果；政府亦會出面與民間企業共同成立聯營企業 (consortia)，以強化公部門與私有研發資源的連結。上述措施已獲具體成果，不僅境內創投社群動力十足，也讓新加坡對整個半導體價值鏈的影響力非比尋常。

具體展現在：其所屬產業成員對其 GDP 貢獻超過 7%，且囊括 11% 的全球半導體市場，有

照片人物(左起)：工業技術研究院副院長張培仁、新竹市長林智堅、SEMI 全球總裁暨執行長 Ajit Manocha

逾 60 家的半導體公司皆群聚於此。劉德成預見下世代微電子重心在於：物聯網 (IoT) 及連接、軟性／混合電子、仿神經型態運算 (Neuromorphic Computing) 的新興記憶體器件、矽光子與先進電子材料研究。此外，「異質整合」將促成輕量、低成本和微型化，而初見苗頭的量子運算 (Quantum Computing)、感測與網路可望再度改寫歷史，例如：提供安全量子密鑰傳輸 (QKD)、利用量子時脈相關性實現更高的感測或解析度、將量子資訊單獨傳輸確保通訊安全等。

上述領域需要對基礎物理、化學、材料科學和設備支出的基礎知識有多方了解。台灣產業的重要推手工業技術研究院 (ITRI)，不僅是負責協調產、官、學發展技術／產品／服務的區域創新中心，也是孕育逾 140 家高科技公司執行長的搖籃。副院長彭裕民闡述，緊扣永續環境、創造低碳、節能、循環社區使命，ITRI 已針對 5G 整合測

試、無人車駕駛測試、智慧製造試產、微電網系統驗證、3D 列印醫療設備製造基地建立營運認證及驗證據點，且成果豐碩。日前更攜手國際半導體產業協會 (SEMI) 和新竹市政府打造亞洲第一自駕車開放場域試驗平台。

半導體晶片是驅動車用精密零件往智能化升級的研發關鍵，舉凡 GPS 地圖、地形感測、記憶體中的精密零件與電子系統都需要成熟的半導體技術作為後盾，而開放式場域測試才是真正自駕車挑戰的開始，如何做好感測及決策控制將是自駕車核心技術。順帶一提，SEMI 著眼於車用半導體的龐大市場潛能，成立全球車用電子諮詢委員會 (SEMI GAAC)，奧迪 (Audi) 即是創始會員之一。另一方面，ITRI 從產業需求出發的「AI-on-Chip 計畫」，冀能降低 10% 的一次性工程費用 (NRE)、發展不可或缺的 IP、縮短 25% 晶片軟體開發時間並提供兩倍 AI 晶片效能。 CTA