學子專區—ADALM2000實驗:TTL逆變器和NAND閘

前言:

作者:ADI 系統應用工程師Antoniu Miclaus和顧問研究員 Doug Mercer

目標

自20世紀60年代首次生產出整合邏輯閘以來,各種數位邏輯電路技術層出不窮。本次實驗將研究電晶體-電晶體邏輯(TTL)電路逆變器(反閘)和2輸入NAND閘配置。

背景知識

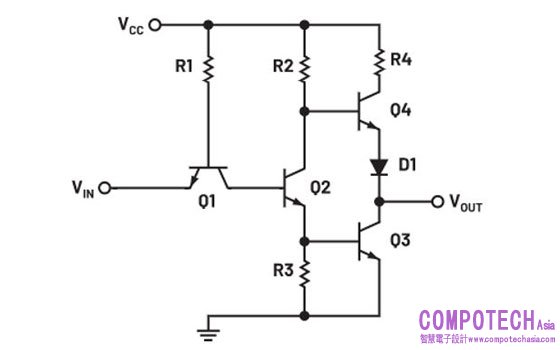

TTL逆變器的原理圖如圖1所示。此電路克服了單晶體管逆變器電路的侷限性。基本TTL逆變器由三級組成:電流導引輸入、分相級和輸出驅動級。

圖1. TTL逆變器

輸入級電晶體Q1執行電流導引功能,可以將其視為背靠背二極體佈置。電晶體以正向或反向模式工作,使電流流入或流出第二級電晶體的基極Q2。正向電流增益ßF遠大於反向電流增益ßR。關斷時,其提供更高的放電電流來為基極放電。

圖2. 輸入電流導引級的等效電路

圖1中的第二級電晶體Q2使用分相器來驅動上拉和下拉輸出級的兩半。其允許以相反相位產生輸入條件,從而可以反相驅動輸出電晶體。如此Q4關斷時Q3可以導通,反之亦然,如圖3所示。

圖3. 分相級

輸出電晶體對Q3和Q4與二極體D1一起被稱為圖騰柱輸出,如圖4所示。此種輸出配置提供了主動拉電流或灌電流的能力,對於驅動容性負載很有用。電阻R4用於限制VCC提供的電流。在穩態條件下,一次只有一個電晶體導通。

圖4. 輸出級

二極體D1用於提高Q4的有效導通電壓,使其能夠在Q3完全導通之前關斷。這有助於防止邏輯狀態轉換期間潛在的大湧浪電流流入輸出級。電阻R4並用於限制輸出級中允許流動的電流。缺點是邏輯高位準會降低,降幅為二極體壓降,如圖11所示。

材料

• ADALM2000 主動學習模組

• 無焊試驗板

• 跳線

• 一個100 kΩ電阻

• 一個2.2 kΩ電阻

• 一個470 Ω電阻

• 一個100 Ω電阻

• 一個小訊號二極體(1N914)

• 五個小訊號NPN電晶體(2N3904和/或SSM2212)

TTL逆變器

說明

ADALP2000 類比零件套件隨附五個2N3904 NPN電晶體。較舊的套件可能包含一對匹配的SSM2212。所示的建議試驗板佈局是針對SSM2212連接。如果只使用2N3904元件,請根據需要更改佈局。

在無焊試驗板上建構圖5所示TTL逆變器電路。如果使用SSM2212 NPN對,其只能取代Q3和Q4(輸出級),因為其基極和發射極端子上有內部保護二極體用以防止反向偏置。

圖5. TTL逆變器

硬體設定

將電路連接到ADALM2000輸入/輸出連接器,如圖5所示。對於未使用的示波器負輸入,在不使用時最好將其接地。

試驗板連接如圖6所示。

圖6. TTL逆變器試驗板電路

程式步驟

將波形產生器W1配置為具有0 V偏移和6 V幅度峰對峰值的100 Hz三角波。在x-y模式下使用示波器觀察電路的電壓傳輸曲線。

圖7. TTL逆變器傳輸曲線

TTL NAND閘

說明

為TTL逆變器再增加一個輸入,便得到一個TTL NAND閘。按照圖8所示連接TTL逆變器電路。

圖8. TTL 2輸入NAND門

硬體設定

將電路連接到ADALM2000 I/O連接器,如圖8所示。對於未使用的示波器負輸入,在不使用時最好將其接地。

試驗板連接如圖9所示。

圖9. TTL 2輸入NAND門試驗板電路

程式步驟

將波形產生器W1配置為具有0 V偏移和6 V幅度峰對峰值的100 Hz三角波,將W2配置為具有0 V偏移、6 V幅度峰對峰值和90°相位的100 Hz三角波。

使用示波器觀察電路的輸出Ch2。

圖10. TTL NAND門輸出波形

測量

傳輸特性

透過施加緩慢上升的輸入電壓,並確定相對於每個電晶體的導通狀態變化而發生的事件序列以及這些變化發生的臨界點,可以推導出TTL逆變器的傳輸特性。考慮圖11所示的電路輸入與輸出傳輸特性曲線。

圖11. TTL逆變器輸入與輸出傳輸曲線

中斷點P1

當輸入接近0 V且基極電流提供給Q1時,該電晶體可以在正向模式下導通。集電極電流的唯一來源是Q2的漏電流,因此Q1將被驅動到飽和狀態。此動作確保了Q2關斷,進而又表示Q3關斷。在沒有負載的情況下,輸出級中有漏電流流動,使得電晶體Q4和二極體D1在導通狀態下幾乎不傳導電流。

VOUT = VCC – VBE4 – VD1

VOUT = 5 V – 0.6 V – 0.6 V = 3.8 V

P1點:VIN = 0.5 V,VOUT = 3.8 V

中斷點P2

隨著輸入電壓略微增加,上述狀態一直持續,直到(在Q1導通並處於飽和狀態的情況下)Q2基極的電壓上升至導通點。則

VIN = VBE2 – VCE1(SAT) = 0.6 V – 0.1 V = 0.5 V

P2點:VIN = 0.5 V,VOUT = 3.8 V

中斷點P3

隨著輸入電壓進一步增加,Q2傳導更多電流,從而完全導通。Q2的基極電流由Q1的基極-集電極結(現在是正向偏置)提供,Q1仍處於飽和狀態。最終,Q3達到導通點。此發生於:

VIN = VBE2 + VBE3 – VCE1(SAT)

VIN = 0.7 V + 0.6 V – 0.1 V = 1.2 V

請注意,當電晶體Q3剛剛導通時,VBE3 = 0.6 V,表示流過R3的電流為0.6 V/470 Ω = 1.27 mA。在線性活動區工作時,Q2的集電極電流為0.97 mA × 1.27 mA = 1.23 mA。

R2兩端的電壓降即為VR2 = 1.23 mA × 2.2 kΩ = 2.7 V。

在此種情況下,Q2上的集電極到發射極電壓降為:

VCE2 = VCC – VR2 – VR3

VCE2 = 5 V – 2.7 V – 0.6 V = 1.7 V

此證實了Q2仍在正向活動模式下運行。

隨著Q3開始導通,電流通過Q4和二極體D1的傳導路徑,隨後完全導通。此種情況下:

VO = VCC – VR1 – VBE4 – VD1

VO = 5 V – 0.94 V – 0.65 V – 0.6 V = 2.81 V

P3點:V = 1.2 V,V = 2.81 V

中斷點P4

隨著輸入電壓進一步增加,Q2傳導更多電流,最終進入飽和模式。Q3也傳導更多電流,最終達到飽和點。當Q2傳導更多電流時,其集電極電流增加。此導致R1兩端的壓降增加,表示Q2上的電壓(即VCE2)下降。當此電壓降至Q4和二極體D1導通所要求的電壓以下時,二者均關斷,然後Q3飽和。

當Q3達到飽和邊緣時:

VI = VBE2 + VBE3 – VCE1

VI = 0.7 V + 0.7 V – 0.1 V = 1.3 V

P4點:VI = 1.4 V,VO = 0.2 V

問題:

1. 典型TTL邏輯閘的輸出電路通常被稱為圖騰柱輸出,原因是其兩個輸出電晶體相互堆疊,就像圖騰柱上的雕像一樣。具有圖騰柱輸出級的門電路能否提供負載電流、吸收負載電流或既能提供又能吸收負載電流?

答案請見 學子專區 部落格。