介紹

嵌入式系統設計人員發現自己在設計限制、效能期望、排程以及預算問題的考量之間交戰。確實,甚至是充滿矛盾的現代專案管理口號和詞彙,都進一步凸顯此角色焦慮不安的本質:「快速故障」;「靈活敏捷」;「永不過時」及「具有破壞性」!即便嘗試滿足這些期望所用的技法,可能相當折磨人,但是整個市場都在談論,並且不斷強調其重要性。我們需要的是一種設計方法,能實作不斷進化的迭代程序,而且如同多數的嵌入式系統一樣,都得從硬體架構開始。

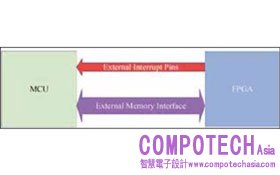

輔助處理器架構是一種硬體架構,以微控制器 (MCU) 和現場可編程閘陣列 (FPGA) 技術的合併優勢而著稱,並且可為嵌入式設計人員提供一個流程,讓他們滿足甚至最嚴苛的要求,同時仍具備必要的彈性,以因應已知和未知的挑戰。使用具備迭代調適能力的硬體,設計人員便能展示進度、達到關鍵里程碑,並完全發揮快速原型開發流程的優勢。

圖 1:一般性輔助處理器示意圖 (MCU + FPGA)。