萊迪思半導體(Lattice)亞太區現場技術支援總監蒲小雙

工業物聯網、5G技術演進將大量設備引入數位資訊系統,感測裝置不停將搜集到的資料透過各種路徑傳遞到資料中心或雲端,為節約有限的網路資源,邊緣計算概念被提出來,經過預處理的資料,將節約大量頻寬資源,提升自動處理的效率。

萊迪思半導體(Lattice)亞太區現場技術支援總監蒲小雙指出,不同產業的開發人員皆在尋求為網路邊緣應用添加處理和互連功能。快速發展的網路邊緣設備市場在要求更高性能和可靠性的同時,希望設備具有低功耗和小尺寸的特性。

越來越多新元件需要採用支援PCIe和千兆乙太網路等常見介面的低功耗處理硬體,這使得新一代FPGA器件需要在連接、計算和小型化方面提供多元化的能力。比如,在極小的尺寸上實現PCIe到SGMII橋接,通過PCIe Gen2將處理器橋接到多個控制外設(UART、SPI、I2C、MDIO等介面),亦或是作為輔助處理器分擔主CPU的計算負載等等。

Certus-NX FPGA擁有低功耗、小尺寸、高可靠性和瞬時啟動等特性

設備開發人員更需要易於使用、具備單一來源的開發平臺,為他們提供能快速推出產品所需的硬體、軟體和IP。

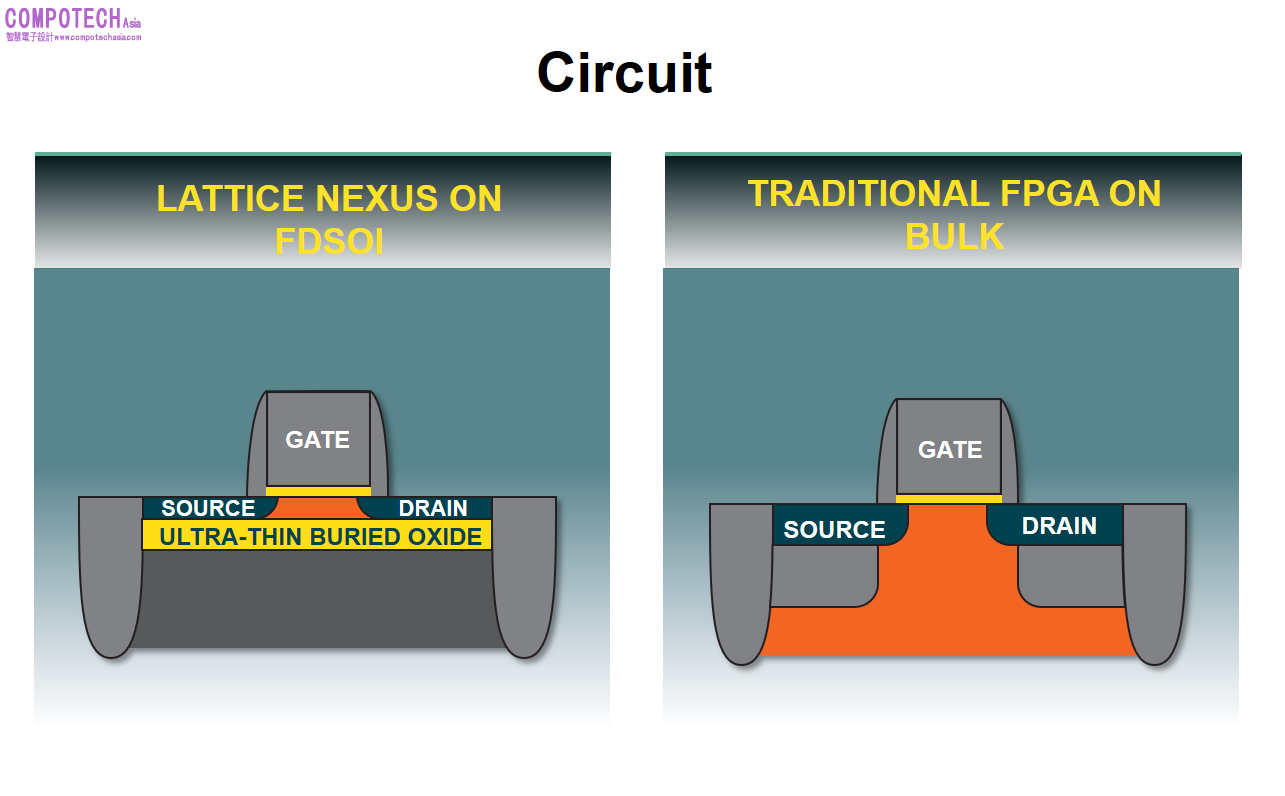

Lattice Certus™-NX系列FPGA擁有低功耗、小尺寸、高可靠性和瞬時啟動等特性,且支援高速PCIe和千兆乙太網路介面,可實現資料協同處理、訊號橋接和系統控制。適用於從自動化工業設備中的資料處理到通訊基礎設施中的系統管理等。 在通用型FPGA市場上,Certus™-NX系列FPG每平方毫米I/O密度最高可達同類型FPGA競品的兩倍,是業界首個基於28 nm FD-SOI製程技術的低功耗FPGA技術平臺。與傳統bulk CMOS製程相比,新製程更好地滿足功耗和散熱管理需求,可將功耗最多降低75%!這不僅有助於降低電池供電的網路邊緣設備的功耗,還能降低工業和資料中心等應用的電力成本。

借助先進的制程,新一代Certus™-NX系列FPG晶片的軟錯誤率(SER)效能達比同類型FPGA的降低100多倍,能夠滿足工業和汽車市場的苛刻應用需求。

圖:採用FD-SOI製程技術的關鍵區域(橙色)大大減少,針對軟錯誤率(SER)的可靠性提高100倍

圖片來源:lattice

Certus-NX FPGA除了可以在36平方毫米內實現完整的PCIe解決方案之外,還可使用1.5 Gbps差分(differential)I/O, 5 Gbps PCIe、1.5 Gbps SGMII和1066 Mbps DDR3多個IP模組,讓設計人員快速搭建起目標應用介面。此外,新產品還支援AES-256加密和ECDSA認證,避免未經授權的造訪/更改/複製行為,借助SPI記憶體,系統完成單個I/O配置只需3 ms,典型應用中的整個元件啟動時間僅需8-14 ms即可完成。

蒲小雙表示,Certus-NX是第二款基於萊迪思Nexus FPGA技術平台的產品,其提供平行處理效能和靈活I/O支援的完美結合,可實現創新的元件設計,重新定義低功耗通用型FPGA,藉由Lattice Nexus開發平臺在系統、架構和電路層面的創新,為開發人員在評估應用效能和功耗需求時提供更多選擇方案。