IC 年屆花甲,EDA 邁向新紀元——AI 運算、領域特定架構、高階合成、數據自動數位化,同步發功

前言:

IC60流光溢彩2:IC 設計固本培元

年屆花甲的 IC 產業,是否已邁入「高原期」、難以再創高峰?其他電子設計自動化 (EDA) 的老將新兵又怎麼看待半導體產業的未來?曾是台灣本土 EDA 廠商代表、現轉往音訊領域開疆闢土的先進期許業界:在花了一甲子奠定「大山頭」後,要站在新的制高點為建立下個更大的山頭而努力;去年成為西門子 (Siemens) 一員的明導國際 (Mentor Graphics),再度為「領域特定架構」(Domain Specific Architecture) &「高階合成工具」(High-Level Synthesis, HLS) 背書;另一家新創企業富比庫 (FootPrintKu) 則試圖運用新的觀念與技術,帶領產業做變革。

EDA 是半導體業根基,SoC 與 UI 是主幹

富迪科技 (Fortemedia) 董事長暨執行長黃炎松博士日前在《IC 60大師論壇》細數,聚焦電子設計的電腦軟體濫觴可追溯至 1970 年代做電晶體分析的 SPICE 和用於佈局 (layout) 的電腦輔助設計 (CAD),隨後 1980 年代因 IC 體積變大,開始推廣電腦輔助工程 (CAE),而 EDA 一詞直到 1985 年左右才出現。他以大樹比喻半導體產業生態的「生生不息」,樹根有兩大支脈:一是封裝、光罩等製造,二是 EDA 工具;樹枝是衍生出的電腦、通訊、手機、穿戴裝置與物聯網 (IoT) 等諸多應用;而單晶片 (SoC) 和使用者介面 (UI) 則是支撐整顆大樹的主幹。

富迪科技 (Fortemedia) 董事長暨執行長黃炎松博士日前在《IC 60大師論壇》細數,聚焦電子設計的電腦軟體濫觴可追溯至 1970 年代做電晶體分析的 SPICE 和用於佈局 (layout) 的電腦輔助設計 (CAD),隨後 1980 年代因 IC 體積變大,開始推廣電腦輔助工程 (CAE),而 EDA 一詞直到 1985 年左右才出現。他以大樹比喻半導體產業生態的「生生不息」,樹根有兩大支脈:一是封裝、光罩等製造,二是 EDA 工具;樹枝是衍生出的電腦、通訊、手機、穿戴裝置與物聯網 (IoT) 等諸多應用;而單晶片 (SoC) 和使用者介面 (UI) 則是支撐整顆大樹的主幹。

照片人物:富迪科技董事長暨執行長黃炎松博士

黃炎松認為,EDA 必須以「平方」的速率成長,才能追上摩爾定律 (Moore's law) 的腳步——電晶體數量每 18 個月就加倍,因應不斷推陳出新的 IC 設計規格;雖然各家廠商竭力從演算法創新、方法論 (methodology) 及平行運算改進,可惜,需求缺口仍不斷擴大。此外,工程專業亦是一大挑戰——若對眼下工程真的毫無所悉,是無法寫出「測試案例」的;偏偏未知範疇越來越廣,傳統電腦架構實有改弦易轍、導入人工智慧 (AI) 的必要。近幾年他觀察到,AI 運算能力是每百天就加倍!而內嵌思考與感官能力的 HOC (Head on Chip) 可能是 SOC 接班人。

「當感測晶片擁有完整的眼、耳、鼻、舌、身、意,之後再連到 AI 晶片,即成 HOC 智能感測器」,黃炎松解釋。往上方應用層能與虛擬實境/擴增實境 (VR/AR)、無人機或機器人對接,若再與精密機械合作,台灣 IC 產業潛力無窮、商機可百倍於今日,邊緣設備 (Edge) 的 IC 設計尤為看俏,而台灣獨霸全球的晶圓代工對此助力甚大,EDA 亦將隨之成長且必將加入 AI 元素。與此同時,「聲音」已是使用者介面的主要選項之一,這也是黃炎松自述離開 EDA 業界、轉而創辦富迪科技,傾力發展小型陣列麥克風 (Small Array Microphone, SAM) 的動機。

深化應用+製程創新,矽電晶體再行廿年大運

Mentor 總裁暨執行長 Walden C. Rhines 亦預計 IC 設計將更趨活躍,且認同當中內涵正在發生質變:「領域特定架構」應蘊而生!若以 2012 年迄今的全球無晶圓廠創投基金為參考指標,由 AI 與機器學習 (Machine Learning) 以 11.63 億美元的絕對優勢居冠,加密貨幣與 5G 高速通訊分別以 4.65 億美元和 3.01 億美元位居二、三名。單是今年以來,AI 及深度學習 (Deep Learning) 的投資就達 7.86 億美元,由 14 家無晶圓新創 AI 公司分食;目前投入相關控制晶片的開發商,多以視覺/臉部辨識為主,其次為資料中心/雲端 AI/高效運算 (HPC)。

Mentor 總裁暨執行長 Walden C. Rhines 亦預計 IC 設計將更趨活躍,且認同當中內涵正在發生質變:「領域特定架構」應蘊而生!若以 2012 年迄今的全球無晶圓廠創投基金為參考指標,由 AI 與機器學習 (Machine Learning) 以 11.63 億美元的絕對優勢居冠,加密貨幣與 5G 高速通訊分別以 4.65 億美元和 3.01 億美元位居二、三名。單是今年以來,AI 及深度學習 (Deep Learning) 的投資就達 7.86 億美元,由 14 家無晶圓新創 AI 公司分食;目前投入相關控制晶片的開發商,多以視覺/臉部辨識為主,其次為資料中心/雲端 AI/高效運算 (HPC)。

照片人物:Mentor 總裁暨執行長 Walden C. Rhines

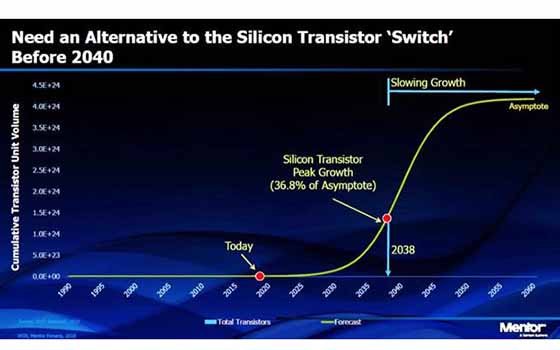

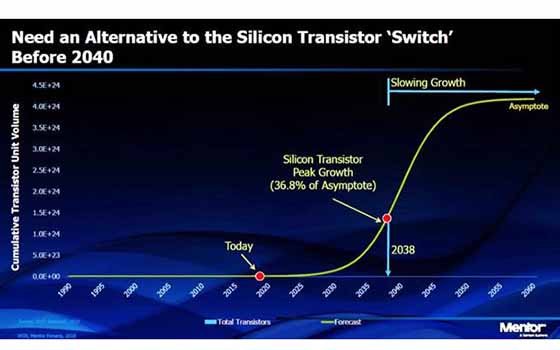

Rhines 再度搬出最愛的「岡波茨曲線」(Gompertz Curve) 論述:這個於 1825 年提出,廣泛用於預測人口成長、手機普及與財務影響的模型告訴我們,以時間序列為函數,最大成長率約落在 36.8%。以此推估,矽電晶體製程的「效用極限」將在 2038 年觸頂;有鑑於此,最遲須在 2040 年之前完成製程轉換,才能避免半導體步向衰退。在此迫切需求帶動下,Rhines 展望今後 EDA 市場將持續暢旺,動能來自於五方面:IC 本身的演進、非半導體企業的新入、創投基金的挹注、研發支出的提高,以及專用晶片 (ASIC) 的蓬勃。

圖1:以「岡波茨曲線」(Gompertz Curve) 預測半導體產業走勢

資料來源:VLSI Research (2016)

資料來源:VLSI Research (2016)

政策護航,中國大陸 IC 設計大爆發

Rhines 回顧近十年半導體產業演變歷程,IC 的年複合成長率 (CAGR) 約 3%,整體成長率有 22%,去年整體產業營收更見突然加速跡象;多項業界合併看來並未產生太大衝擊,反見 IC 研發支出不斷上揚,2017 年即增加 9.8%。再者,無晶圓廠半導體的創業投資日漸增多,中國大陸的來勢洶洶尤其值得關注——當地無晶圓廠投資於今年第二季首度超越美國,且矢志從製造轉型「設計」意圖明顯;中國大陸「國家集成電路產業投資基金」(簡稱「大基金」) 從 2014 年首發的 200 億美元、增至今年的 470 億美元,且另有 474 億美元的新基金正蓄勢待發。

Rhines 回顧近十年半導體產業演變歷程,IC 的年複合成長率 (CAGR) 約 3%,整體成長率有 22%,去年整體產業營收更見突然加速跡象;多項業界合併看來並未產生太大衝擊,反見 IC 研發支出不斷上揚,2017 年即增加 9.8%。再者,無晶圓廠半導體的創業投資日漸增多,中國大陸的來勢洶洶尤其值得關注——當地無晶圓廠投資於今年第二季首度超越美國,且矢志從製造轉型「設計」意圖明顯;中國大陸「國家集成電路產業投資基金」(簡稱「大基金」) 從 2014 年首發的 200 億美元、增至今年的 470 億美元,且另有 474 億美元的新基金正蓄勢待發。

受到政府大力支持激勵,去年中國大陸 IC 設計公司已達 1,380 家,其中,功率、類比、微機電 (MEMS)/感測器、晶圓廠和射頻 (RF) 裝置是前五大分眾應用。企業規模也有所擴增,現以 100~500 人為大宗。另一方面,谷歌 (Google)、亞馬遜 (Amazon) 和臉書 (Facebook) 開始製造自有晶片,特斯拉 (Tesla) 捨通用型 GPU 而改用專為自動駕駛系統訂製的處理器,博世 (Bosch) 甚至乾脆斥資 10 億歐元新設自有晶圓廠……。這些標誌性事件皆意味著:有越來越多企業將涉足「半導體設計」領域;惟隨著 AI 抬頭,須重新省思 IC 設計邏輯。

圖2:中國大陸無晶圓廠 IC 設計公司之分眾市場概況

資料來源:Mentor analysis (2018/07)

瞄準終端應用,「領域特定架構」厚積薄發

Rhines 說明,若以軟體為中心,現代被編譯過的腳本語言 (Scripting language) 雖具編程效率、有利於動態類型及重複使用,卻可能在執行時遭遇麻煩。反之,以硬體為中心的好處是:依循領域特定架構、只需少數工序就能運作地很好。那麼,何不兼取兩者之長——瞄準終端應用,發展「領域特定架構」。他坦言,早在 1980 年代就曾喧騰一時的 AI,正是因為當時網路/物聯網環境未成熟、缺乏可分析的大數據,加上傳統電腦晶片運算力有限、無法載入先進演算法以及無可變現的殺手級應用加持,才未能一躍而起。

Rhines 說明,若以軟體為中心,現代被編譯過的腳本語言 (Scripting language) 雖具編程效率、有利於動態類型及重複使用,卻可能在執行時遭遇麻煩。反之,以硬體為中心的好處是:依循領域特定架構、只需少數工序就能運作地很好。那麼,何不兼取兩者之長——瞄準終端應用,發展「領域特定架構」。他坦言,早在 1980 年代就曾喧騰一時的 AI,正是因為當時網路/物聯網環境未成熟、缺乏可分析的大數據,加上傳統電腦晶片運算力有限、無法載入先進演算法以及無可變現的殺手級應用加持,才未能一躍而起。

他強調,典型電腦架構的運算力雖然不斷精進,卻不適用於臉部/語音辨識等需要大幅縮短工作週期的 AI 平行運算;只有引進「領域特定架構」概念,上述問題方可迎刃而解。一家名為 Emoshape 的公司,更推出號稱全球首款內建情緒合成 (Emotion Synthesis) 引擎的「情緒處理單元」(Emotion Processing Unit, EPU),預估在電腦遊戲、虛擬實境 (VR)/擴增實境 (AR) 深具潛力;微軟 (Microsoft) 亦為混合實境 (MR) 裝置 HoloLens 開發客製化的深度神經網路晶片。這些「領域特定架構」同樣需要設計工具的與時俱進。

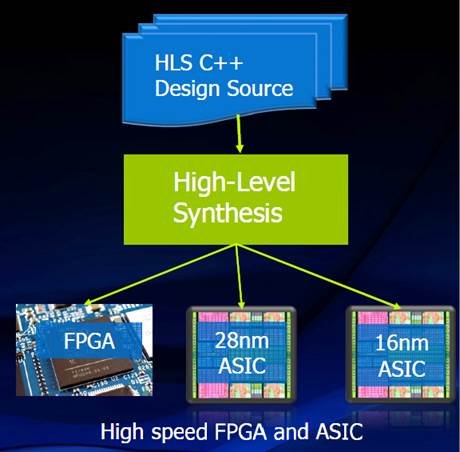

「高階合成」易於轉換不同製程,探索所有設計可能

Rhines 主張,EDA 在原有萃取 (Abstraction) 與功率分析功能之外,還須向下個階層延伸、形塑「高階合成」。他歸納 HLS 擁有四大利益:1.加速產品上市並確保產出品質;2.可借用 FPGA 為單晶片 (SoC) 或 ASIC 預做原型設計;3.允許延後變更規格;4.減少驗證及除錯成本,特別適合電腦視覺/神經運算、高頻寬/蜂巢式通訊,以及影像處理/視訊/壓縮等應用。實證發現,相較於手工的 VHDL、Verilog 等暫存器傳遞語言 (RTL),可節省四倍以上時間!HLS C++ 一脈相承,可套用在多種不同的製程技術上,且非常容易轉換,大幅降低工程複雜度。

Rhines 主張,EDA 在原有萃取 (Abstraction) 與功率分析功能之外,還須向下個階層延伸、形塑「高階合成」。他歸納 HLS 擁有四大利益:1.加速產品上市並確保產出品質;2.可借用 FPGA 為單晶片 (SoC) 或 ASIC 預做原型設計;3.允許延後變更規格;4.減少驗證及除錯成本,特別適合電腦視覺/神經運算、高頻寬/蜂巢式通訊,以及影像處理/視訊/壓縮等應用。實證發現,相較於手工的 VHDL、Verilog 等暫存器傳遞語言 (RTL),可節省四倍以上時間!HLS C++ 一脈相承,可套用在多種不同的製程技術上,且非常容易轉換,大幅降低工程複雜度。

圖3:HLS 拉近高速 FPGA 和 ASIC 的設計差距

資料來源:Mentor 提供

如此一來,便於讓開發人員迅速探索所有可能的設計方案,進而決定最適合執行者,且可省下昂貴的遷移成本輝達 (NVIDIA) 便因此改進 50% 設計生產力,並節約 80% 驗證成本。猶記多年前眾家 EDA 廠商初倡 HLS 之際,業界就有人提及學習曲線及「與 RTL 流程整合」是關鍵;經過這些時間的努力,似乎見到打開市場的契機。Mentor 亞太區技術總監李立基補充,IC 設計從最初的原理圖到硬體 Verilog,再到如今的 C 合成,是 Methodology 的根本變革 (Revolution) 而非漸次演進 (Evolution),工程師必須改變思維以適應新的設計。

Data is King,但分享vs.保密得謹慎拿捏

李立基還提到,數據一直是 AI 的動力來源,但如何在資料分享與保密之間取得平衡很重要,利用標準設計平台、拉近使用工具差異或是折衷方式。基本上,Mentor 也同意雲端化趨勢,而安全與使用費用是使用者的兩大考量;但李立基評估,雲端僅適合作為短期靈活使用,若是整個專案都使用雲端計價未必較划算。另西門子繼收購 Mentor 後,去年再宣佈將機器學習軟體商 Solido 納入旗下,可望借助集團資源強化變異感知設計與特徵化模擬能力,擴展 Mentor 的模擬/混合訊號 (AMS) 驗證產品組合。

李立基還提到,數據一直是 AI 的動力來源,但如何在資料分享與保密之間取得平衡很重要,利用標準設計平台、拉近使用工具差異或是折衷方式。基本上,Mentor 也同意雲端化趨勢,而安全與使用費用是使用者的兩大考量;但李立基評估,雲端僅適合作為短期靈活使用,若是整個專案都使用雲端計價未必較划算。另西門子繼收購 Mentor 後,去年再宣佈將機器學習軟體商 Solido 納入旗下,可望借助集團資源強化變異感知設計與特徵化模擬能力,擴展 Mentor 的模擬/混合訊號 (AMS) 驗證產品組合。

談到數據,Rhines 指出,西門子原本即能讓用戶存取所需資料,類似的理念用在 IC 設計上,對於逆向控管產出品質有加分作用;而 2015 年新成立富比庫公司,正是致力於研發 EDA Library 自動建置與驗證引擎的軟體商。創辦人暨執行長黃以建表示,電子業有被世人視為傳統產業之象;EDA 雖然每年都有新產品推出,但在設計及製造流程上,過去數十年其實沒有太大改變。上游元器件製造商所輸出的規格書 (Data Sheet) 是 PDF 檔,到了系統廠或 EDA 廠商手上須做大量人工輸入,才能著手生產;且一有新的元件問市,每一家都得重複動作。

照片人物:富比庫創辦人暨執行長黃以建

Auto Digitization,協助 EDA 專業知識傳承

體認到這個痛點,富比庫善用自動化和 AI 科技首創 EDA 雲端平台,藉由虛擬機器人將這些資料數位化、整合進現今主流 EDA 軟體,為下游製造商分擔冗餘工作,有助於提升效率並避免錯誤。這個稱為「Auto Digitization」(自動數位化) 的程序,可為產業解決四大困境:1.EDA 專業知識傳承不易,培訓成本過高,一旦人員流動又得重頭來過;2.建置零件耗時費工,影響工作效率,偏偏這是後續系統模擬的必備前置作業;3.檔案繁複、零件瑣碎,單是「命名」就是一大學問,造成資料控管困難;4.人力不足,且容易侷限員工的工作發展及學習空間。

富比庫的願景是:聯合業界催生「電子零件格式標準化」——1.描述電子零件實體與焊盤圖案 (land pattern) 資訊;2.定義電路板零件、線路符號和 3D 模型之特徵;3.建立資料標準格式、描述建置規則與命名架構。著眼於台灣在半導體設計、製造及下游終端生產不乏全球知名的標竿企業,生態資源豐富,黃以建相當看好本地發展前景。智慧化所及,有意推行「標準化」、「產業平台」的籌謀亦時有所聞;不過,礙於被複製、剽竊或駭入的風險顧慮,致使有些資料分享計畫終究未能成事。或許,越是上游的產業、資料開放程度越高,勝算相對更大。