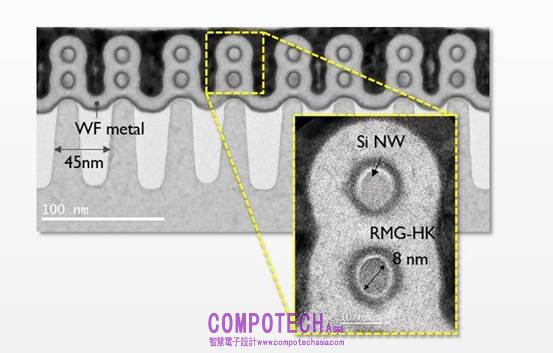

2016年6月17日--奈米電子研究中心IMEC在VLSI研討會上,,展示了環繞式極匣的n與pMOSFET,這些MOSFET皆由垂直堆疊、直徑僅8奈米的水平矽質奈米線製成。這些以矽質塊材基板製成、運用業界RMG製程的裝置,相較於鰭型FET的參考裝置,在性能水平上具備更優良的短通道特性(SS = 65 mV/dec, DIBL = 42 mV/V for LG = 24 nm)。

GAA裝置的結構能提供絕佳的靜電掌控能力,從而使極限CMOS裝置得以微縮。再者,水平奈米線是RMG FinFET的自然延伸,相比之下垂直奈米線會更需要顛覆性的技術性改變。更甚者,奈米線的堆疊能將每個覆蓋區的驅動電流最大化。IMEC將這三方面成功的結合於一,同時也是第一次展示微縮尺寸、垂直堆疊的水平矽質奈米線:直徑8nm、橫向間距45nm以及20nm的垂直距離。

和傳統的FinFET流程相比,IMEC做出了兩大改變。首先,為保留尖銳的矽-鍺/矽((SiGe)/Si)介面,在淺溝渠隔離(STI)的密實化步驟要在750°C的高溫下進行,這對良好控制下釋放奈米線十分必要。第二,為抑制底層寄生通道,IMEC便採用低複雜度的類接地參雜方案因應。

「IMEC已在實現sub-10nm技術節點的道路上有了突破性的進展,體現在微縮尺寸的奈米線堆疊上與固態靜電控制,同時將業界的RMG製程運用在矽質塊材基板上。」IMEC的邏輯裝置與積體電路總監Dan Mocuta表示:「後續的研究階段將會著重於達成更密的間隙上,並以此知識基礎,發展環繞式極匣橫向奈米線CMOS裝置。」

IMEC能夠成功研究出先進邏輯微縮的技術,有賴於core CMOS計畫的關鍵合作夥伴的一同努力。這些夥伴包含Global Foundries、Intel(因特爾)、Micron、SK Hynix、Samsung(三星)、TSMC(台積電)、Huawei(華為)、Qualcomm以及Sony(索尼)。

NMOS GAASiNWFET的穿透式電子顯微鏡影像(LG=70nm):(a)矽質奈米線陣列概覽 ; (b)兩條堆疊的奈米線其細節畫面

關於 imec

imec在奈米電子與光電領域進行世界領先級的研究。 imec善用資通訊科技(ICT)、醫療保健以及能源等全球各領域合作夥伴的創新能量,讓科學知識發揮更大效益。 imec提供產業相關的技術解決方案。在獨特的高科技環境中,我們頂尖的國際人才致力為永續社會打下更美好生活的基礎。 imec的總部位於比利時魯汶,並於比利時、荷蘭、台灣、美國、中國、印度以及日本等地設有辦公室。本公司旗下有超過2,500人的職員,包含將近740名的業界常駐人士以及客座研究人員。 imec於2015年的收入(損益)總額為4億1,500萬歐元。如需關於imec的進一步資訊,可參訪網站 www.imec.be。

本月熱點 HOME

- Microchip推出maXTouch® 觸控螢幕控制器

- 全新 NVIDIA RTX A400 和 A1000 GPU 增強人

- Imagination 推出全新Catapult CPU,加速

- 英飛凌推出全新 PSoC Edge 微控制器產

- 英飛凌推出經濟型低功耗長距離藍

- ROHM 6432尺寸金屬板分流電阻「PMR1

- Teledyne e2v獨特的5D圖像感測器可提供

- Microchip推出AVR® DU系列USB微控制器,

- 意法半導體推出高成本效益的無線

- CE-LINK推出尺寸小、功率大的革命性

- Microchip推出搭載硬體安全模組的P

- HPE Aruba Networking推出高容量Wi-Fi 7無